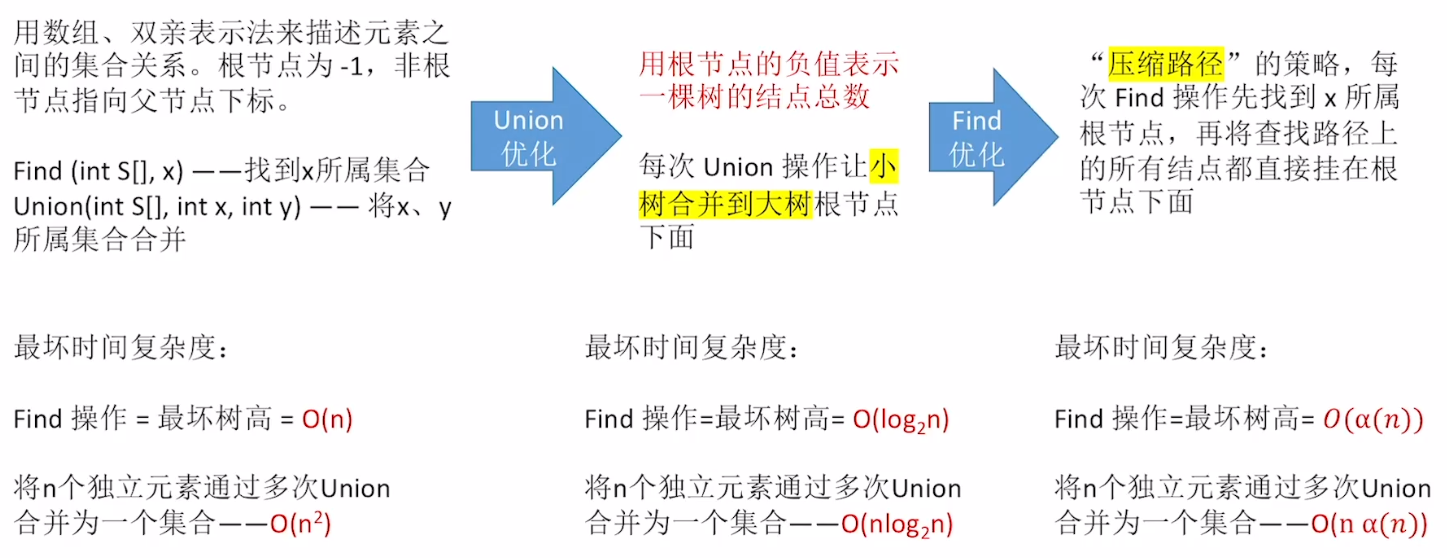

AC耦合电容,也叫DC blocking隔直电容,在几乎所有的高速串行链路中,都可以看到它的身影,它的主要作用是去掉信号中的直流偏置分量,同时让高频分量可以顺利通过,类似于一个高宽带的滤波器。

由于电容的焊盘通常都要比传输线的宽度要细,在电容这里会形成一个阻抗偏低点,提升这个阻抗,是电容仿真优化的重点。

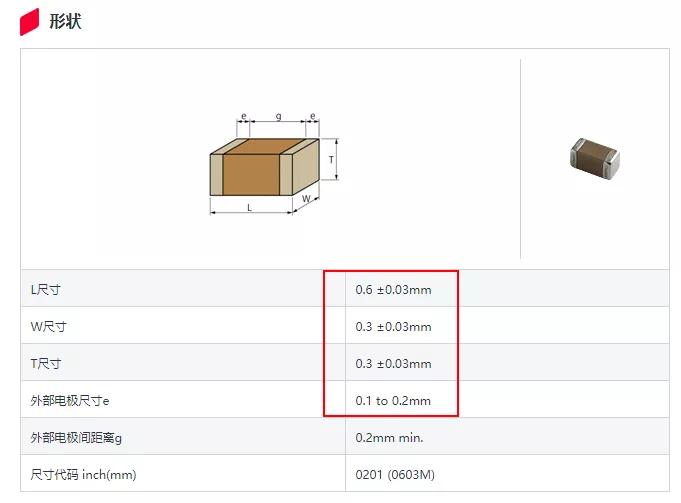

为了减小阻抗失配,会选用封装比较小的电容,目前高速PCB中,0201和01005封装的电容用的比较多,一般都是MLCC(Multi-layer Ceramic Capacitor )多层陶瓷电容,因为使用的是多层电极叠加结构,高频时电感非常低,具有非常低的等效串联电阻,损耗小。

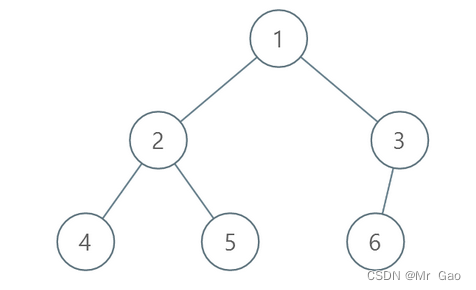

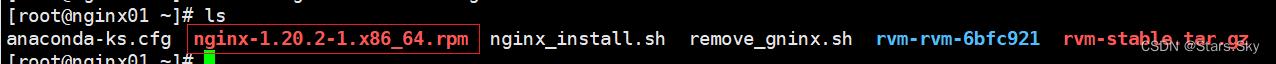

MLCC电容结构参考图一:两边是用来焊接的大电极,镀镍,镀锡,中间的陶瓷介质是钛酸钡,中间包裹着相互交错叠加的电极薄片,容值大小不同,电极的数量就不同。图二是0201封装电容尺寸,从村田官网截的图。

图一、陶瓷电容结构示意图

图二、0201电容封装尺寸

AC耦合电容仿真,如果能拿到具体的MLCC模型最好不过了,但是像陶瓷的介电常数、内部电极数量这些参数对厂家来说都是机密,一般人是没法拿到这些数据的,就算有这些尺寸,因为内部电极的厚度不过1~3um,这种薄片在HFSS中仿真,会划分非常多的网格数,耗费很多的CPU和内存资源,仿真时间很长,因此MLCC模型不太适合直接用来仿真。

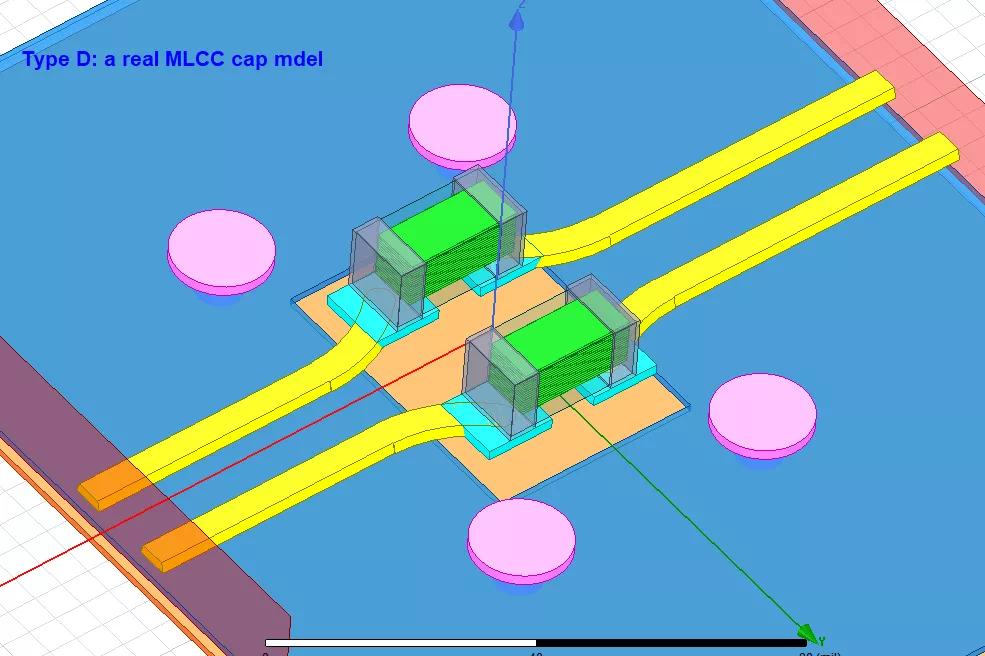

当然,这也并非绝对,samtec的大神就发表了关于用MLCC陶瓷电容仿真56Gbps和112Gbps PAM4的论文,有兴趣的可以去了解下文末的参考资料,但是对普通的仿真者来讲,技术难度还是比较大,图三是我根据论文建立的MLCC模型,因为仿真出来的SDD21曲线有很多谐振,就不过多分享了,毕竟结果不正确。

图三、真实的MLCC陶瓷电容仿真模型

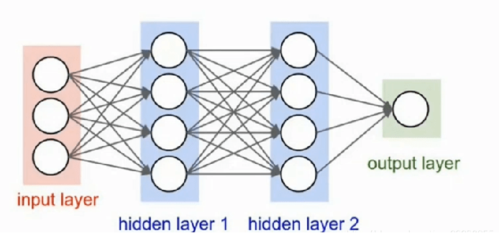

既然利用真实的MLCC模型仿真行不通,那么就得找到一些相对简单的模型来进行电容阻抗的优化。基于此模型,仿真出来的阻抗(TDR)应该与测试的TDR很接近,不然仿真模型也没有意义,凡是与测试结果差异很大的模型都无效,必须通过多次校准来完善模型。我自己建立的电容模型有6种,分别为:

-

第一、type A——就是一个金属块模型,见图四,它不是标准的0201封装尺寸,这个模型是我校准过的模型,近期的一些测试发现它的精度还不够,要继续完善;

图四、校准过的金属block电容模型

-

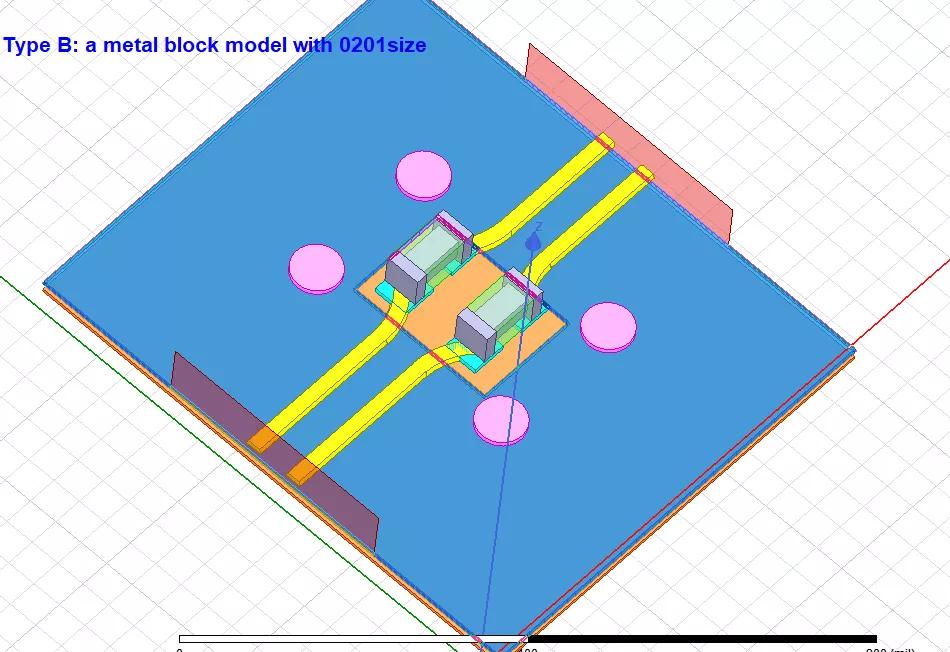

第二、type B——是一个标准0201封装尺寸的金属块模型,中间的block尺寸可调,需要基于实测TDR,见图五;

图五、0201封装尺寸金属block电容模型

-

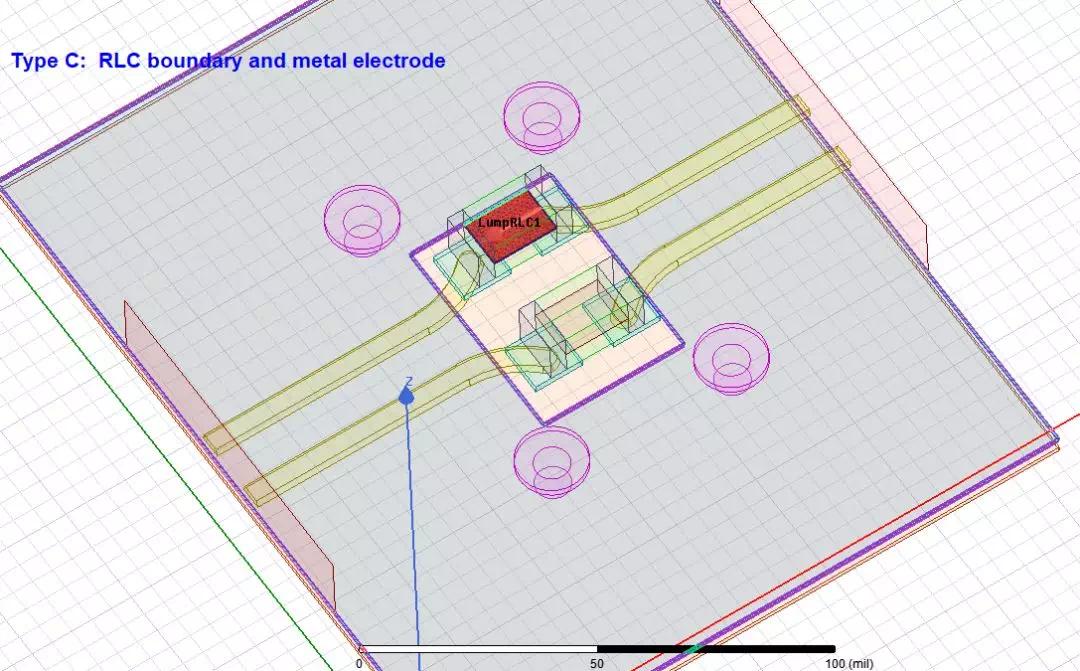

第三、type C——这个模型是HFSS help提到的一种,保留电容两边的金属电极,中间加了一个0.1uF电容边界条件,见图六;

图六、金属电极加RLC边界电容模型

点击完整阅读全文

AC耦合电容仿真知多少

![[附源码]Python计算机毕业设计高校课程思政案例库系统Django(程序+LW)](https://img-blog.csdnimg.cn/9efa4a1350264aec9c6a832ae0b7dc6c.png)

![[GYCTF2020]Easyphp](https://img-blog.csdnimg.cn/1c70c7eb42664e8183b89c16ffc31e7f.png)