提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

Xilinx DDR3学习总结——1、MIG核设置

- 前言

- 开发板 DDR信息

- MIG 设置

前言

话说之前从来没有使用过DDR,工作中的项目都是流式处理的,没有一个大存储的需求,应该图像处理中DDR用的会比较多一些,但是一个这么常用的东西不预先学习一下也不像话,在这里,也就记录一下学习的过程。参考其他优秀的博主的文章,现学现会。

开发板 DDR信息

开发板手册的介绍信息:

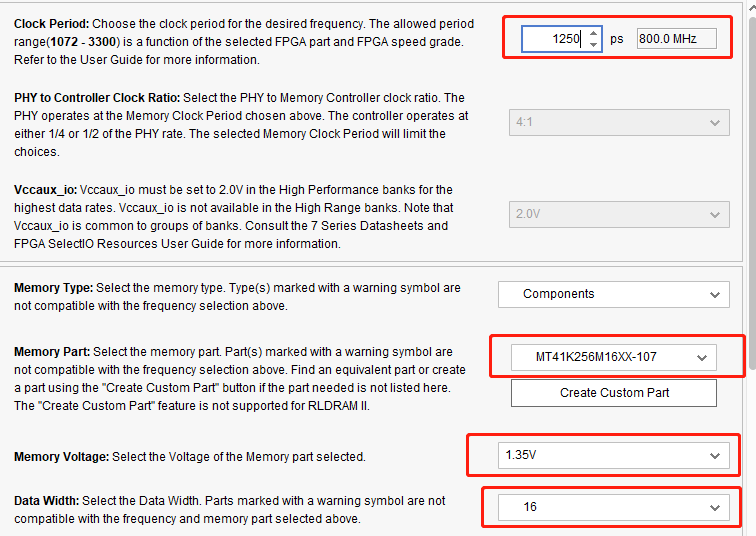

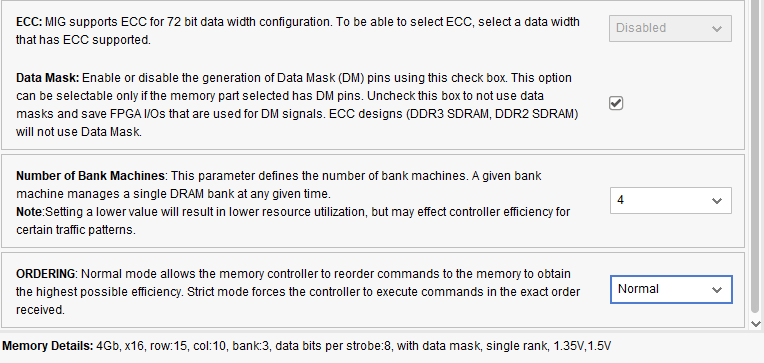

开发板上有4个DDR3颗粒,单片DDR内存大小是512MB,数据接口是16bit,四片DDR3内存共有2GB。内存数据主频高达1600MHZ,数据带宽可达1600MHz*64bit

DDR3型号:MT41K256M16TW-107

根据型号计算:256M*16bit = 512MB,容量没错

多片DDR连接时,地址引脚是完全一致的,不同的是数据位以及对应的数据标志的一些扩展 4片DDR3则DQ变成了64bit。

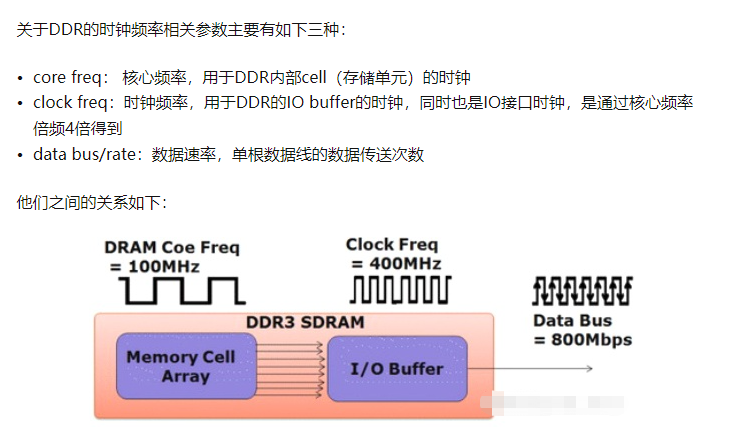

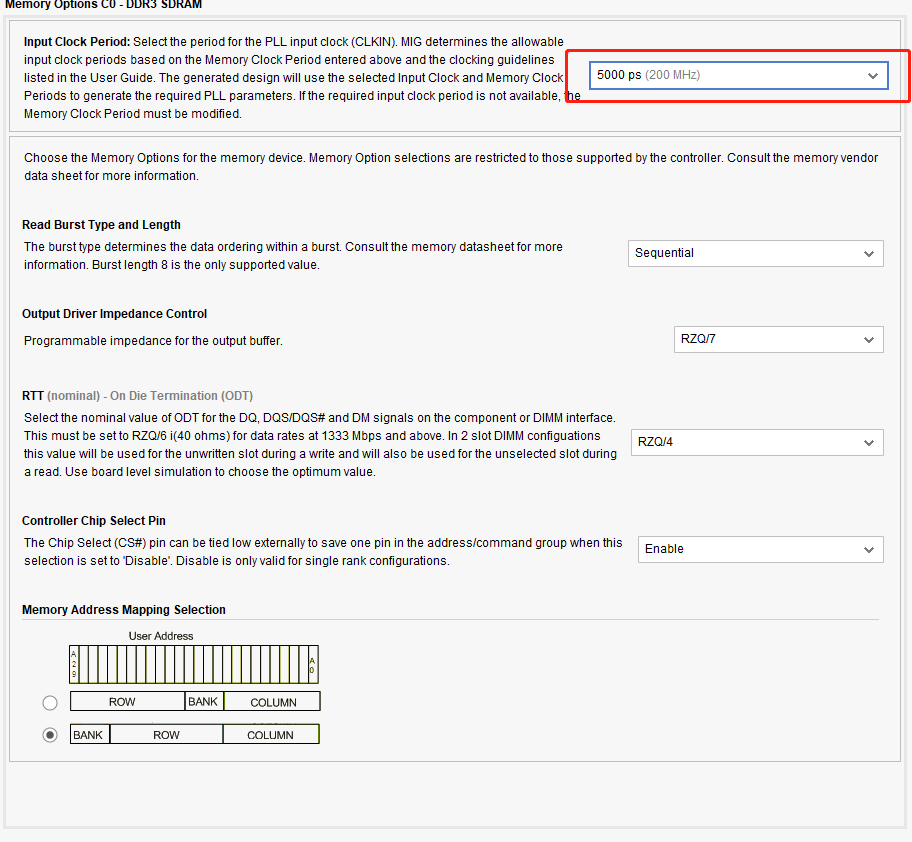

数据主频高达1600MHz,那么IO时钟(怎么描述呢?)为800MHz,时钟比为4:1,那么用户时钟是200MHz

MIG 设置

下面直接对MIG进行设置,虽然有4片DDR3,但还是从一片开始使用吧

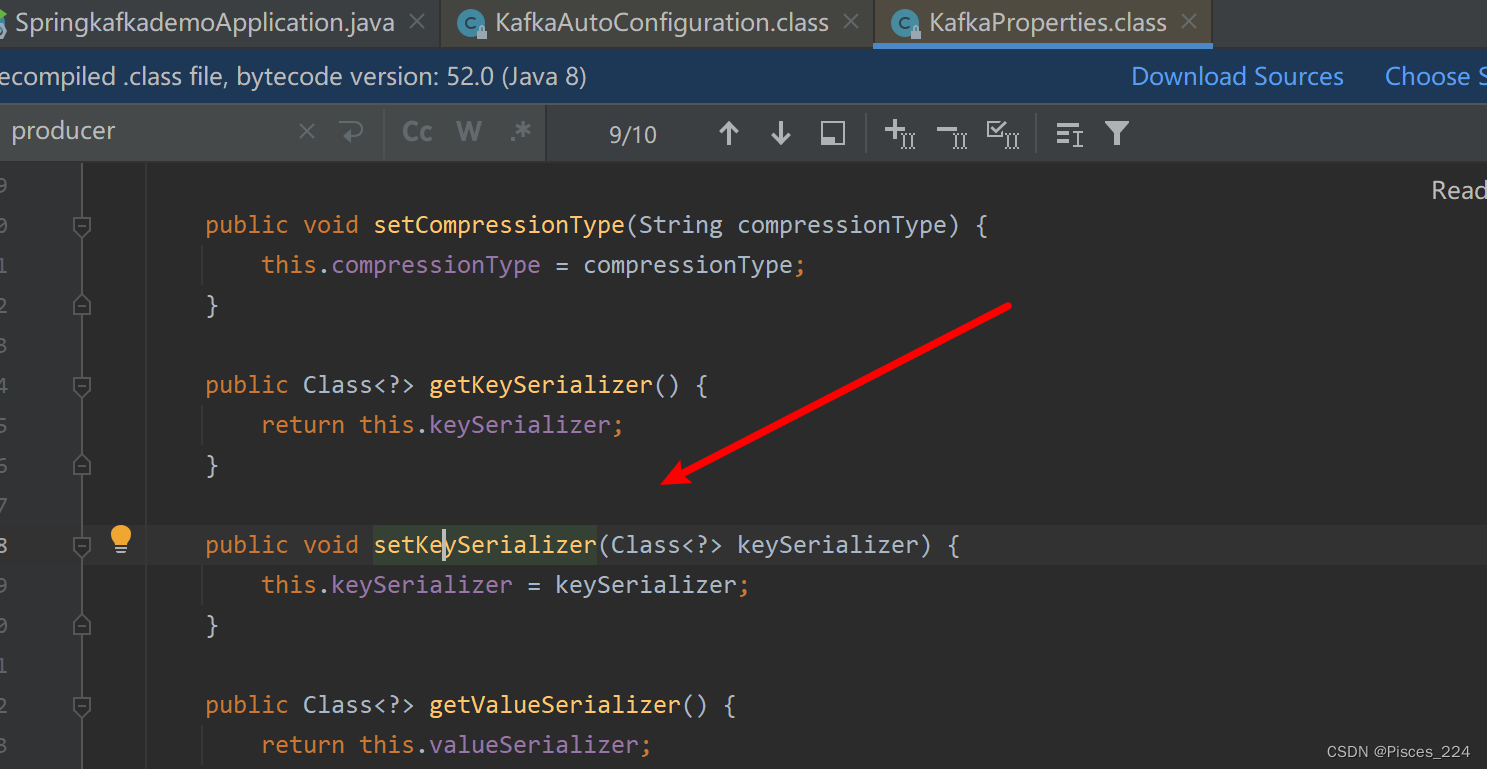

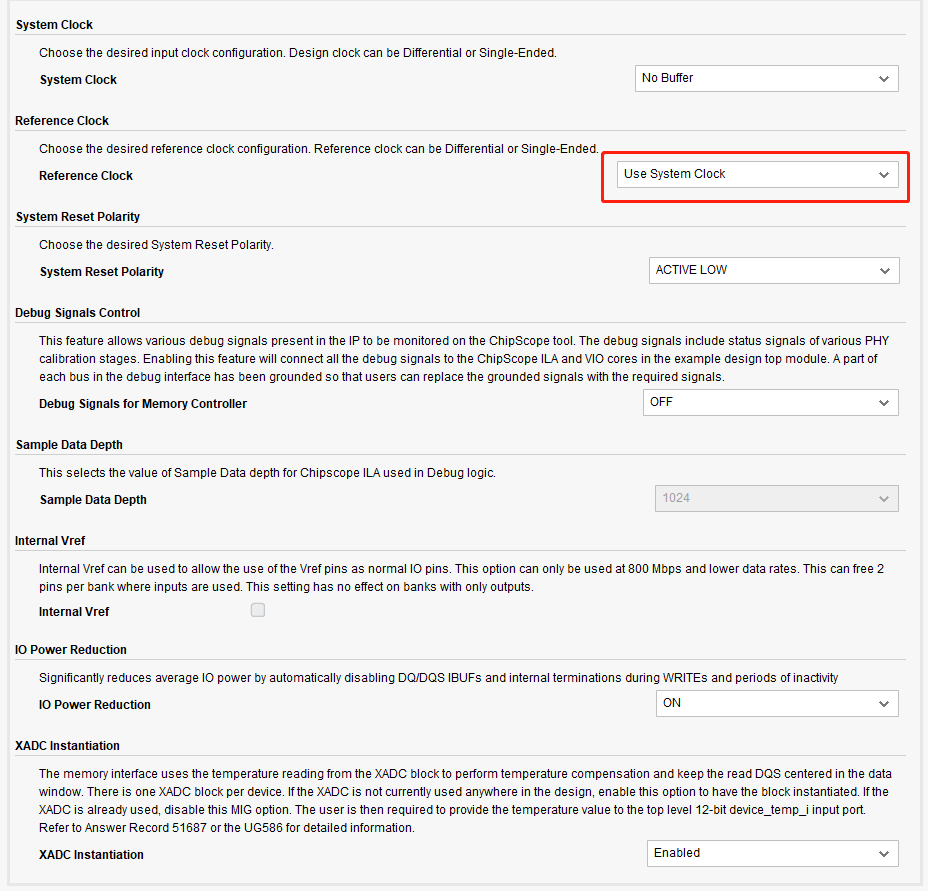

上面这个红色方框要注意,每次重新打开MIG IP的时候,这个值又会变成默认值。这个系统时钟经常使用200MHz,是因为除了这个时钟输入,还需输入一个参考时钟,参考时钟固定为200MHz,如果系统时钟时钟也是200MHz的,那么这两个时钟就可以合并为一个。

熟悉Xilinx IO Delay相关结构的都知道,需要对IO做微小延迟调整的时候,用的时钟就是200MHz

系统时钟使用200MHz的时候,上图的红色方框参考时钟可以与系统时钟是同一个端口

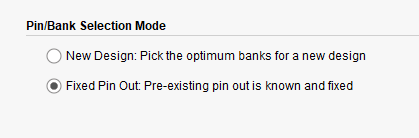

因为我们事先准备好了引脚定义,所以选择FIxed

然后读入UCF文件

NET "ddr3_addr[0]" LOC = "AC11" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[10]" LOC = "AJ11" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[11]" LOC = "AC10" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[12]" LOC = "AD8" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[13]" LOC = "AE11" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[14]" LOC = "AB8" | IOSTANDARD = SSTL135 |