Reduce Serial Loading Simulation Time with Sampling

使用write_patterns命令时,可以使用-sample开关保存完整pattern集的样本。这将减少pattern文件中的pattern数量,从而减少模拟时间。此外,-Sample开关允许您控制样本中包含的每种类型的pattern数量。通过改变样本pattern的数量,可以微调串行模式的文件大小和模拟时间之间的权衡。

使用并行加载执行初始验证后,可以使用采样pattern集模拟串行加载,直到满意测试覆盖率合理接近所需规范。然后,使用未采样pattern集执行一次系列加载模拟,作为最后一个验证步骤。

Test Pattern Data Support for IDDQ

为了获得最佳结果,如果在每个非扫描周期后都捕获到额外的IDDQ故障,则应测量电流。但是,您只能在测试模式序列中的特定位置测量电流,通常是在测试循环边界的末尾。为了确定何时可以进行IDDQ电流测量,pattern文件在适当的位置添加以下命令:

measure IDDQ ALL;

几种测试pattern数据格式支持IDDQ测试。TDL 91(德州仪器)、MITDL(三菱)、TSTL2(东芝)和FTDL _E(富士通)中有特殊的IDDQ测量结构。这些工具将这些构造添加到测试数据文件中。所有其他格式(WGL和Verilog)将这些声明表示为注释。

Basic Test Data Formats for Patterns

Text Format

这是运行write_patterns命令时工具生成的默认格式。除了WGL、STIL和二进制格式外,该工具还可以以这种格式进行读取。

此格式包含基于文本的并行格式的测试pattern数据以及pattern边界规范。主模式块调用适当的测试过程,而标头包含测试覆盖率统计信息和必要的环境变量设置。该格式还包含每个扫描测试过程,以及关于设计中每个扫描存储元件的信息。

要创建基本文本格式文件,请在应用程序命令行输入以下内容:

ANALYSIS> write_patterns filename -ascii

Comparing the Text Format with Other Test Data Formats

许多情况下,可能会发现将模拟或测试数据格式的内容与文本格式的内容进行比较以便于调试。本节提供了此任务所需的详细信息。

通常,测试集中的第一个周期执行某些任务。所有测试数据格式的第一个测试周期关闭所有时钟引脚上的时钟,驱动所有双向引脚上的Z,驱动所有其他输入引脚上的X,并禁用任何主输出引脚上的测量。

测试pattern

集可以包含两个主要部分:用于检测扫描链中故障的链测试块,以及用于检测其他系统故障的扫描测试或循环测试块。

The Chain Test Block

链测试应用test_setup过程,然后是加载扫描链的load_unload过程,然后再次应用load_unlead过程卸载扫描链。每个load_unload过程依次调用shift过程。此操作通常会将重复模式“0011”加载到链中。但是,如果存在少于四个单元的扫描链,则操作加载和卸载一个重复的“01”模式,然后加载一个重复“10”模式。此外,当组中的多个扫描链共享公共扫描输入引脚时,链测试过程分别加载和卸载具有重复pattern的每个扫描链,以顺序测试它们。

测试过程文件在指定时间应用测试过程中的每个事件。每个测试程序对应于一个或多个测试循环。每个测试程序可以有一个具有不同定时定义的测试周期。默认情况下,所有事件都使用1纳秒的时间刻度。

The Scan Test Block

pattern

集中的扫描测试块从应用test_setup过程开始。扫描测试块包含多个测试模式,每个测试模式通常应用加载卸载程序,强制主输入,测量主输出,并脉冲捕获时钟。

load_unload过程转换为一个或多个测试周期。模式中的force、测量和时钟脉冲事件转换为ATPG生成的捕获周期。每个事件在测试周期内都有一个序列号。序列号的默认时间刻度为1 ns。当前pattern的扫描链的卸载与下一pattern的扫描链条的加载同时发生。因此,测试集中的最后一个模式包含load_unload序列的额外应用程序。更复杂的扫描样式(例如,像LSSD)在模式中使用master_observe和skked_load过程。对于具有顺序控制器的设计,如边界扫描设计,每个测试过程中可能有几个测试周期来操作顺序扫描控制器。

一些pattern类型(例如,RAM顺序和时钟顺序类型)比基本pattern更复杂。RAM顺序pattern涉及扫描链的多个负载和RAM写入时钟的多个应用。时钟序列pattern涉及加载扫描链之后的多个捕获周期。另一种特殊类型的模式是clock_po模式。在这些模式中,时钟可以在整个测试周期中保持有效,而不应用捕获时钟。如果测试数据格式仅支持单个定时定义,则该工具无法在一个pattern集中同时保存clock_po和nonlock_po模式。这是因为tester不能再现一个满足两种pattern要求的时钟波形。每种模式类型(combinational、clock_po、ram_sequential和clock_sequentil)都可以有单独的时序定义。

General Considerations

在测试过程中,可能会留下许多未指定的引脚。未指定的主输入引脚保持其先前的状态。

所有测试数据格式都包含注释行,用于指示每个测试块和每个测试模式的开始。可以使用这些注释将文本格式的测试数据与其他测试数据格式相关联。

这些注释行还包含循环计数和循环计数,这有助于将测试器pattern数据与原始测试pattern数据相关联。循环计数表示测试循环的数量,换档顺序计数为一个循环。循环计数表示所有测试循环的数量,包括换档循环。如果tester有单独的扫描模式内存缓冲区,则循环计数很有用,否则循环计数更相关。

Binary

此格式包含二进制并行格式的测试模式数据,这是工具可以读取的唯一格式(文本格式除外)。以这种格式生成的文件包含与文本格式相同的信息,但使用的是压缩格式。您应该将这种格式用于存档目的,或者用于存储大型设计的中间结果。

要创建二进制格式文件,请输入以下命令:

ANALYSIS> write_patterns filename -binary

Verilog

该格式包含Verilog和Verifault模拟器可读的基于文本格式的测试模式数据和时序信息。该格式还支持扫描单元的串行和并行加载。Verilog格式支持所有Tessend Shell定时定义,因为Verilog刺激是一系列定时事件。

要生成基本Verilog格式的测试pattern文件,请在write_patterns命令中使用以下参数:

write_patterns filename [-Parallel | -Serial] -Verilog

Verilog模式文件包含应用测试模式、将预期输出与模拟输出进行比较以及打印包含失败比较信息的报告的步骤。

这些工具将所有模式和比较函数写入一个主文件(文件名),而将主要输出名称写入另一个文件(文件名称.po.name)。如果选择并行加载,它们还会将每个扫描链的每个扫描子链的扫描输出引脚的名称写入单独的文件中(例如,filename.thain1.name)。这允许工具报告预期输出和模拟输出之间存在差异的输出引脚。

Wave Generation Language (ASCII)

波形生成语言(WGL)格式包含基于结构化文本格式的测试模式数据和时序信息。可以将此格式转换为各种模拟和测试环境,但必须首先将其读入波形数据库并使用适当的转换器。此格式支持扫描单元的串行和并行加载。

一些测试数据流通过将WGL转换为激励和响应文件来验证pattern。有时,这种转换过程使用自己的并行加载方案,称为内存到内存映射,用于扫描模拟。在该方案中ATPG模型中的扫描存储元件必须与仿真模型中的相应存储元件具有相同的名称。由于这种并行加载方案的局限性,您应该确保:每个DFT库模型(也称为扫描子链)只有一个扫描单元,以及所有扫描单元的扫描输入和扫描输出引脚名称相同。要生成基本的WGL格式测试模式文件,请在write_patterns命令中使用以下参数:

write_patterns filename [-Parallel | -Serial] -Wgl

Standard Test Interface Language (STIL)

要生成STIL格式的测试pattern文件,请在write_patterns命令中使用以下参数:

write_patterns filename [-Parallel | -Serial] -STIL

ASIC Vendor Data Formats

ASIC供应商的测试数据格式包括 TDL 91、 FTDL-E、三菱MITDL和东芝TSTL2。ASIC供应商的芯片测试人员使用这些格式。

所有ASIC供应商数据格式都是基于文本的,并以并行方式将数据加载到扫描单元中。此外,ASIC供应商通常对模式定时施加若干限制。大多数ASIC供应商模式格式仅支持单个定时定义。

以下小节简要描述了ASIC供应商模式格式。

TI TDL 91

此格式包含基于文本格式的测试pattern数据。该工具支持TDL 91 3.0版和TDL 91 6.0版的功能。3.0版格式支持多个扫描链,但仅允许对所有测试周期进行单个定时定义。因此,所有测试周期必须使用主捕获周期的计时。TI的ASIC施加了额外的限制,即应始终在测试周期结束时进行比较。

要生成基本的TI TDL 91格式测试模式文件,请在write_patterns命令中使用以下参数:

write_patterns filename -TItdl

格式化程序将完整的测试数据写入文件名。它还将链测试写入另一个文件(filename.chain),以便在TI ASIC流期间单独使用。

Fujitsu FTDL-E

This此格式包含基于文本格式的测试pattern数据。FTDL-E格式将测试数据分为测量1或0值的pattern和测量Z值的pattern。测试pattern分为测试块,每个测试块包含64K测试仪循环。

To generate a basic FTDL-E format test pattern file, use the following arguments with the

write_patterns command:

write_patterns filename -Fjtdl

格式化程序将完整的测试数据写入名为filename.fjtdl.func的文件。如果测试模式集包含IDDQ测量值,格式化程序将在名为filename.ftjtl.DC的文件中创建单独的DC参数测试块。

Mitsubishi TDL

This format contains test pattern data in a text-based format.

To generate a basic Mitsubishi Test Description Language (TDL) format test pattern file, use

the following arguments with the write_patterns command:

write_patterns filename -MItdl

格式化程序以并行格式表示所有扫描数据。它将测试数据写入两个文件:

程序文件(filename.td0),其中包含所有引脚定义、定时定义和扫描链定义;以及测试数据文件(filename.td1),其中包含并行格式的实际测试矢量数据。

Toshiba TSTL2

此格式仅包含基于文本格式的测试pattern数据。测试pattern数据文件包含定时信息。此格式支持多个扫描链,但仅允许对所有测试周期进行单个定时定义。TSTL2以并行格式表示所有扫描数据。

要生成基本的Toshiba TSTL2格式测试模式文件,请在write_patterns命令中使用以下参数:

write_patterns filename -TSTL2

The formatter writes the complete test data to the file named

filename.

Vector Creation and Modification

Tessent工具提供了一种基于I/O端口或内部引脚状态的布尔操作在pattern集中操作Broadside矢量数据的方法,从而创建新的Broadside数据来保存。

这个新的Broadside矢量数据可能代表工具中不存在的被测设计的新的顶层层次结构。目前,这种操作仅限于Broadside pattern集(如IJTAG pattern集)或使用-串行开关写入的ATPG扫描pattern数据 ,创建Broadside向量时使用write_patterns命令。还可以从任何源创建宽边矢量数据,将数据传递给write_patterns命令,并让工具以pattern格式之一(包括test_setup和test_end过程数据(如果存在))写入矢量数据。当使用向量创建和修改时,术语模式和向量具有如下特定含义:

•pattern-pattern是测试刺激和响应的排列,旨在针对特定项目或故障进行测试。在ATPG中,一个pattern通常由一组扫描加载、一些启动和捕获刺激,然后一次扫描卸载组成。由于它存储在ATPG工具内部,因此pattern还不包含测试向量。也就是说,数据不能作为一组测试向量直接写入测试仪。

•矢量-矢量是一组在一个测试周期内发生的设备端口上的force和期望值。矢量可被处理并加载到测试仪存储器中,并应用于DUT。一组向量可以以表示ATPGpattern的方式进行分组,但pattern不一定由一组向量组成,直到通过write_patterns命令创建向量来表示该模式。

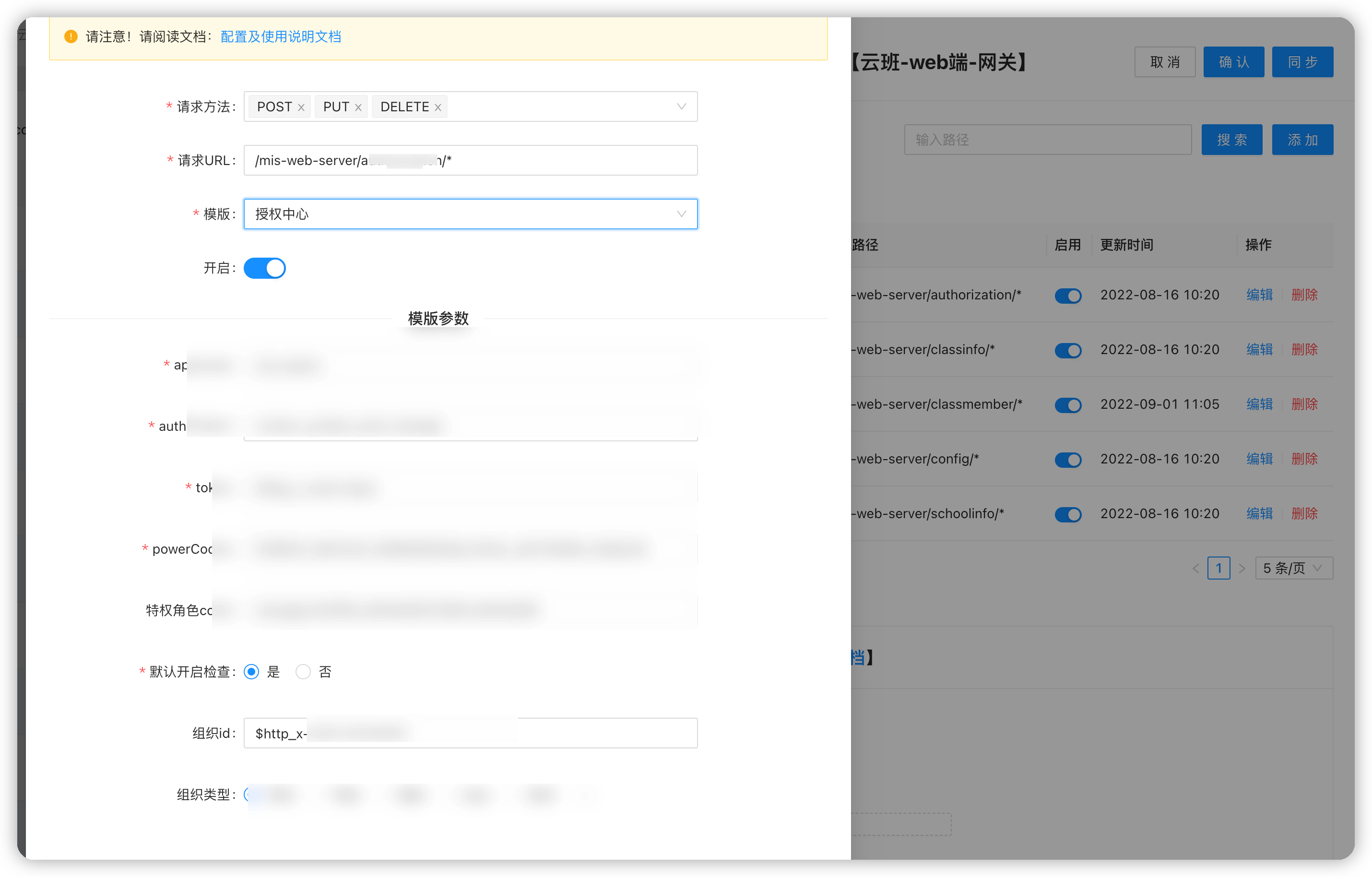

Port List Modification

可以修改用于保存Broadside矢量的端口列表。

创建和修改端口列表时使用以下命令:

•

get_write_patterns_options

•

report_write_patterns_options

•

set_write_patterns_options

这些命令可用于限制工具仅使用现有设计端口的子集来写入pattern,或用于添加加载到工具中的设计数据中不存在的其他顶级端口。无论端口列表如何修改,完整的端口集、force值和期望值仍将可用于传递给向量回调进程。

例如,Tcl向量回调过程可以使用Broadside向量中的一组完整的force和期望值来创建新的force和预期值,然后这些值只应用于端口子集。这些命令将能够创建一组要使用的端口,删除现有的端口,报告现有的端口集,并内省要使用的一组端口。

Vector Data Callbacks

使用回调过程,可以通过编程方式修改force 和期望来改变Broadside向量数据中的端口值。

Vector Data Callback Procs

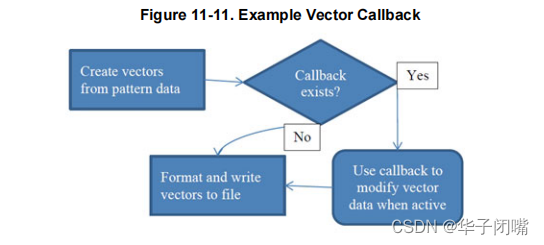

另一组命令选项用于启用可以应用于所有Broadside向量的Tcl回调过程。只能在写入串行扫描pattern或其他没有并行加载扫描数据的pattern集(如IJTAG模式)时使用此选项。这些回调

proc被插入到writepatterns命令的数据流中。write_patterns命令从工具的内部pattern存储中获取指定的pattern集,并对其进行处理或将其扩展为一组Broadside测试向量,一次一个pattern。然后写入正确的模式文件格式。回调在测试向量创建之后和写入之前插入到这个流中,允许在将它们写入pattern文件之前对其进行修改。在写入修改后的向量的过程中,write_patterns命令用N值向前填充任何输入端口,该值为该端口上先前向量的最后一个强制值。因此,如果回调进程在输入端口上放置了一个N,如果之前的任何向量在该端口上强制了一个已知值,那么它将被替换为一个已知的值(0或1)。如果该端口不是在过程中或被写入的模式集中的数据显式强制的,那么传递给回调进程的向量也可能在输入端口具有一个N值。Tcl procs可以在dofile中、在命令提示符下或从外部文件中定义。在使用命令将Tcl proc添加为向量回调proc之前,必须定义Tcl proc。

这些回调将从write_patterns命令中传递一个向量集,该向量集包含完整端口和管脚集或可选指定的端口和管头集上的强制值和预期值。回调将返回一个向量集,该向量集包含所有端口和管脚的新force和期望值,或可选指定的端口和管头的缩减集。回调还可以返回一个空向量集,或者一个包含多个向量的向量集,乘以传递给它的向量数。write_patterns命令将使用返回的向量当它将向量写入pattern文件时,用set代替传递的值。当回调返回一个空向量集时,这表示不会为传递给回调的向量写入向量。因此,回调可以从要写入的向量列表中删除向量。例如,到的Tcl回调看起来类似于以下内容:

proc myCallback { receivedVecSet } {

# code here to create returnedVecSet from receivedVecSet

return $returnedVecSet

}

回调过程将由Tcl interpreter以仅允许introspection commands

模式执行。

![[附源码]Node.js计算机毕业设计电子市场计算机配件报价系统Express](https://img-blog.csdnimg.cn/9c6e1954f5694beeb0fd624374ed6012.png)