SerDes详解

- 1 SerDes简介

- 1.1 并行总线接口

- 1.2 SerDes接口

- 1.3 SerDes的特点

- 2 发送均衡技术

1 SerDes简介

1.1 并行总线接口

在SerDes流行之前,芯片之间的互联时通过系统同步或者源同步的并行接口进行接口传输数据。

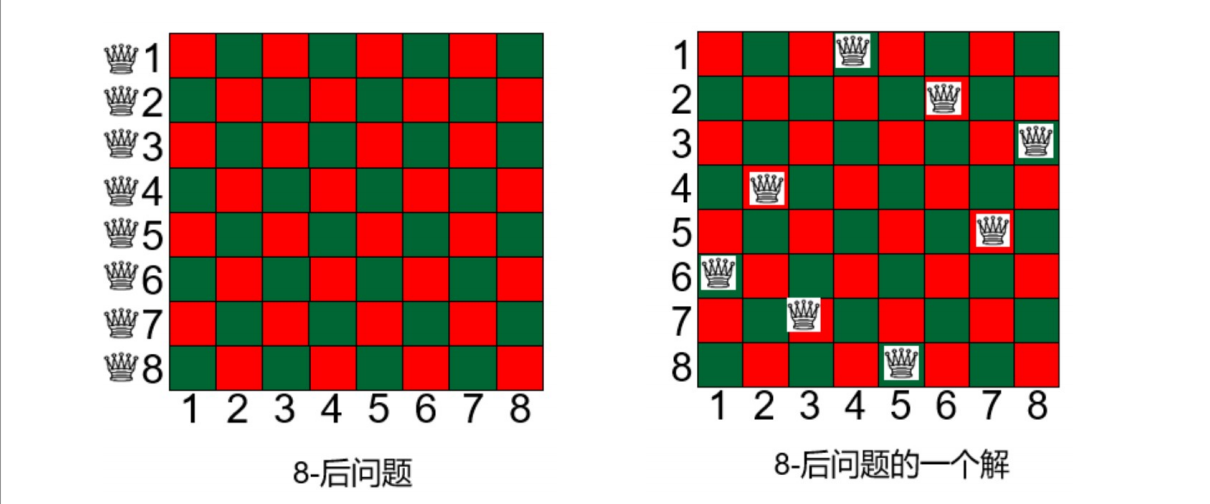

| 并行接口 | 定义 | 图片 |

|---|---|---|

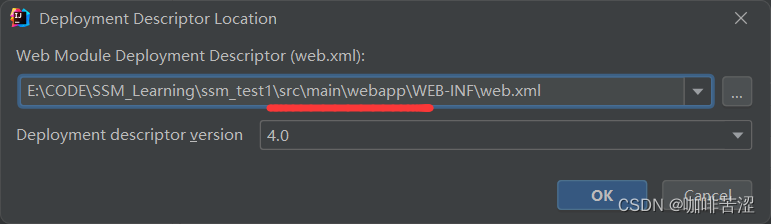

| 系统同步 | 发送端和接收端都是由系统时钟驱动的。 | ![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-ikYz2JbB-1670757544682)(硬件电路设计.assets/image-20221211175324111.png)]](https://img-blog.csdnimg.cn/1bbae0b08ada426d9b76f65725797dd0.png) |

| 源同步 | 是由发送端在发送数据的同时发送一个选通信号,接收端将这个选通信号作为接收时钟,控制信号的接收。理论上不受频率的限制,极大的提高的数据传输的速度。 |  |

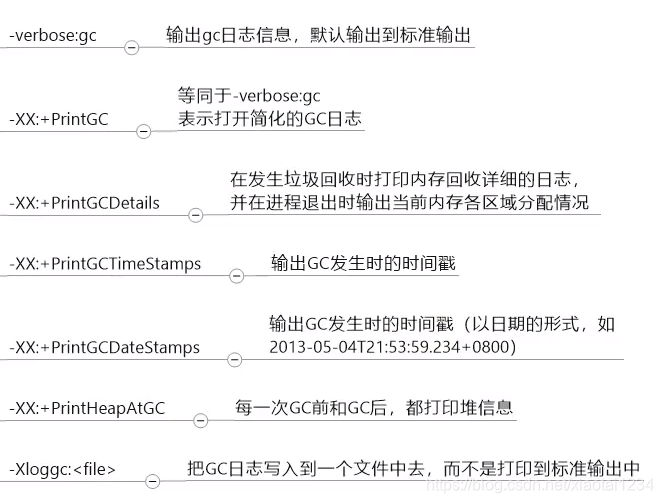

随着接口的频率的升高,在在并行接口中,以下几个因素限制了带宽的增加:

- 时钟达到两个芯片的传播时延不相等(clock skew)

- 并行数据各个bit的传播时延不相等(data skew)

- 时钟的传输时延与数据的传输时延不一致。

1.2 SerDes接口

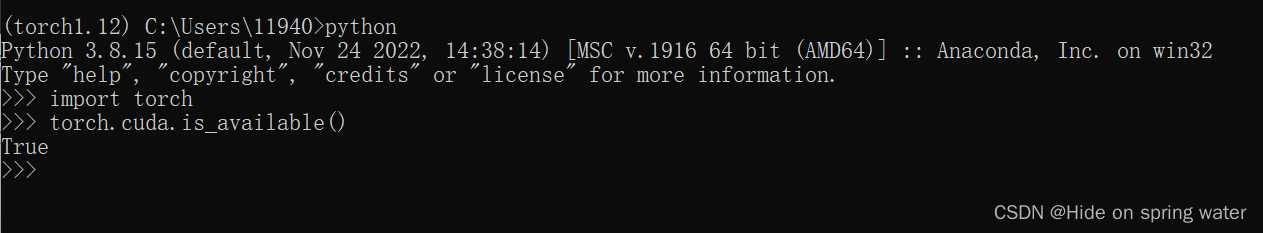

SerDes(Serializer-Deserializer)是串行器和解串器的简称。串行器(Serializer)也称为SerDes发送端(Tx),解串器(Deserializer)也成为SerDes接收端(Rx),一般通道数小于4。

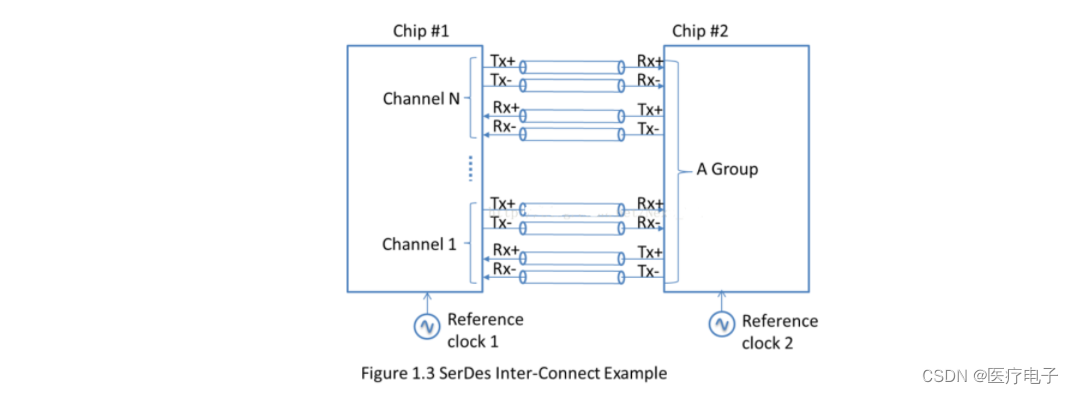

SerDes不传送时钟,这是SerDes的一个特点。SerDes在接收端集成了CDR(Clock Data Recovery)电路,利用CDR电路从数据的边沿信息中提取时钟信息,并找到最优的采样位置。SerDesc采用差分的方式传送数据,一般会有多个通道的数据放在一个group中以共享PLL资源,每个通道仍然是相互独立工作的。SerDes同样需要参考时钟(Reference Clock),一般也是差分形式,以降低噪声。接收端和发送的端的参考时钟可以允许有几百PPM的频差,也可以是同频的时钟,对视对于相位没有要求。

举例:一个SerDes通道使用4个引脚(Tx+/-,Rx+/-),FPGA的速率高达28Gbps,一个16bits的DDR3-1600的速率为1.6Gbps*16=25Gbps,却需要50个引脚。因此,SerDes在传输带宽上有明显的优势。

1.3 SerDes的特点

- SerDes在数据线中时钟内嵌,数据传输器件无需传输时钟时钟;

- SerDes通过加重/均衡奇数可以实现告诉长距离传输;

- SerDes占用较少的IO资源。

2 发送均衡技术

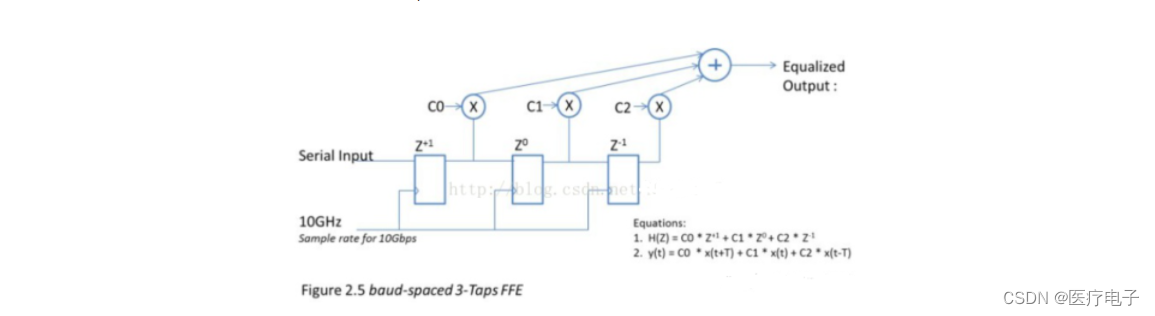

串行速率太高,必须使用均衡奇数来保证数据完整性。发送端均衡器设计为一个高通滤波器,目前是让达到接受测的信号为一个干净的信号,这就是前向反馈均衡(FFE,Feed Forward Equalization)。

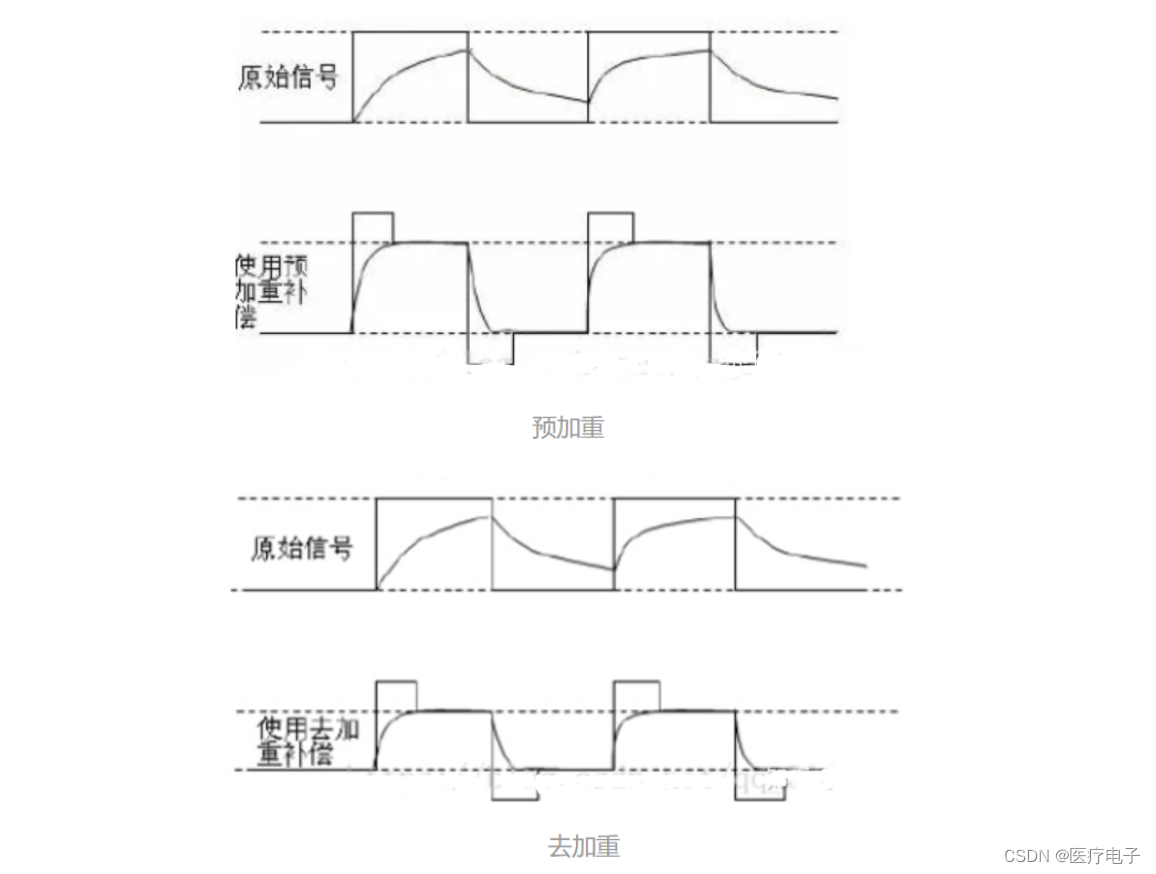

其实FFE 是一个比较偏数学或者说是频域的概念,具体到电路层次,从时域信号来看,一般又叫加重器(emphasis)。加重分为去加重(de-emphasis)和预加重(pre-emphasis)。De-emphasis 降低差分信号的摆幅(swing)。Pre-emphasis增加差分信号的摆幅。、由于目前芯片都需要追求降低功耗,所以大部分使用de-emphasis的方式,加重越强,信号的平均幅度会越小。

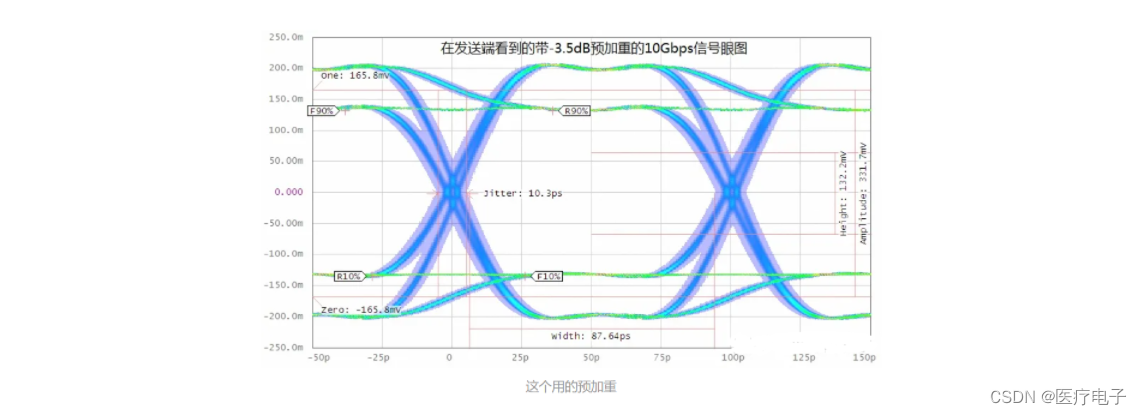

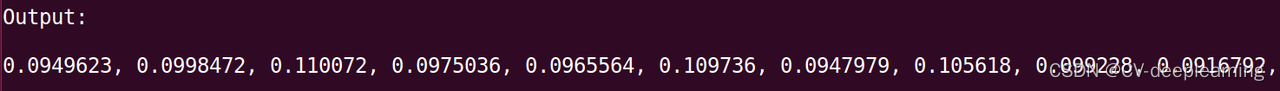

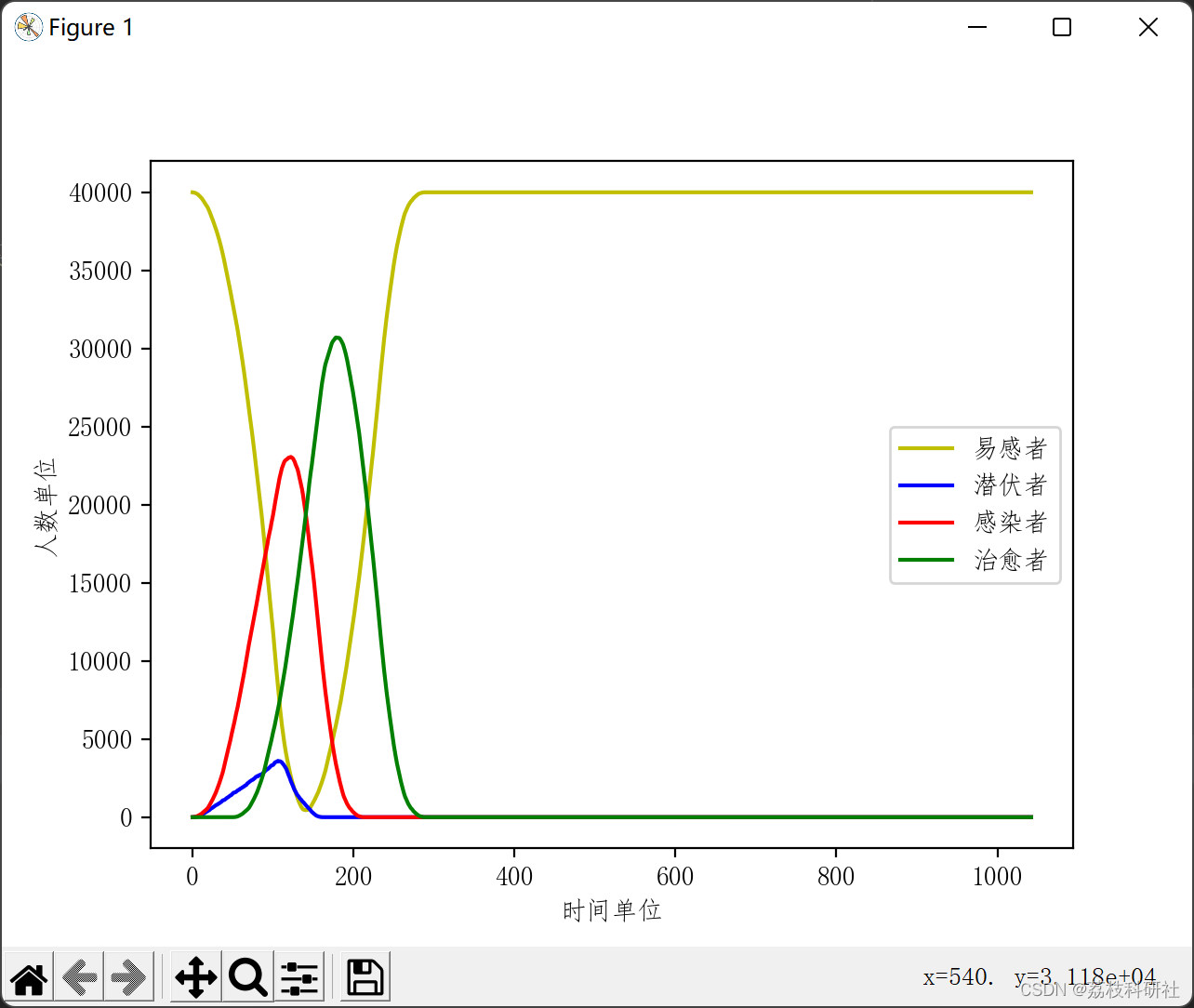

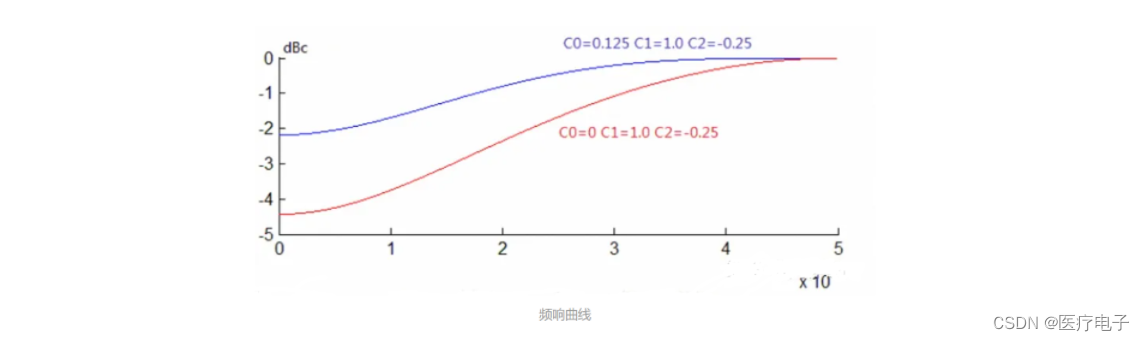

FFE相当于一个高通滤波器,调节滤波器的系数可以改变滤波器的频响,以补偿不同的信道特性,一般可以动态配置。以10Gbps线速率为例,图为FFE频率响应演示。可以看到,对于C0=0,C1=1.0,C2=-0.25的配置,5GHz处高频增益比低频区域高出4dB,从而补偿信道对高频频谱的衰减(高频衰减大)。

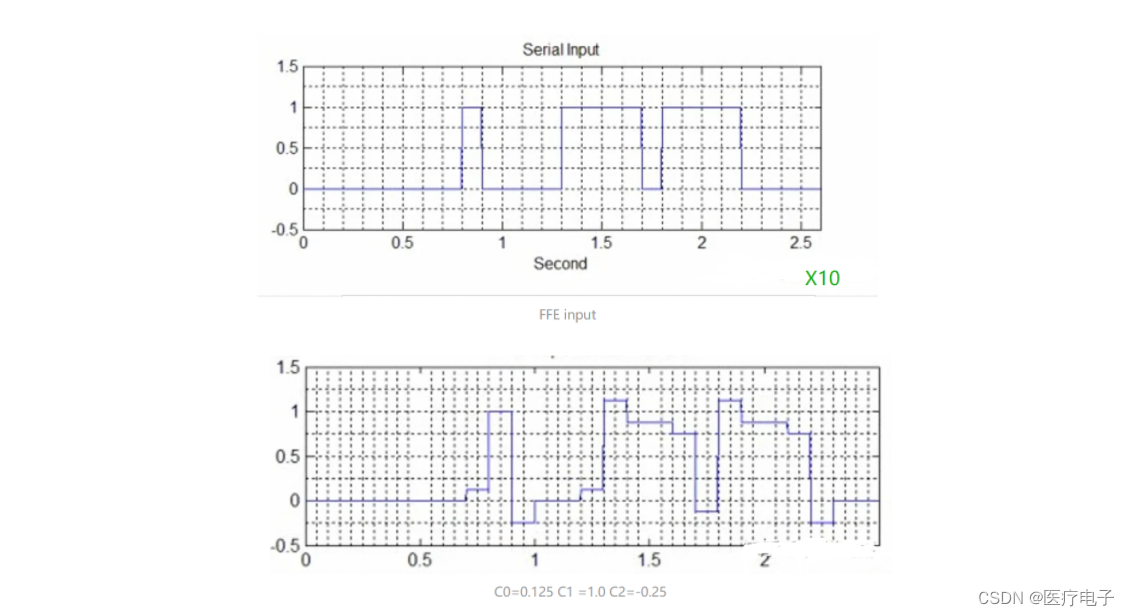

对于一个 0000 0000 1000 0111 1011 1100 00 的10Gbps速率信号,我们来看下他在3阶FFE的调整下是如何变化的。

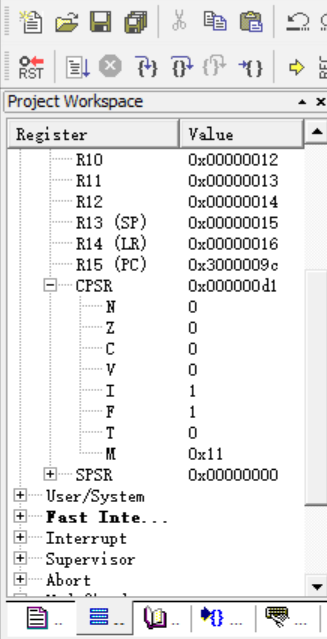

从图中可以看到,高频部分得到增强,低频部分压低,经过信道之后,可以想象接收端可能会是一个0.8左右的眼图(高频衰减多,低频衰减少)。所以,如果你拿高速示波器在发送端测试眼图,多数会一个翘的眼图: