微信公众号上线,搜索公众号小灰灰的FPGA,关注可获取相关源码,定期更新有关FPGA的项目以及开源项目源码,包括但不限于各类检测芯片驱动、低速接口驱动、高速接口驱动、数据信号处理、图像处理以及AXI总线等

二、AXI-Lite关键代码分析

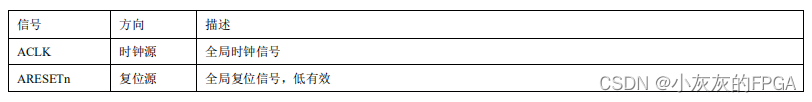

1、时钟与复位

需要注意的是:xilnx的axi的ip组件都是低复位有效;使用的开源的采用的是高复位有效

官方axi协议也采用的是低复位

2、写数据操作,对代码部分进行分析

写数据操作时候,使用三个通道,即写地址、写数据、写响应通道

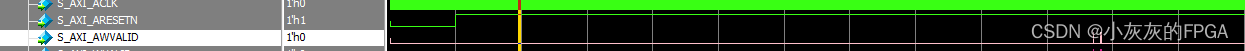

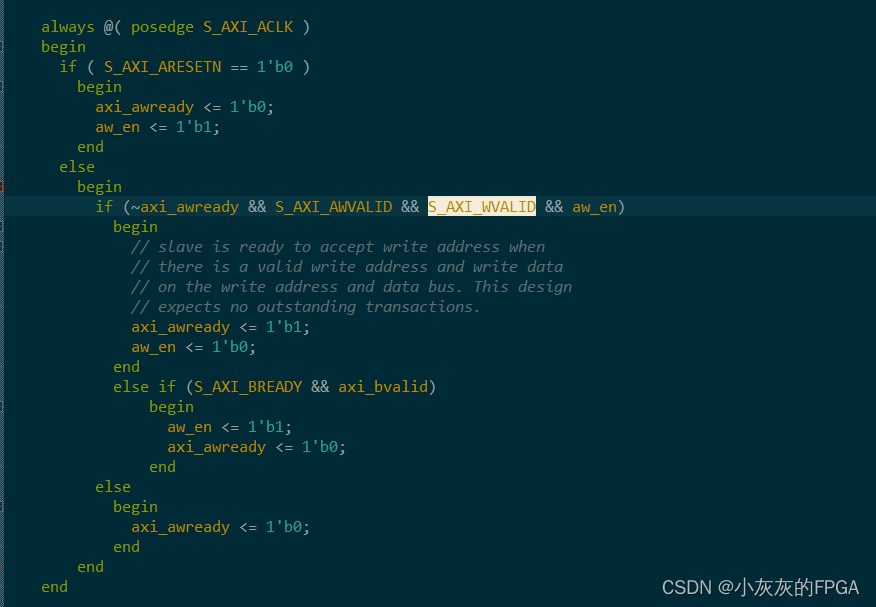

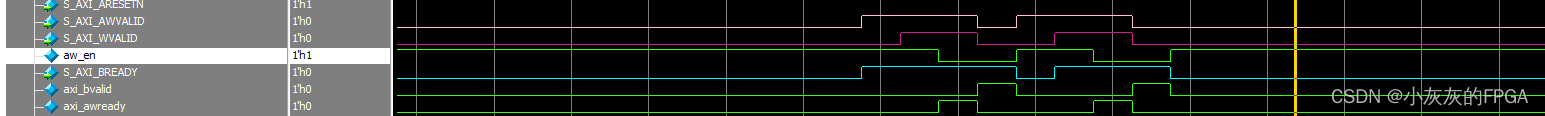

①写地址准备信号生成,当写地址通道有效信号(S_AXI_AWVALID1)&&写数据通道有效信号(S_AXI_WVALID1)&&(aw_en1)&&(axi_awready0)时候,在S_AXI_ACLK时钟上升沿,axi_awready跳变为高电平;在写响应通道准备信号和有效信号为高时,axi_awready跳变为低电平,其余条件为低电平

代码开发中实例如下:

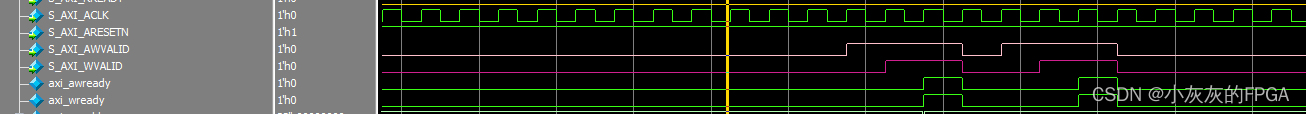

仿真时序图

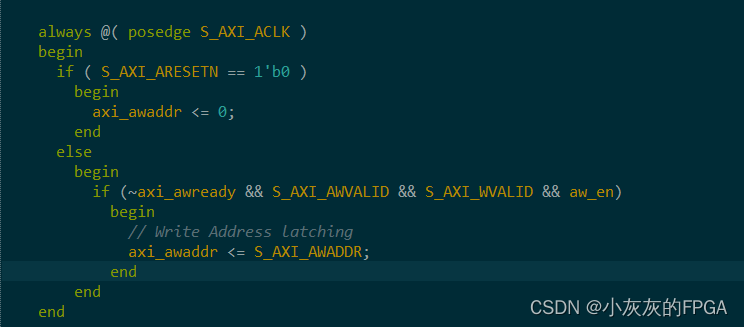

②写地址信号生成,当写地址通道有效信号(S_AXI_AWVALID1)&&写数据通道有效信号(S_AXI_WVALID1)&&(aw_en1)&&(axi_awready0)时候,在S_AXI_ACLK时钟上升沿锁存S_AXI_AWADDR

代码开发中实例如下:

仿真时序图

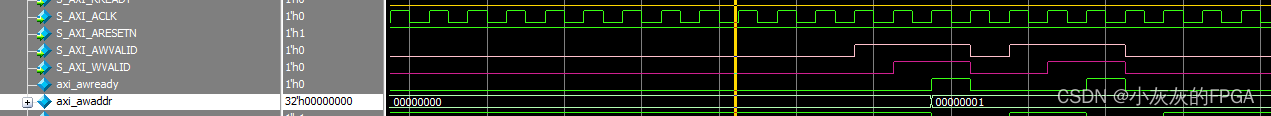

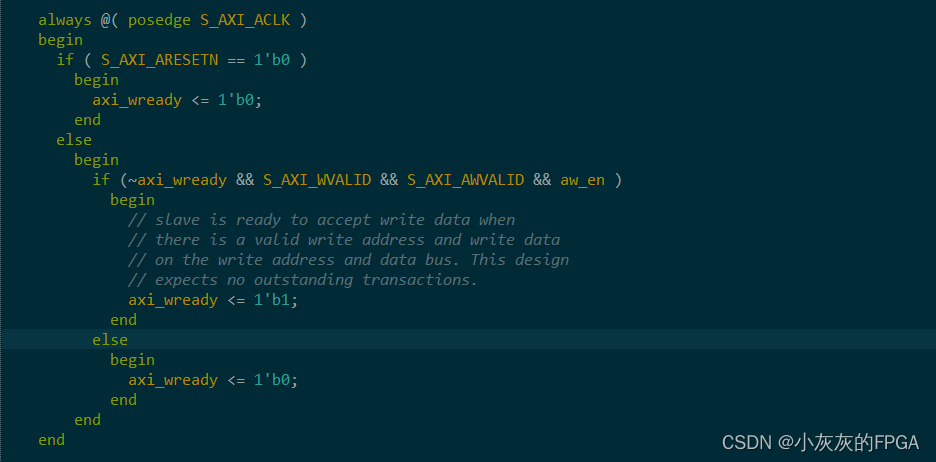

③写数据准备信号生成,当写地址通道有效信号(S_AXI_AWVALID1)&&写数据通道有效信号(S_AXI_WVALID1)&&(aw_en1)&&(axi_wready0)时候,在S_AXI_ACLK时钟上升沿,axi_wready跳变为高电平,其余条件为低电平

代码开发中实例如下:

仿真时序图

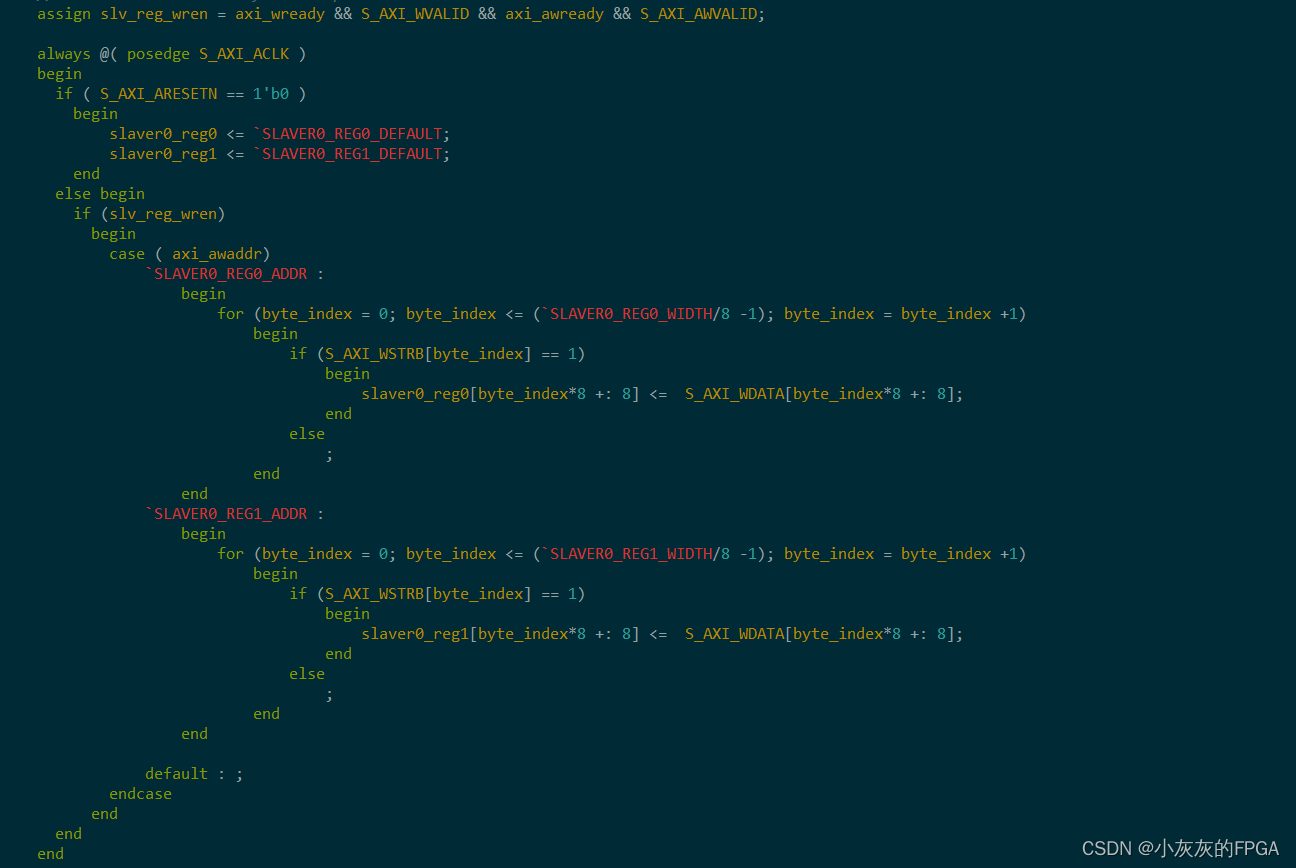

④写数据寄存器

配合SOC或者MPSOC的PS部分完成对外设或者寄存器的控制,比如GPIO的控制等。

在写地址通道有效、写地址通道准备信号ok以及写数据通道有效、写数据通道准备信号ok时,寄存器写使能slv_reg_wren才有效。

axi_awaddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB],即axi_awaddr[3:2],写通道地址的高两位。

[(byte_index*8) +: 8],byte_index = 0/1/2/3,对应[0:7],[8:15],[16:23],[24:31],对应32位数据。

代码开发中实例如下:

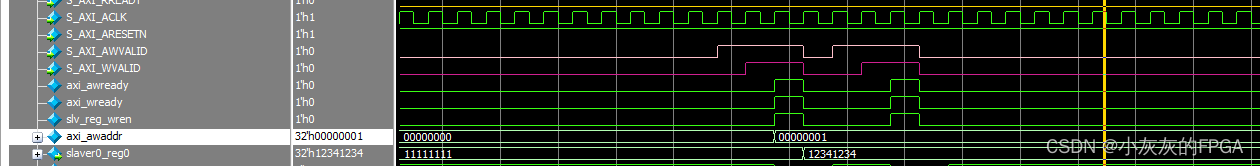

仿真时序图

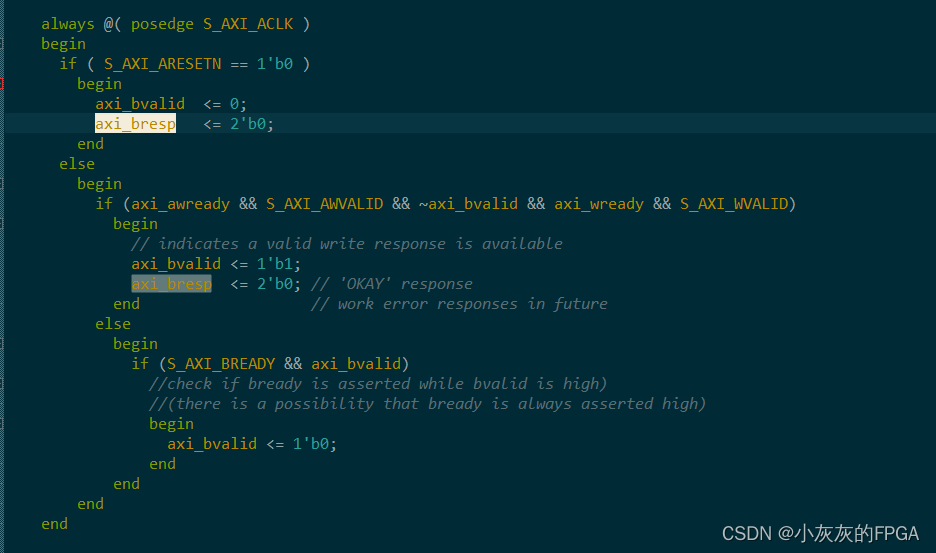

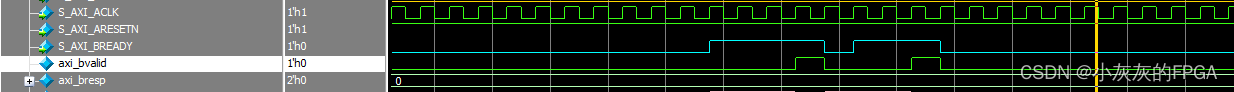

⑤写响应通道

axi_bavlid表示从机端数据已经接收完成

代码开发中实例如下:

仿真时序图

读数据操作时候,使用两个通道,即读地址、读数据通道

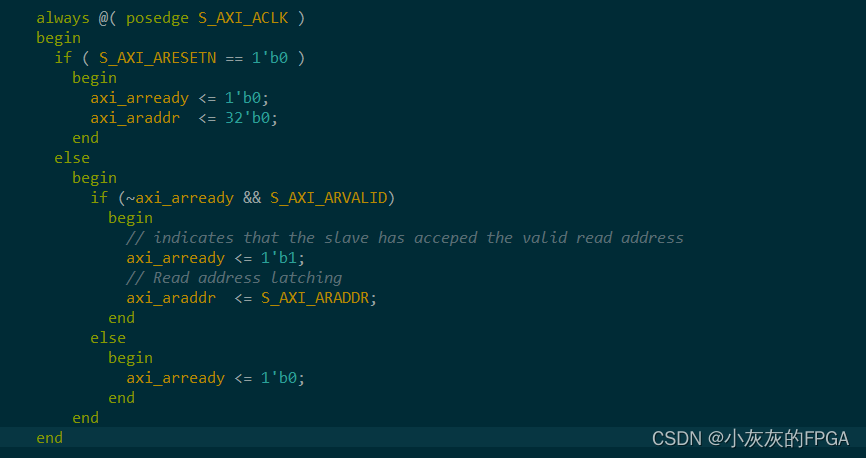

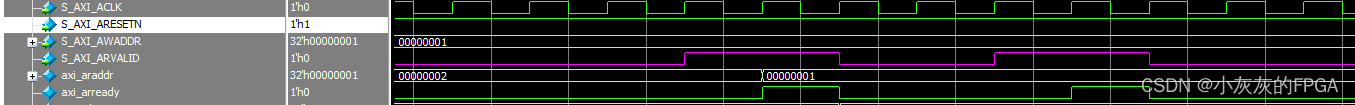

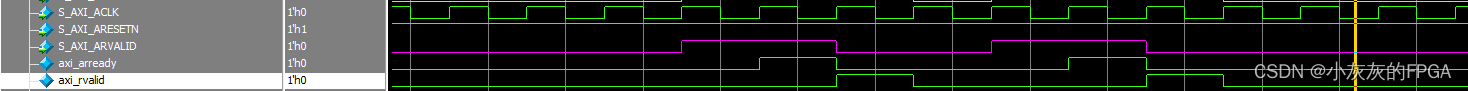

①读地址通道的axi_arready和axi_araddr

代码开发中实例如下:

仿真时序图

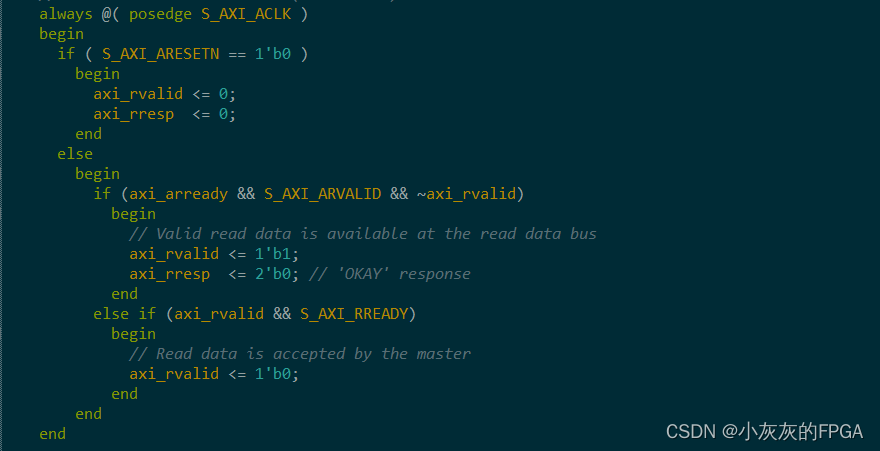

②读数据通道的axi_rvalid

代码开发中实例如下:

仿真时序图

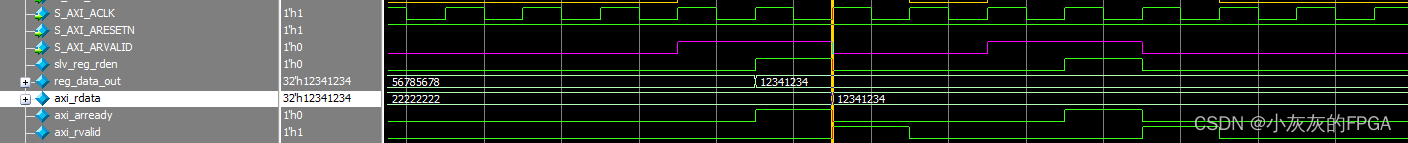

③读数据通道的寄存器读取

代码开发中实例如下:

仿真时序图

AXI协议之AXILite开发设计(二)

news2025/4/8 10:13:46

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/798386.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

Bootstrap框架(组件)

目录 前言一,组件1.1,字体图标1.2,下拉菜单组件1.2.1,基本下拉菜单1.2.2,按钮式下拉菜单 1.3,导航组件1.3.1,选项卡导航1.3.2,胶囊式导航1.3.3,自适应导航1.3.4ÿ…

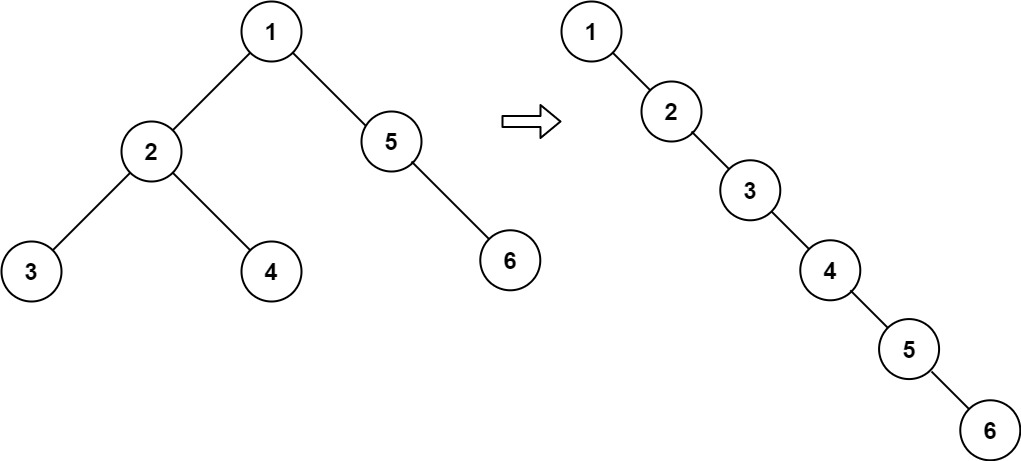

【LeetCode】114.二叉树展开为链表

题目

给你二叉树的根结点 root ,请你将它展开为一个单链表:

展开后的单链表应该同样使用 TreeNode ,其中 right 子指针指向链表中下一个结点,而左子指针始终为 null 。展开后的单链表应该与二叉树 先序遍历 顺序相同。

示例 1&…

【黑马头条之图片识别文字审核敏感词】

本笔记内容为黑马头条项目的图片识别文字审核敏感词部分

目录

一、需求分析

二、图片文字识别

三、Tess4j案例

四、管理敏感词和图片文字识别集成到文章审核 一、需求分析 产品经理召集开会,文章审核功能已经交付了,文章也能正常发布审核。对于上次…

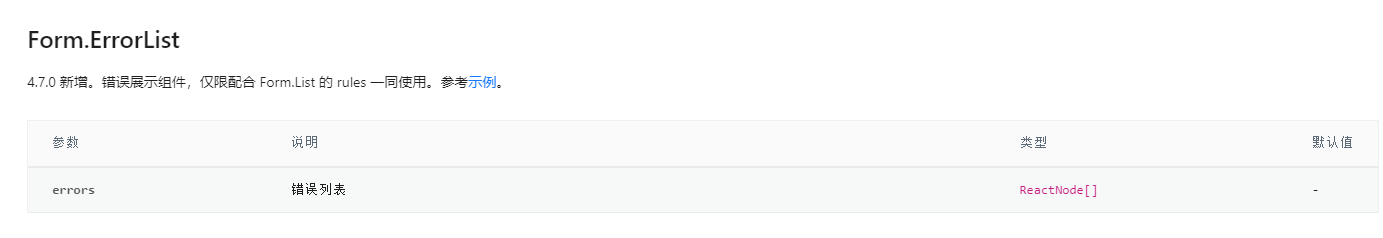

【已解决】React Antd Form.List 表单校验无飘红提示的问题

背景 我想对 Form.List 构建的表单进行校验,比如下拉框中的内容应当至少有一个 XX,表单的长度不能少于多少等等对 List 内容进行校验,并给出飘红提示

问题

比如我有这样一段代码来实现对 list 具体内容的校验,但是写完后发现没有…

专科程序员,想要面试获胜必须要做的两个点

这两天看到一篇关于专科程序员找工作的文章,感受到了其中的坎坷

那么作为专科程序员,我们应该如何获胜,获得工作机会呢?

根据我的经验,以下两点一定会给你带来更多的机会。

一个是学好英语

另外一个是构建自己的…

高层金属做power mesh如何避免via stack

随着工艺精进,pr要处理的层次也越来越多,如何选择power plan的层次尤为关键,一方面决定ir drop的大小,影响着芯片的功能,一方面决定绕线资源,影响面积。

选择高层metal做power mesh的关键在于厚金属&#…

微信小程序开发之配置菜单跳转到自定义页面

需求:

用户点击公众号菜单跳转到自定义带引流码的链接

公众号相关文档:

网页授权 | 微信开放文档 大致流程:

1.在公众号菜单配置链接:

https://open.weixin.qq.com/connect/oauth2/authorize?appidXXXXXXXXXXXX&redirect_urihttps%3A%2F%2F测试域名%2Fws_dabai%2Fwe…

i.MX6ULL(二十) linux platform 设备驱动

Linux 系统要考虑到驱动的可重用性,因 此提出了驱动的分离与分层这样的软件思路,在这个思路下诞生了我们将来最常打交道的 platform 设备驱动,也叫做平台设备驱动。 1 Linux 驱动的分离与分层 1.1 驱动的分隔与分离 对于 Linux 这样一…

查看电脑上NET Framework最高版本

1、使用CMD工具

1、进入路径:

cd %WINDIR%\Microsoft.NET\Framework\v4.0.303192、查看版本

MSBuild /version2、效果

【Github】自动监测 SSL 证书过期的轻量级监控方案 - Domain Admin

在现代的企业网络中,网站安全和可靠性是至关重要的。一个不注意的SSL证书过期可能导致网站出现问题,给公司业务带来严重的影响。针对这个问题,手动检测每个域名和机器的证书状态需要花费大量的时间和精力。为了解决这个问题,我想向…

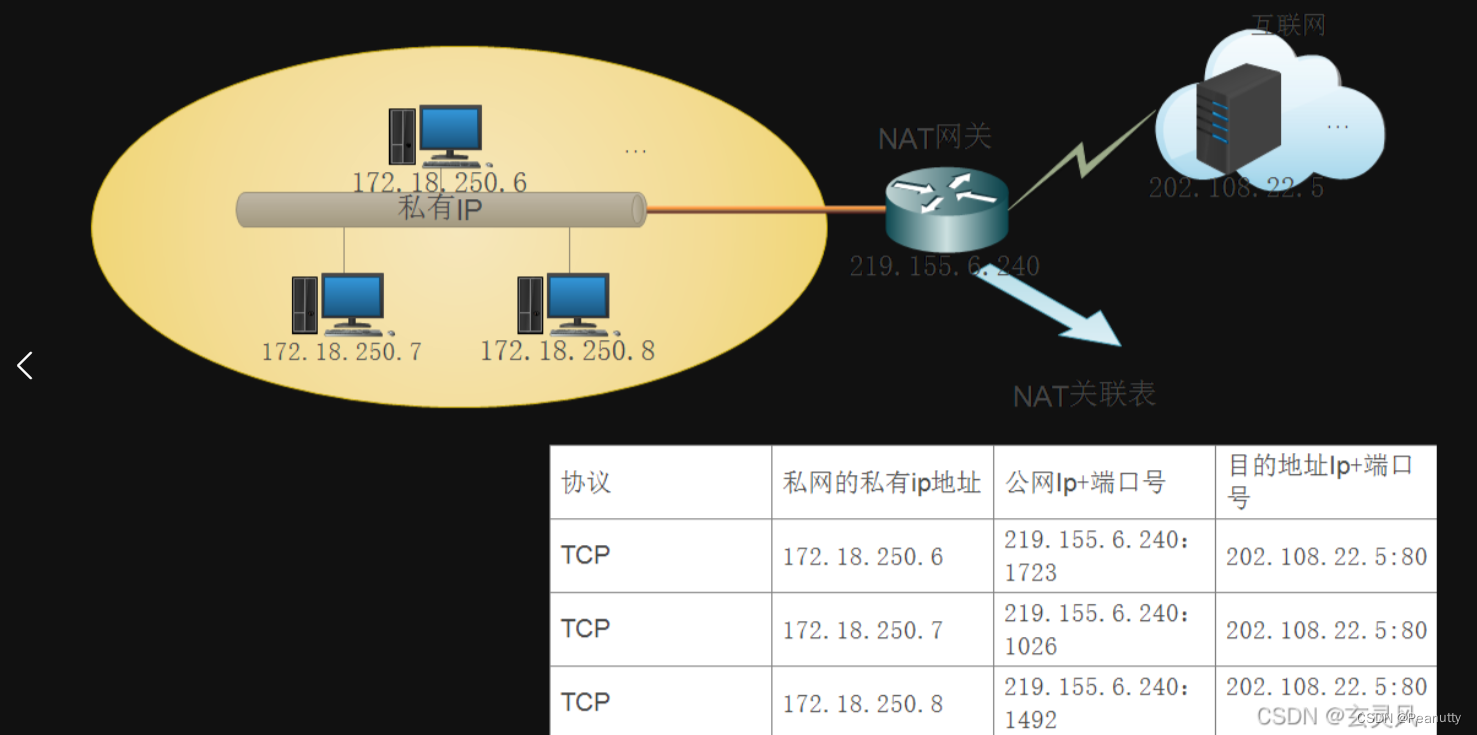

NAT详解(网络地址转换)

一句话说清楚它是干什么的:

网络地址转换:是指通过专用网络地址转换为公用地址,从而对外隐藏内部管理的IP地址,它使得整个专用网只需要一个全球IP就可以访问互联网,由于专用网IP地址是可以重用的,所以NAT大…

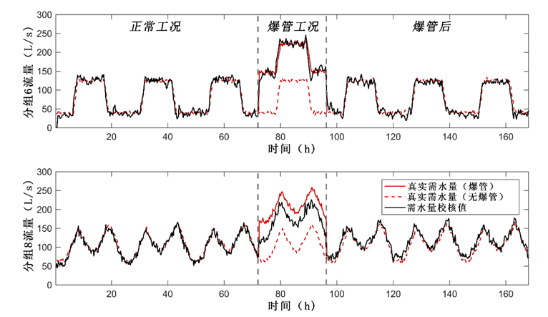

基于机器学习的供水管网水力模型

大数据、人工智能、物联网等前沿技术正推动人类社会发展发生深刻变革。2021年12月12日,国务院印发了《“十四五”数字经济发展规划》,进一步指明了各行业数字化转型发展的方向。作为传统的民生保障行业,供水行业也面临着向数字化智慧化转型的…

2023年的前端开发还好找工作么

首先可以明确写在前面的是,前端的确是不像之前一样,只会简单的基础就能轻轻松松的找到工作的,随着学习的人不断增多,市场自然会逐步提高对就业人员的要求,那么再以之前的要求来看待前端的话的确是不可取的

互联网在&a…

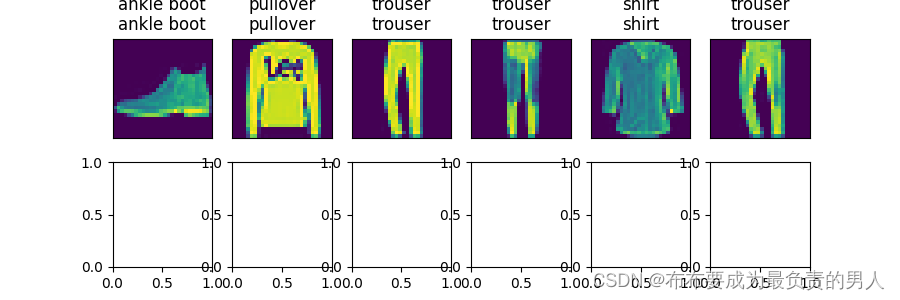

机器学习深度学习——多层感知机的从零开始实现

👨🎓作者简介:一位即将上大四,正专攻机器学习的保研er 🌌上期文章:机器学习&&深度学习——多层感知机 📚订阅专栏:机器学习&&深度学习 希望文章对你们有所帮助 为…

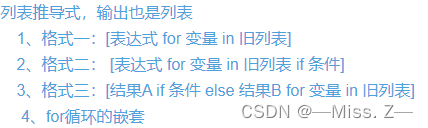

计算机二级Python基本操作题-序号41

1. 输入字符串s,按要求把s输出到屏幕,格式要求:宽度为30个字符,星号字符*填充,居中对齐。如果输入字符串超过30位,则全部输出。 例如:键盘输入字符串s为"Congratulations”,屏幕…

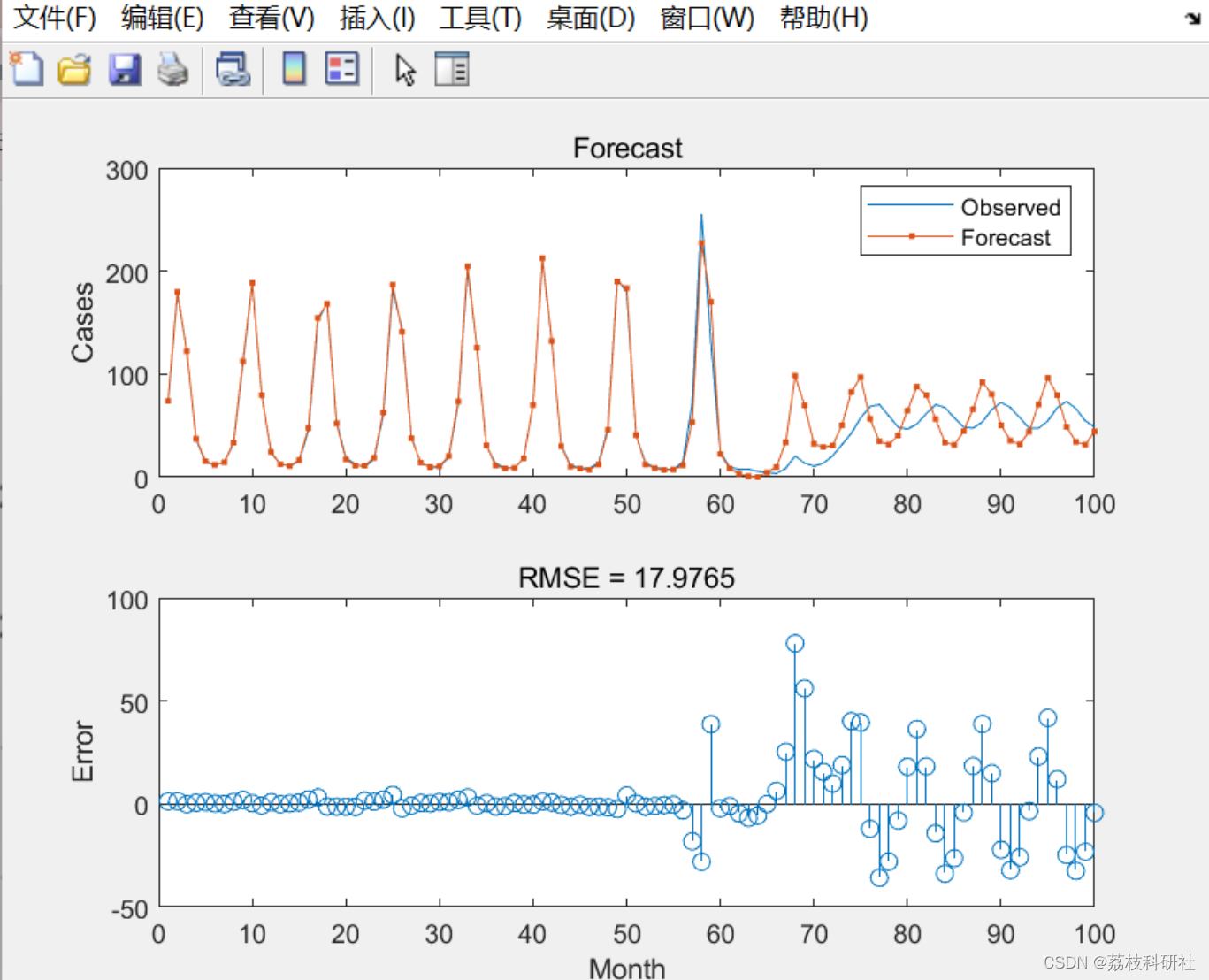

基于Kaggle训练集预测的多层人工神经网络的能源消耗的时间序列预测(Matlab代码实现)

目录 💥1 概述 📚2 运行结果 🌈3 Matlab代码实现 🎉4 参考文献 💥1 概述

本文为能源消耗的时间序列预测,在Matlab中实现。该预测采用多层人工神经网络,基于Kaggle训练集预测未来能源消耗。 &am…

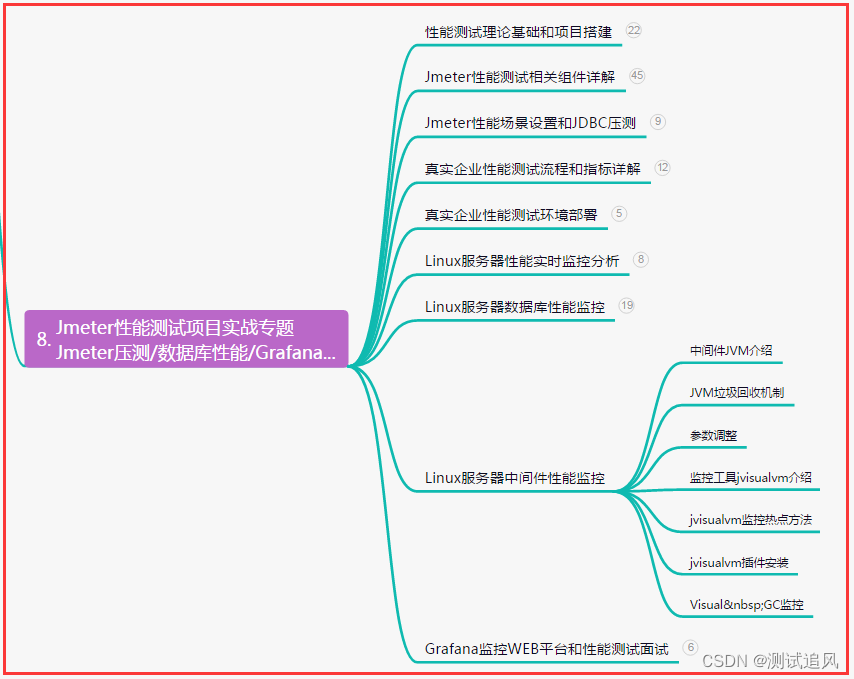

自动化测试如何做?分层自动化测试如何实施?一篇概全...

目录:导读 前言一、Python编程入门到精通二、接口自动化项目实战三、Web自动化项目实战四、App自动化项目实战五、一线大厂简历六、测试开发DevOps体系七、常用自动化测试工具八、JMeter性能测试九、总结(尾部小惊喜) 前言

分层的自动化测试…

【Spring Cloud Alibaba】限流--Sentinel

文章目录 概述一、Sentinel 是啥?二、Sentinel 的生态环境三、Sentinel 核心概念3.1、资源3.2、规则 四、Sentinel 限流4.1、单机限流4.1.1、引入依赖4.1.2、定义限流规则4.1.3、定义限流资源4.1.4、运行结果 4.2、控制台限流4.2.1、客户端接入控制台4.2.2、引入依赖…

(双指针) 剑指 Offer 57. 和为s的两个数字 ——【Leetcode每日一题】

❓ 剑指 Offer 57. 和为s的两个数字

难度:简单

输入一个递增排序的数组和一个数字 s,在数组中查找两个数,使得它们的和正好是 s。如果有多对数字的和等于 s,则输出任意一对即可。

示例 1: 输入:nums [2…