一、实验目的

1:了解双端口静态存储器IDT7132的工作特性及使用方法。

2:了解半导体存储器如何读写。

二、实验总结

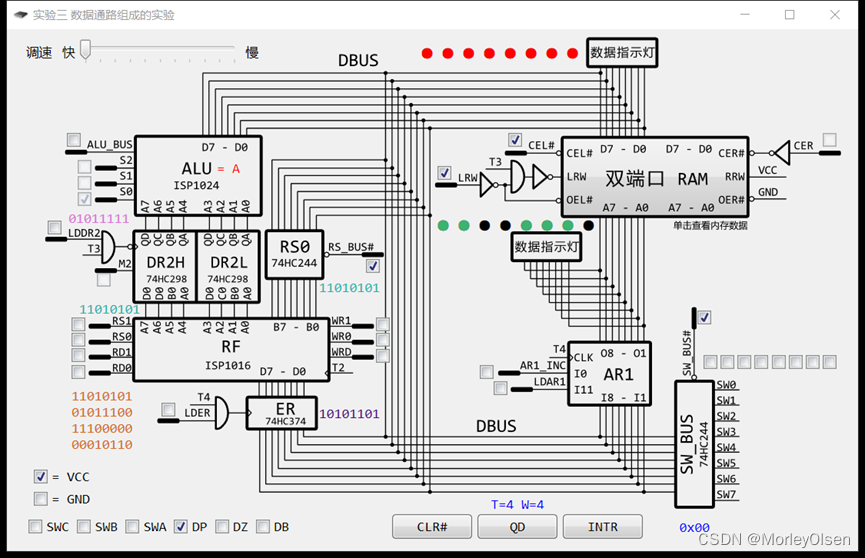

0:实验内容

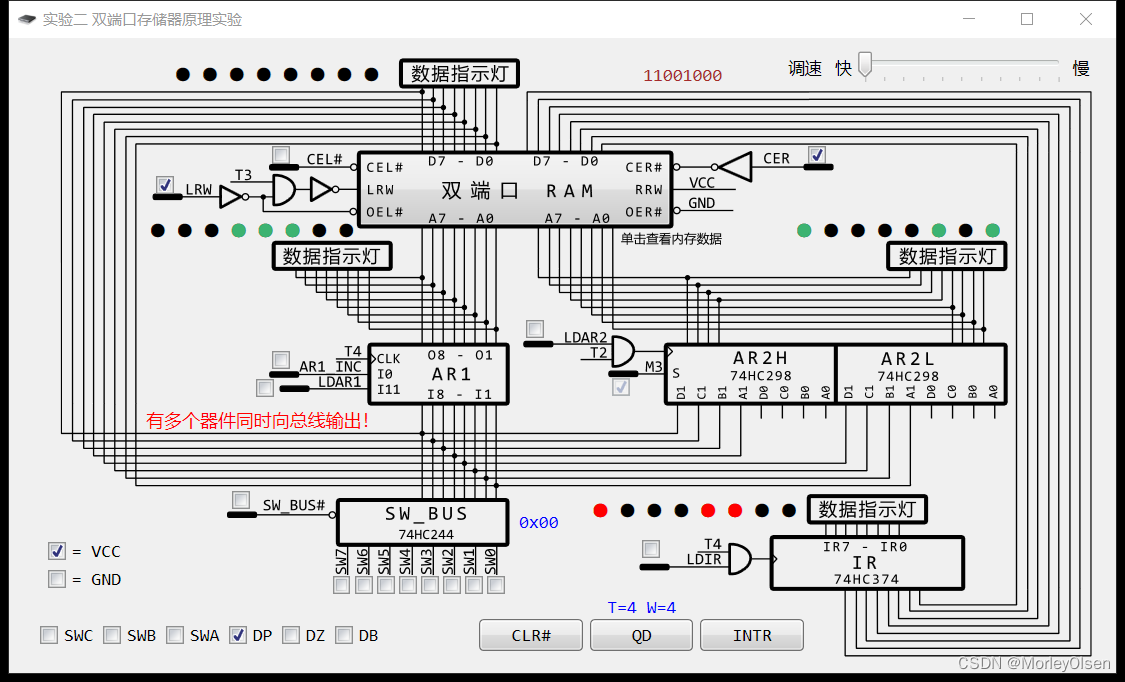

双端口存储器RAM:

左端口的数据部分与数据总线DBUS7-DBUS0相联;右端口的数据引脚与指令传输线IN7-IN0连接,显示地址和IR中的数据用IR/DBUS切换。左端口地址由AR1提供,右端口地址由AR2(两片74HC298)提供,向AR1、AR2输入地址时注意,应切换AR1/AR2开关。地址和输入数据均由SW7-SW0输入,左、右地址分别存在AR1、AR2中,并在输入时要注意AR1/AR2的切换。

| 左端口 | 右端口 |

| CEL#(低有效) | 芯片CER#(内部经过一个反向器,低有效),但是控制信号CER=1(高有效) |

| LRW(1=读,0=写) | RRW(1=读,0=写,RRW已接固定高电平 ) |

| OEL#(低电平,仿真已经设置) | OER#(OER#固定接低电平) |

实验步骤:

Step1:控制信号接线, 如下表所示。

| 开关 | K0 | K1 | K2 | K3 | K4 | K5 | K6 |

| 控制信号 | CEL# | LRW | CER | LDAR1 | LDAR2 | SW_BUS# | LDIR |

Step2:DP=1,DB=0,DZ=0。

Step3:合上电源,按CLR#。

Step4:从左端口写入数据,IR/DBUS=DBUS,AR1/AR2=AR1,向10H单元写入11H数据。

Step5:从右端口读出数据,AR1/AR2=AR2,IR/DBUS=IR,读出存储器10H单元的数据,数据送入IR中并在指示灯上显示。

上述操作的各步骤中控制信号的内容如下表所示:

| K0 | K1 | K2 | K3 | K4 | K5 | K6 | 执行的操作内容 |

| CEL# | LRW | CER | LDAR1 | LDAR2 | SW_BUS# | LDIR | |

| 1 | 1 | 0 | 1 | 0 | 0 | 0 | 地址10H写入AR1 此时SW7至SW0为:00010000 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 11H写入M[10H] 此时SW7至SW0为:00010001 |

| 1 | 1 | 0 | 1 | 0 | 0 | 0 | 地址10H写入AR1 此时SW7至SW0为:00010000 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 左端口读出M[10H] |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 地址10H写入AR2 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 | 右端口读出M[10H] |

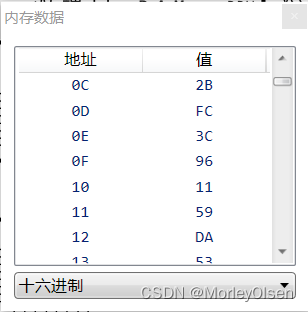

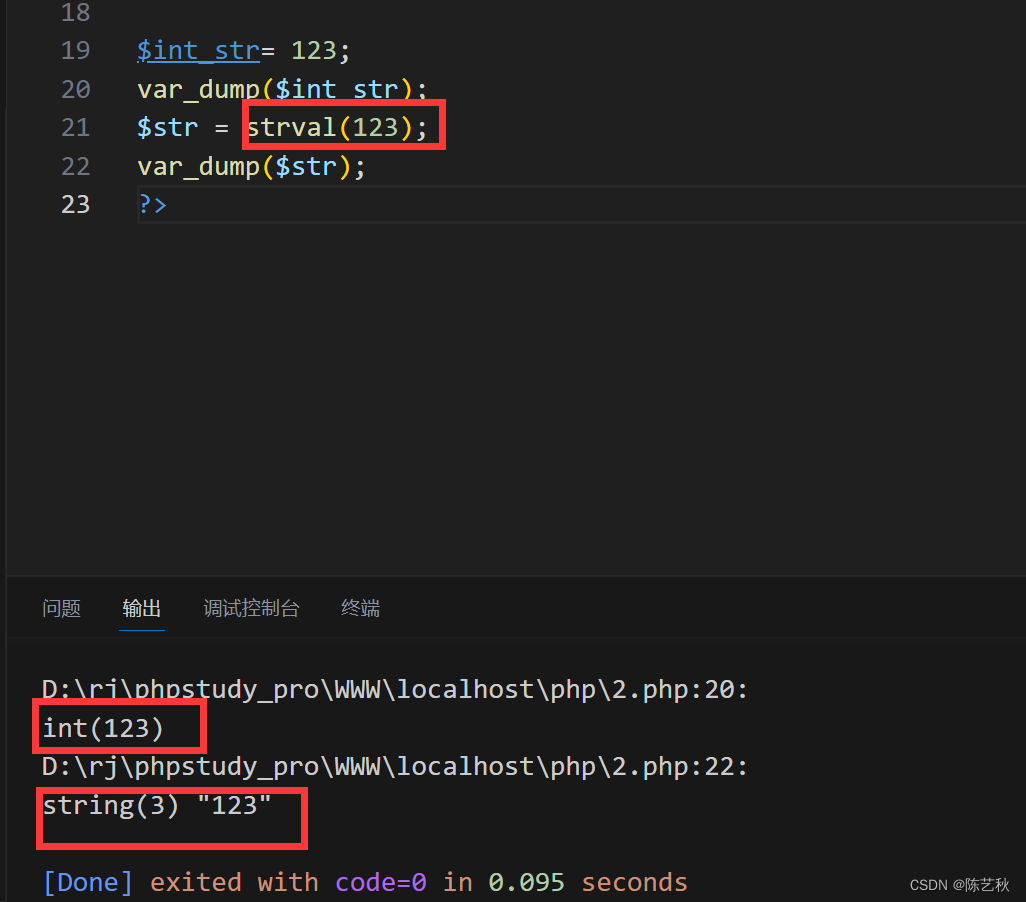

其中将11H写入10H地址后,可以双击双端口RAM,观察到数据成功写入给定的地址中,如下图所示(地址10H,值11H):

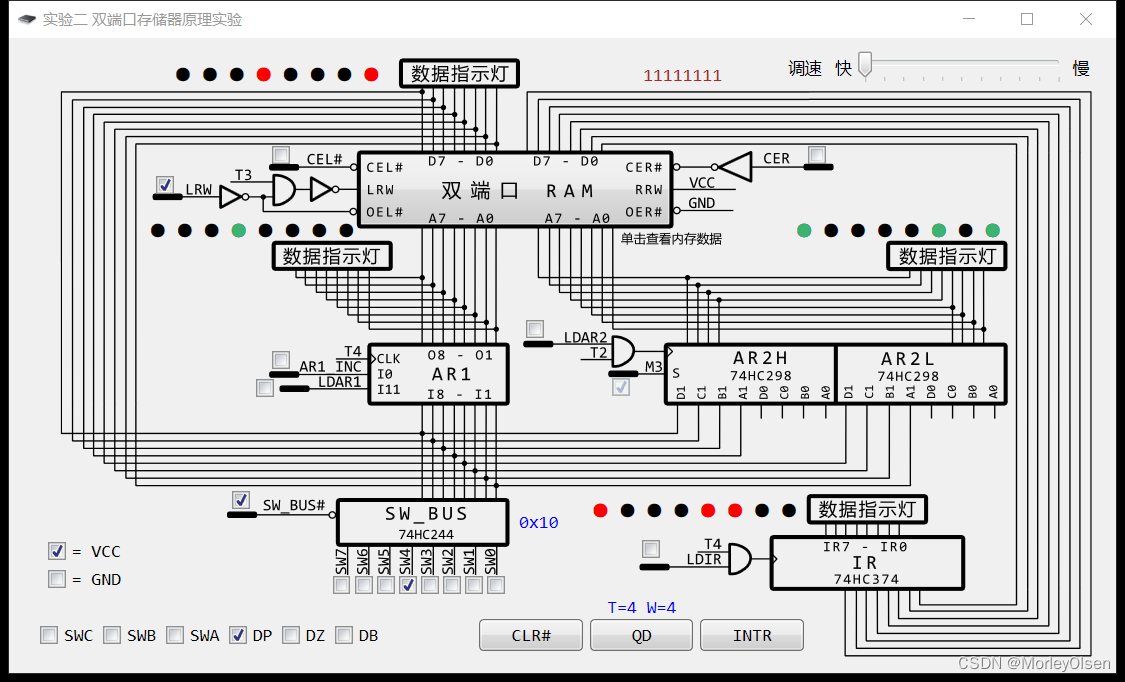

从左端口读出M[10H]如下图所示:

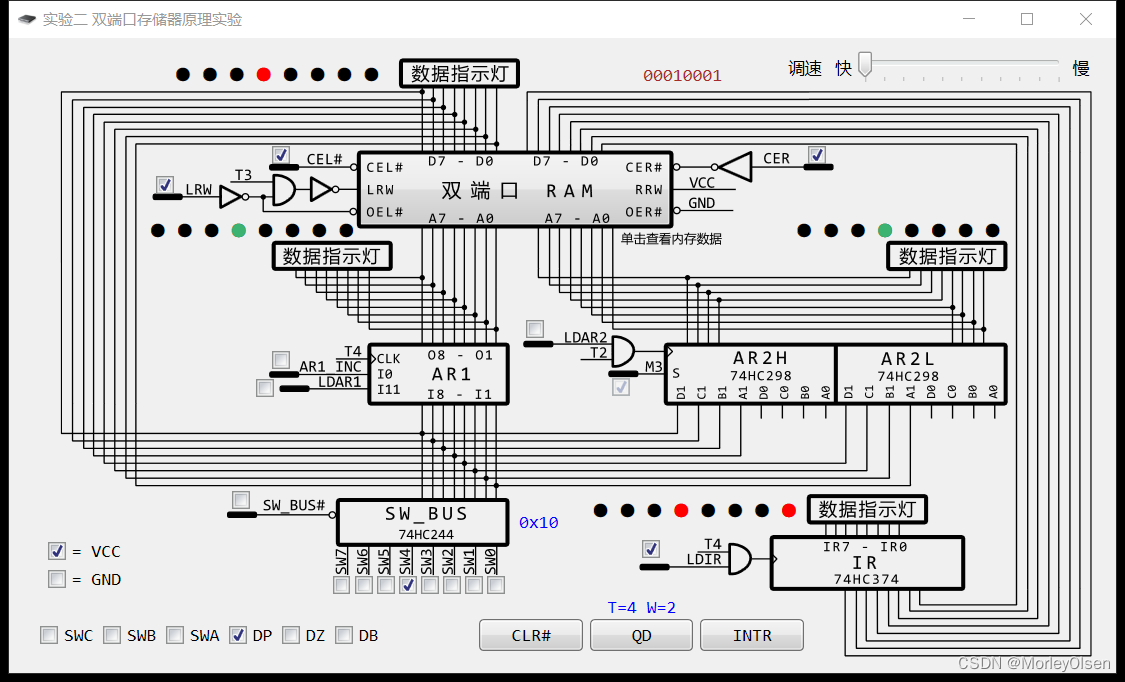

从右端口读出M[10H]如下图所示:

Step6:将控制器产生的控制信号与存储器部分的接线端孔相连接,即控制器的输出LDAR1、AR1_INC、SW_BUS#、CEL#、LRW依次与数据通路的对应信号连接,时序发生器的输入TJI接控制存储器的输出TJ。通过SWC、SWB、SWA的设置选择KWE写存储器,后续采用KRD读存储器。

(1)令DP = 0,DB = 0,DZ = 0,使实验系统处于连续运行状态。令SWC = 0、SWB = 1、SWA = 0,使实验系统处于写双端口存储器工作方式KWE。

按CLR#按钮,使实验系统处于初始状态。置SW7—SW0为80H,按QD按钮,将80H写入AR1。置SW7—SW0为01H,按QD按钮,将01H写入存储器80H单元。AR1自动加1,变为81H。置SW7—SW0为02H,按QD按钮,将02H写入存储器81H单元。AR1自动加1,变为82H。

(2)令DP = 0,DB = 0,DZ =0,使实验系统处于连续运行状态。令SWC = 0、SWB = 0、SWA = 1,使实验系统处于读双端口存储器工作方式KRD。

按CLR#按钮,使实验系统处于初始状态。置SW7—SW0为80H,按QD按钮,将80H写入AR1。按QD按钮,读出该存储单元的数据。按QD,AR1自动加1,变为81H。按QD可读出该单元的存储数据。

1:实验中问题及解决方法

无。

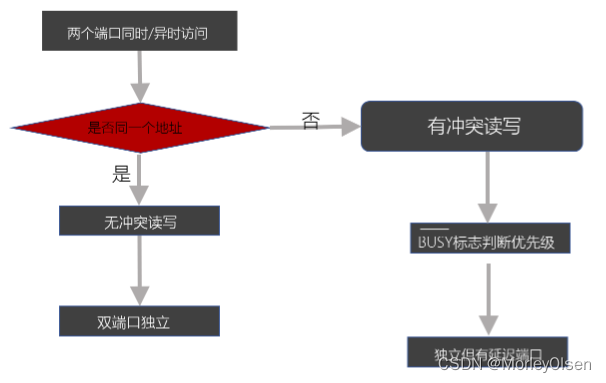

2:在什么情况下出现冲突?出现冲突后,左/右端口在何种条件下可被访问?

在 LRW置为1,CEL#置为0,CER置为1的情况下,会出现冲突,即左右端口同时读主存的同一个存储单元。

出现冲突后,左右端口在以下条件下可被访问:①如果CER不变,则需要将CEL#置为1,使得左端口为无效;或者将LRW置为0,使得左端口执行写操作而非读操作,此时可以安全访问。②如果CEL#和LRW不变,则需要将CER置为0,使得右端口为无效,此时可以安全访问。

在实际的硬件电路中,双端口存储器器件采用以下方式来判断两个端口的信号(即增加BUSY标志判断优先级,或按照两端口读写的先后顺序):

3:实验总结

- IDT7132的右端口无法写入数据,只能进行读出数据。当RRW=1时执行读操作,当RRW=0时执行写操作。本实验中RRW 已接固定高电平,故只能读出数据。

- 本实验数据线共8条,地址线共11条(8条为SW7至SW0,3条为SWC、SWB、SWA),地址的总容量为2^11*8位,其中SWC~SWA的功能为片选。

- LRW为控制双端口RAM左侧进行读写操作的信号,AR1_INC为控制地址寄存器1地址自增的信号。AR1_INC在Step1~Step5中置为0,在Step6中会置为1,使得地址自动实现增加1。

- 将寄存器R0中的数据存入给定地址中:首先通过SW_BUS置地址,存入AR1中,双端口RAM从AR1中读取地址;然后将R0寄存器的数据通过DR2直通到ALU中,从A端输出到DBUS内,(或者将R0寄存器的数据写入RS0中,从B端输出到DBUS内),双端口RAM从DBUS中写入数据进入给定地址。

- 存储器由若干个存储单元构成,实现对地址和数据的存储功能;存储单元由若干个存储位元构成,一个存储单元可以对应一个地址或数据;存储位元是0/1存储的最小单位,硬件上存储每一位的高低电平。

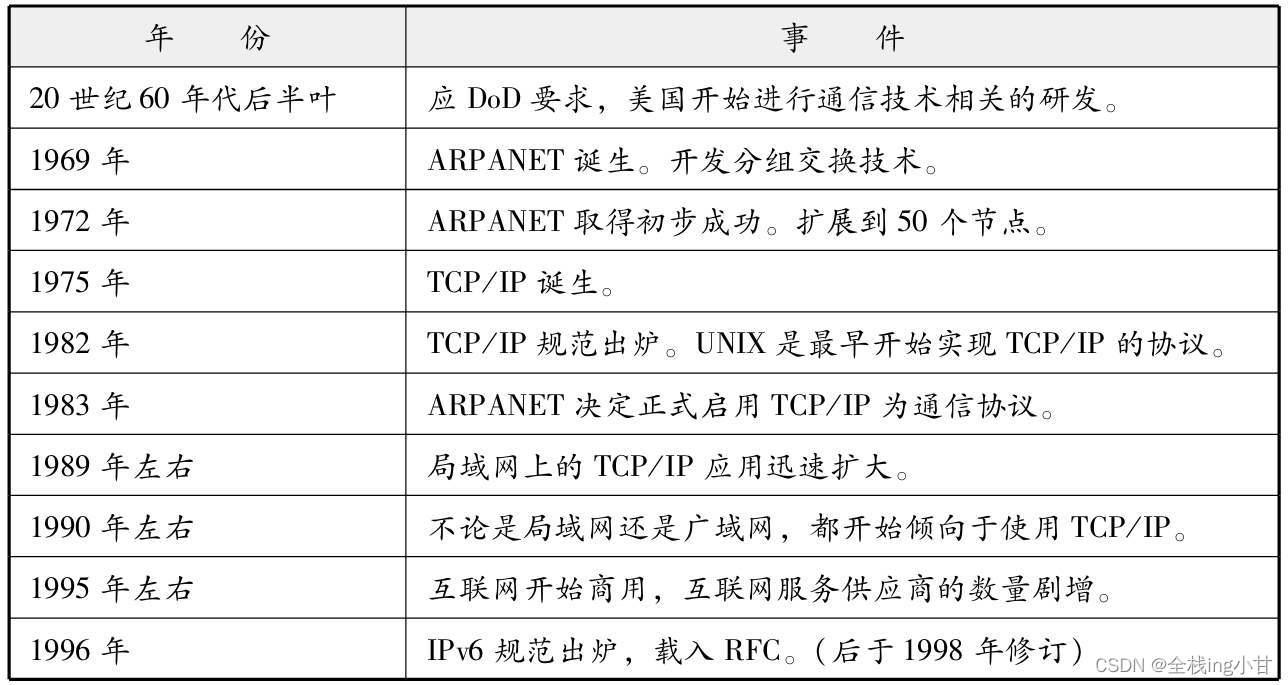

- 控制台方式开关 SWC、SWB、SWA的工作方式如下表所示:

| SWC | SWB | SWA | 工作方式 |

| 0 | 0 | 0 | PR,启动程序 |

| 0 | 0 | 1 | KRD,读取端口存储器 |

| 0 | 1 | 0 | KWE,写双端口存储器 |

| 0 | 1 | 1 | KLD,加载寄存器堆 |

| 1 | 0 | 0 | KRR,读寄存器堆 |

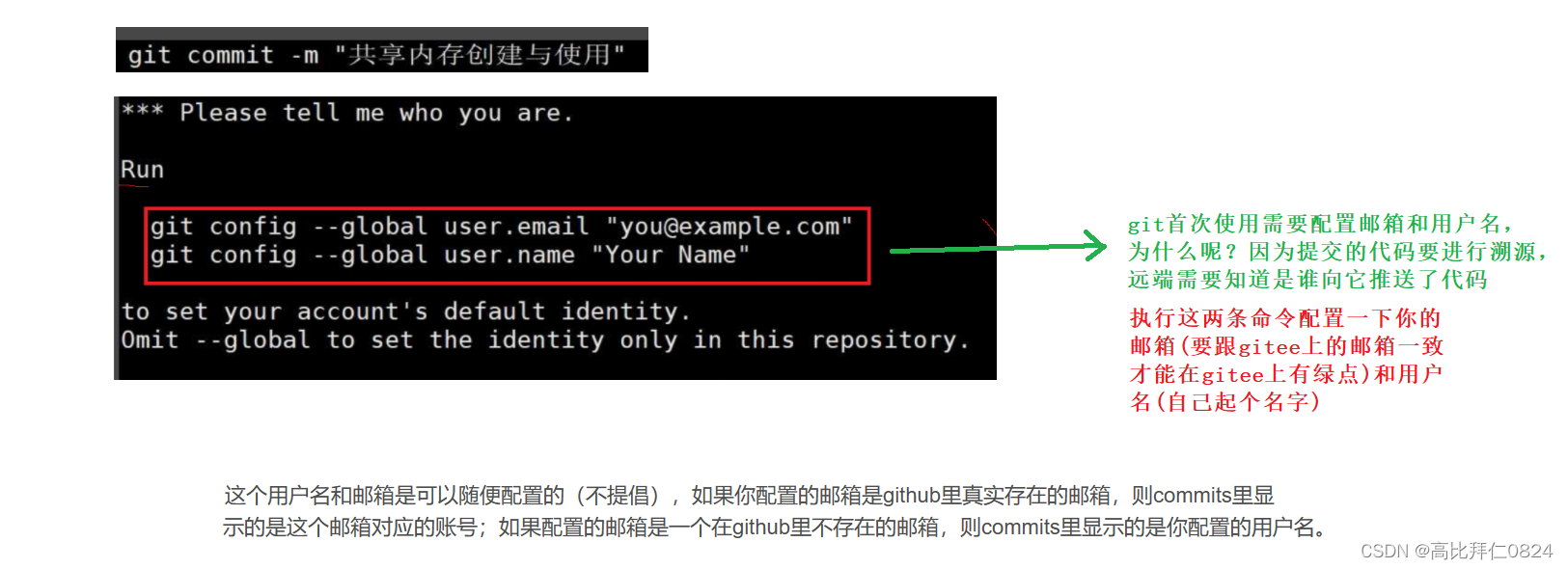

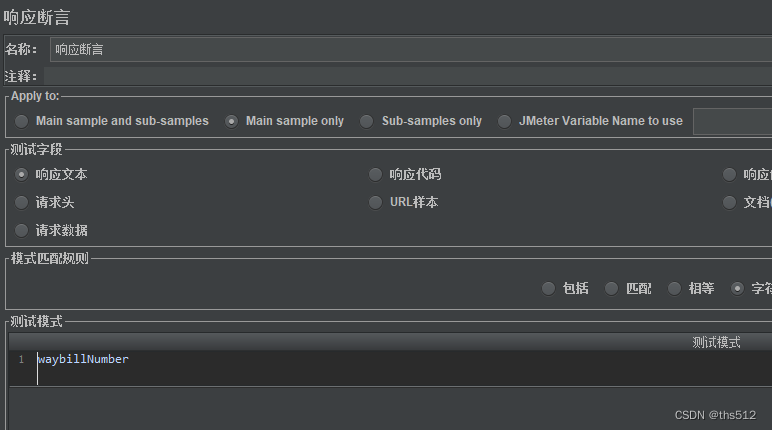

当SW_BUS# = 0,LRW = 1,CEL# = 0的时候,有多个器件同时向总线输出,会发生数据冲突,即SW控制台向数据总线输入数据,同时双端口RAM向数据总线输入数据。在虚拟实验中,报错如下图所示:

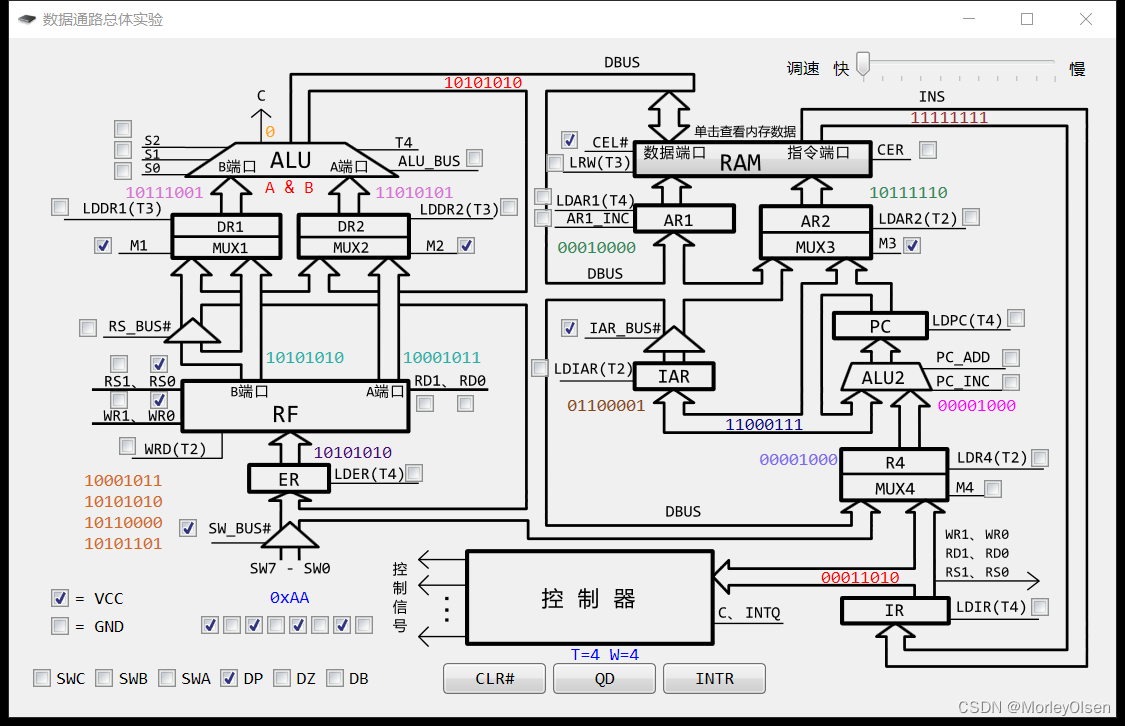

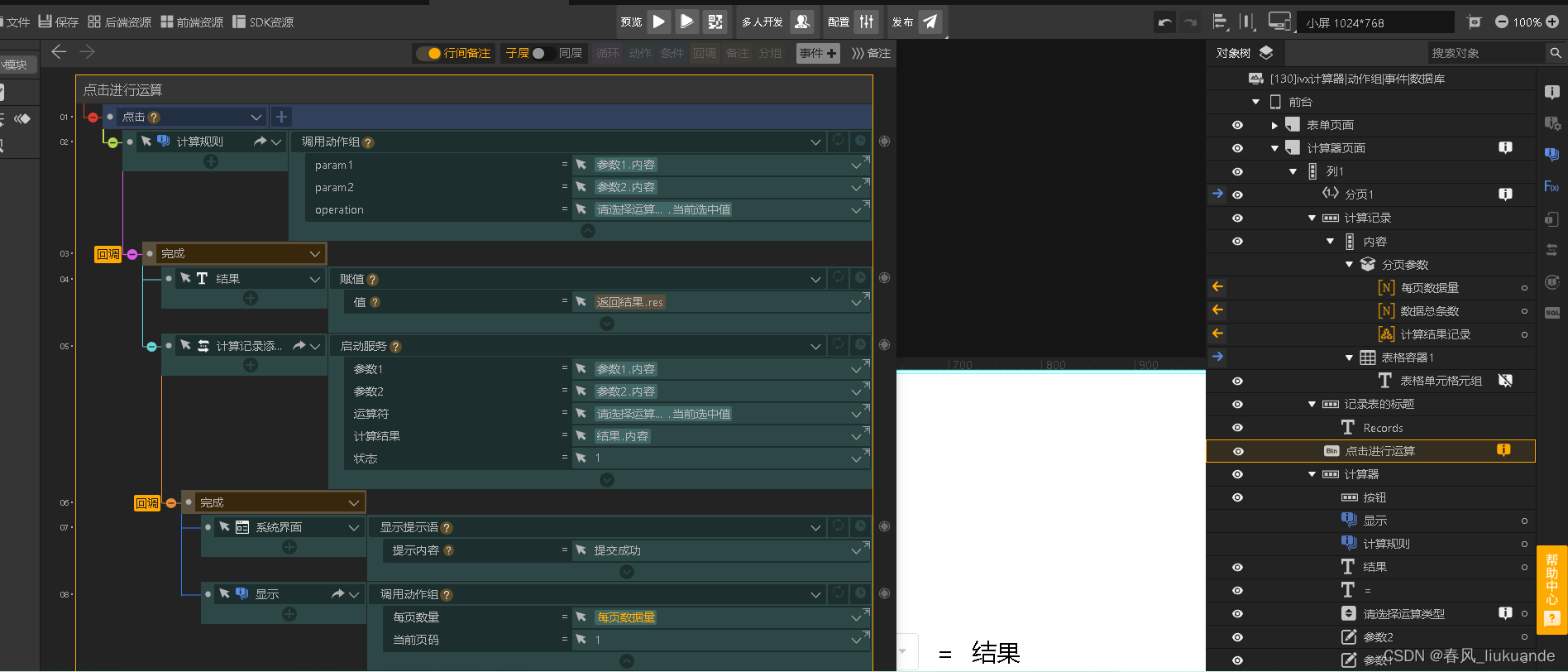

三、仿真分析

打开仿真软件,仿真面板左下角【数据通路总体图】,参照本实验指导“数据通路总体图”和存储器原理图,从存储器左端口在10H单元存入数据AAH后,并从做左端口读出10H单元中的数据,存入寄存器R1中,并从B端口读出R1的内容输出到总线。写出实现这个功能所需步骤中操作控制信号,按照操作控制信号有效的先后顺序写出。

1:向地址寄存器AR1写入地址10H,此时SW_BUS# =0,LDAR1=1,其余信号设为无效,QD脉冲后完成操作。

2:向双端口RAM左侧写入数据AAH,并存入10H中,此时SW_BUS# =0,CEL# =0,LRW=0,其余信号设为无效,QD脉冲后完成操作。

3:双击双端口RAM,可以查看到地址10H中已经存入AAH,说明存入有效。

4:从双端口RAM左侧读出10H存储的数据,此时CEL# =0,LRW=1,其余信号设为无效,不需要QD脉冲即可在DBUS上读出数据。可以查看到DBUS上端红色的数据显示10101010,说明成功读取。同时由于AR1中的地址没改变,所以不需要重新给AR1写入所读取的存储单元的地址。

5:将读取的数据写入暂存器ER,此时CEL# =0,LRW=1,LDER=1,其余信号设为无效,QD脉冲后完成操作。可以查看到暂存器上端紫色的数据显示为10101010,说明成功写入。

6:将暂存器ER的数据写入RF的R1寄存器中,此时WRD=1,WR1=0,WR0=1,其余信号设为无效,QD脉冲后完成操作。可以查看到寄存器RF左端第二个橙色的数据显示为10101010,说明成功写入R1寄存器。

7:从B端口读出R1的内容输出到总线,此时WR1=0,WR0=1,RS1=0,RS0=1,RS_BUS# =0,其余信号设为无效,不需要QD脉冲即可在DBUS上读出数据。可以查看到DBUS上端红色的数据显示10101010,说明成功读取R1寄存器。

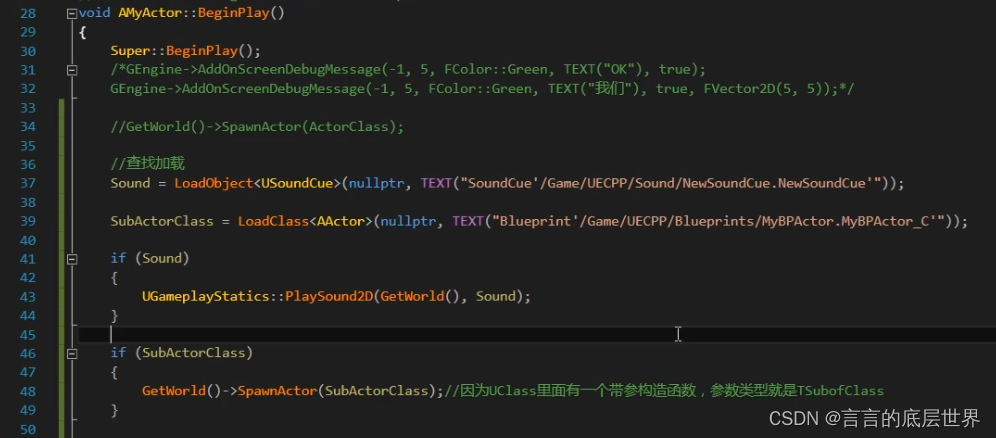

8:流程完成后的最终结果如下图所示:

四、问题回答

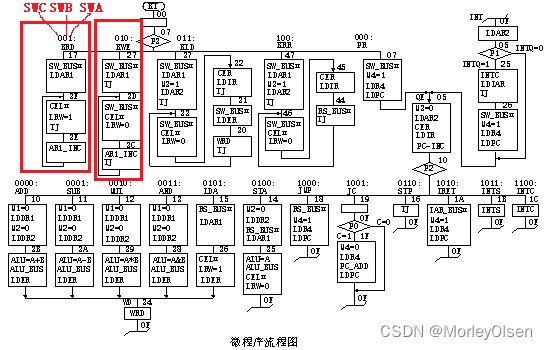

根据数据通路总图分析,指令和数据输入到存储器采用在哪种控制台方式?若程序执行应该在哪种控制台方式?

指令和数据输入到存储器时,可以采用PR控制台方式,即SWC=SWB=SWA=0。因为此时人工控制QD来启动相应程序。

如果程序执行第一个红框的内容时,可以采用KRD控制台方式,即SWC=SWB=0,SWA=1。因为第一个红框先通过SW7至SW0向AR1输入地址,然后从RAM左端口读出对应的数据到DBUS上,按QD后AR1中的地址自增1,而后重复从左端口读出数据的过程。即从起始输入的地址开始,连续对后面的存储单元读取数据,直到按下CLR#终止操作为止。

如果程序执行第二个红框的内容时,可以采用KWE控制台方式,即SWC=SWA=0,SWB=1。因为第二个红框先通过SW7至SW0向AR1输入地址,然后从RAM左端口写入对应的数据进地址,按QD后AR1中的地址自增1,而后重复从左端口写入数据的过程。即从起始输入的地址开始,连续对后面的存储单元写入数据,直到按下CLR#终止操作为止。

各控制台方式的具体内容如下表所示:

| 控制台方式 | 具体内容 |

| PR | PR是启动程序方式。 首先在 SW7 一 SW0 指定启动地址,按启动按钮 QD 后,启动程序运行。 |

| KRD | KRD是读取端口存储器方式。 (l)首先在 SW7 一 SW0 置好存储器地址; 按 QD 按钮,则将此地址打入地址寄存器 ARl,并读出该地址存储器内容到数据总线 DBUS。 (2)每按一次 QD 按钮,地址寄存器 ARl 加 l,并读出新地址存储器内容到数据总线 DBUS。 依次进行下去,直到按复位按钮 CLR#为止。 |

| KWE | KWE是写双端口存储器方式。 (l)首先在 SW7 一 SW0 置好存储器地址; 按 QD 按钮,则首先将此地址打入地址寄存器 ARl,然后等待输入数据。 (2)在 SW7 一 SWO 置好数据,按 QD 按钮,首先写数据到 ARl 指定的存储器单元,然后地址寄存器 ARl 加 l,等待新的输入数据。 依次进行下去,直到按复位按钮 CLR#为止。 |

| KLD | KLD是加载寄存器堆方式,用于对寄存器堆加载。 (1)首先在 SW7 一 SW0 置好 存储器地址,按 QD 按钮,则将此地址打入地址寄存器 ARl 和地址寄存器 AR1。 (2)在 SW7 一 SW0 置好数据,数据的低 2 位 Dl、D0 为寄存器堆中的寄存器号,按一次 QD 按钮,则 写数据到 ARl 指定的存储器单元;然后将写入的数据从右端口读出,并送入指令寄存器 IR。 (3)在 SW7 一 SW0 置好数据,该数据为写入寄存器的数据,寄存器号由 IR 低 2 位指定。 按 QD 按钮,则首先将此数据写入寄存器 ER,然后将 ER 中的数据写入指定的寄存器。 (4) 返回(2),依次进行下去,直到按复位按钮 CLR#为止。 |

| KRR | KRR是读寄存器堆方式,用于读寄存器堆中的寄存器。 (1)首先在 SW7 一 SW0 置好存储器地址,按 QD 按钮,则将此地址打入地址寄存器 ARl 和地址寄存器 AR1。 (2) 在 SW7 一 SW0 置好数据,数据的 D3、D2 位为寄存器堆中的寄存器号,按一次 QD 按钮。 则与数据到 ARl 指定的存储器单元;然后将写入的数据从右端口读出,并送入指令寄存器 IR。同时将 IR3、IR2 指定的寄存器送往数据总线 DBUS。拨动开关 IR/DBUS 可看到 IR 的值和 IR 指定的寄存器的值。 (3)返回(2),依次进行下去,直到按复位按钮 CLR#为止。 |

![LeetCode[912]排序数组](https://img-blog.csdnimg.cn/7034baa5a8204b4caf4057f0a9ea3a75.png)