3.2 闪存实战指南

闪存接口有同步异步之分。一般来说,异步传输速率慢,同步传输速率快。

(1)异步接口没有时钟,每个数据读由一次RE_n信号触发,每个数据写由一次WE_n信号触发。

(2)同步接口有一个时钟信号,数据读写和时钟同步。

3.2.1 异步时序

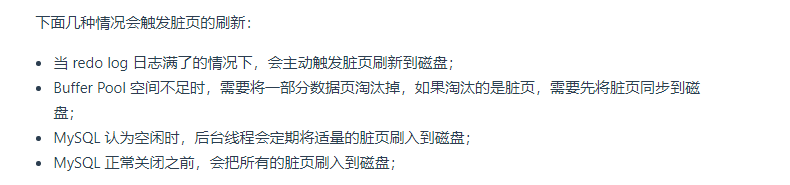

1. 异步写数据时序图

在CLE、ALE、片选(CE_n)为低时,数据在写使能信号的上升沿写入数据寄存器中。(??这个说法不一定正确)

上图中有5个信号:

从上图看出,数据写入的时候,数据总线不能传输地址和命令,所以ALE和CLE无效。每一个WE_n周期对应一次有效的数据传输。

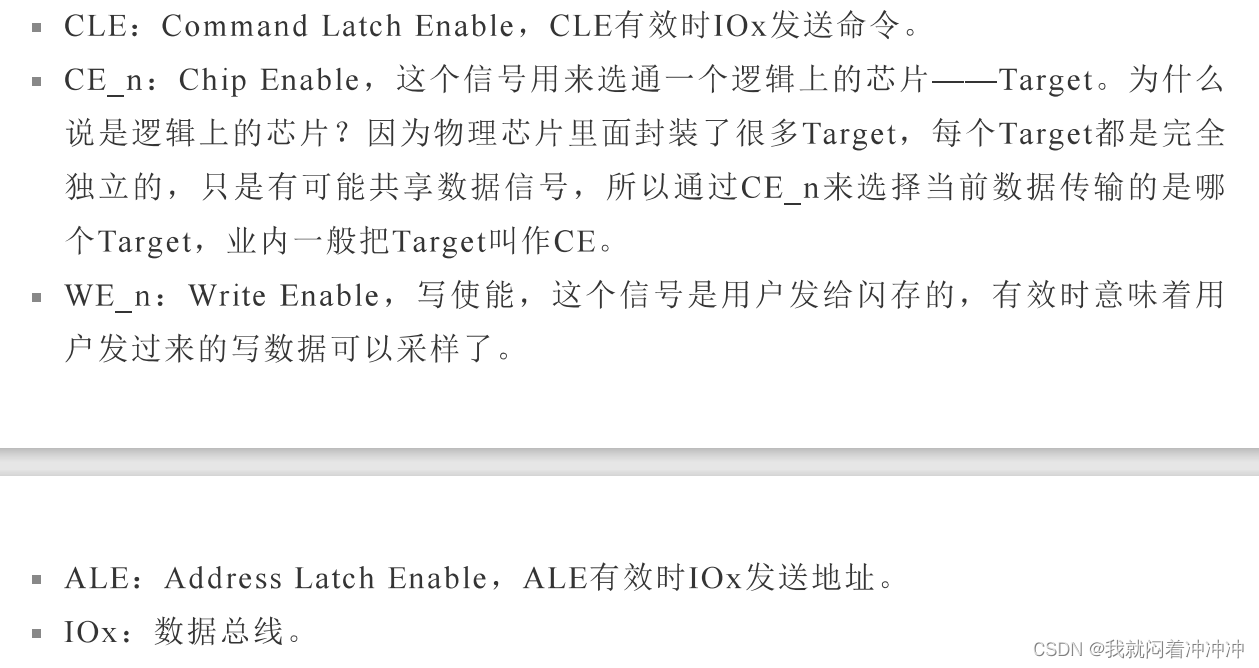

2. 异步数据读出时序

同步模式下DQS信号的上升沿与下级沿都能控制信号的传输,使传输速度翻倍。

3.2.4 闪存寻址

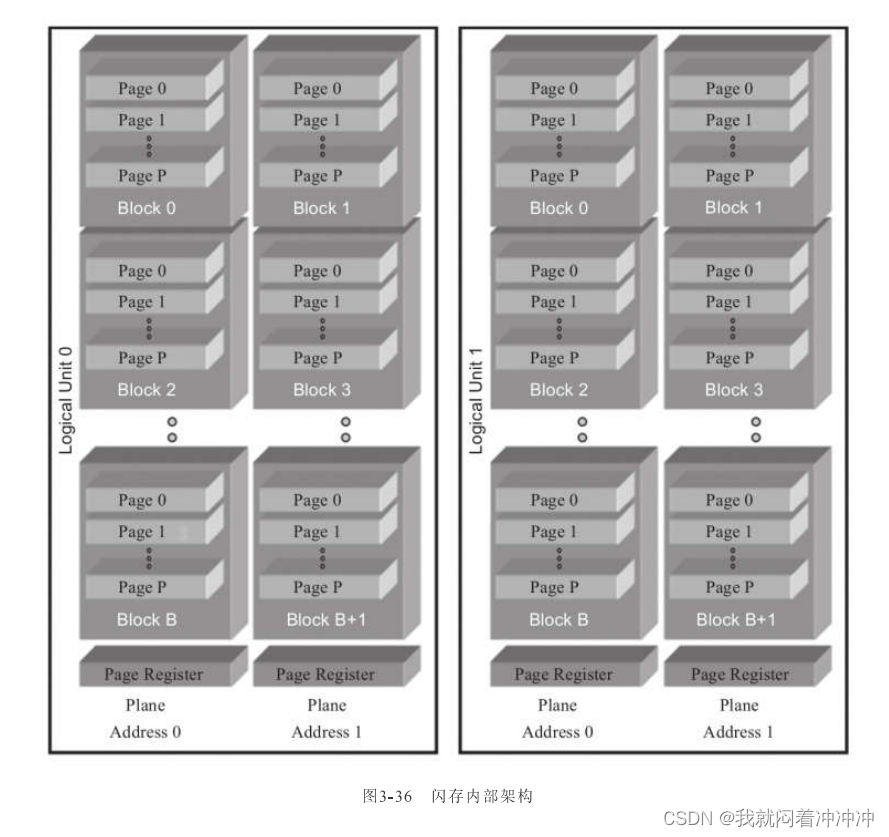

下图是一个Target,即一个可以独立工作的逻辑芯片。

一个Target包含两个LUN,一个LUN包含两个Plane,一个Plane包含多个Block,一个Block包含多个Page。

3.3 闪存特性

3.3.1 闪存存在的问题

1. 闪存坏块

闪存块Block是有一定寿命的。闪存中的存储单元先天就有一些的坏的,或者说是不稳定的,并且随着闪存的不断使用,坏的存储单元会越来越多。因此,必须要有坏块管理机制。

2. 读干扰Read Disturb

从闪存读取原理来看:当读取一个闪存页Page的时候,闪存块中未被选中的Page的控制栅极都会加一个正电压以保证MOS管是导通的。但,频繁在MOS管的控制栅极加正电压,可能会导致电子被吸进浮栅极,造成轻微写,从而导致比特翻转。但这不是永久性损伤,对Block执行擦除操作后可正常使用。

读干扰会导致浮栅极进入电子。有电子进入,会导致晶体管的阈值电压右移!

注意:读干扰影响的是同一个Block上的其他Page,而非读取的Page本身。

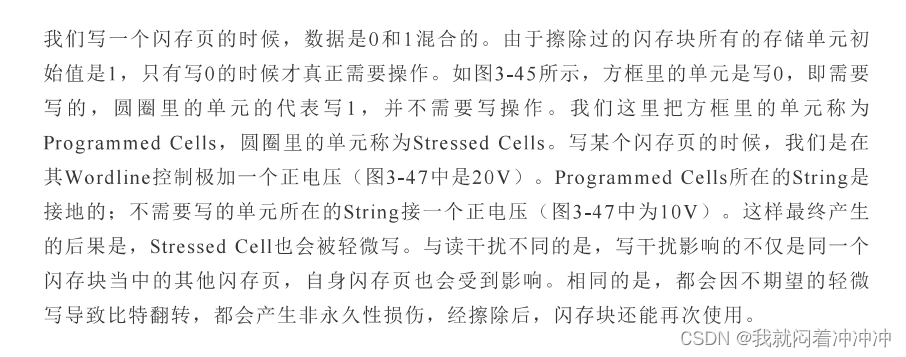

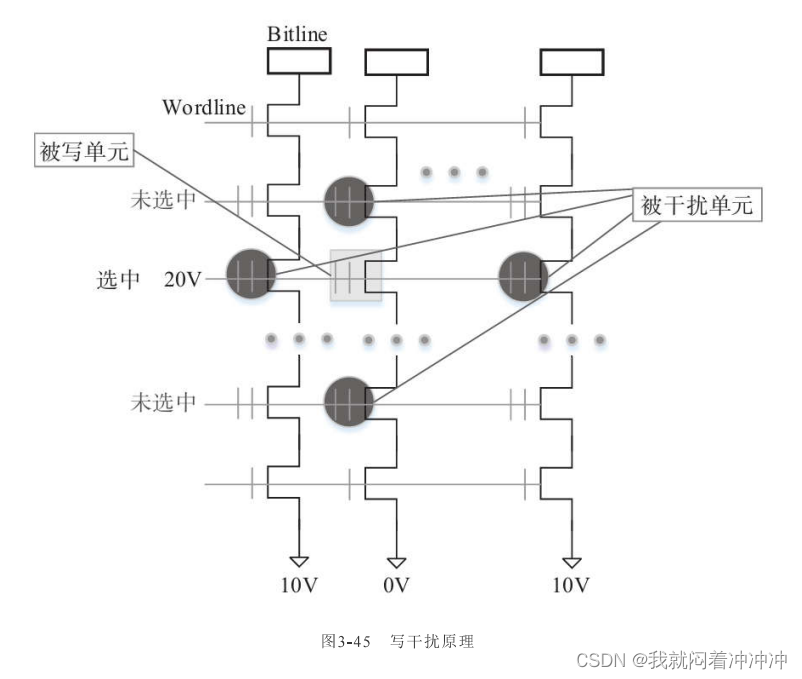

3. 写干扰Program Disturb

除了读干扰会造成比特翻转,写干扰也会。

4. 存储单元间的耦合Cell-to-Cell interference

5. 电荷泄露

存储在闪存存储单元的电荷,如果长期不使用,会发生电荷泄露。这同样会造成非永久性损伤,擦除后Block还能使用。

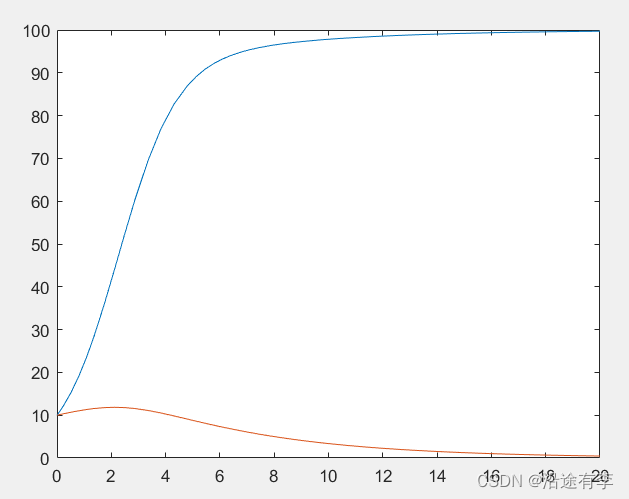

3.3.2 寿命

随着擦写次数的增加,会发生3种故障:

(1)擦过的晶体管,读出错;

(2)写过的晶体管,有可能被误检测为擦过的状态;

(3)写过的晶体管,有可能在其他的单元读的时候,把整个Bitline都给关了。

如何解决寿命问题呢?

(1)Wear Leveling:通过磨损平衡算法,让所有的闪存块均衡擦写,避免少数Block先挂掉,从而导致固态硬盘容量下降;

(2)降低写放大:写放大越低,SSD的磨损速度越慢;

(3)用更好的纠错算法:纠错能力越强,容许的出错率越高。

3.3.3 MLC使用特性

对于MLC或TLC来说,写一个Block当中的Page,应该是顺序写,如Page0-->Page1-->Page2……,禁止随机写入。原因如下:

(1)一个存储单元包含两个闪存页数据,要先写Lower Page,再写Upper Page;

(2)相邻单元之间有耦合电容,工艺上要求后面的闪存页写操作时前面的闪存页已经写过。

但对读来说,没有这个限制。SLC也没有这个限制。

3.3.4 闪存数据保质期

闪存中,数据保存时间的问题叫做Data Retention。

保质期到了的标志:从闪存读出来的数据无法使用ECC纠错成功。

如何解决Data Retention问题呢? 采用Read Scrub技术,或者叫数据巡检、扫描重写技术等。

![[MySQL]可重复读下的幻读](https://img-blog.csdnimg.cn/e64bba4b19af487faa2a5264306338e6.png)