3.1 闪存物理结构

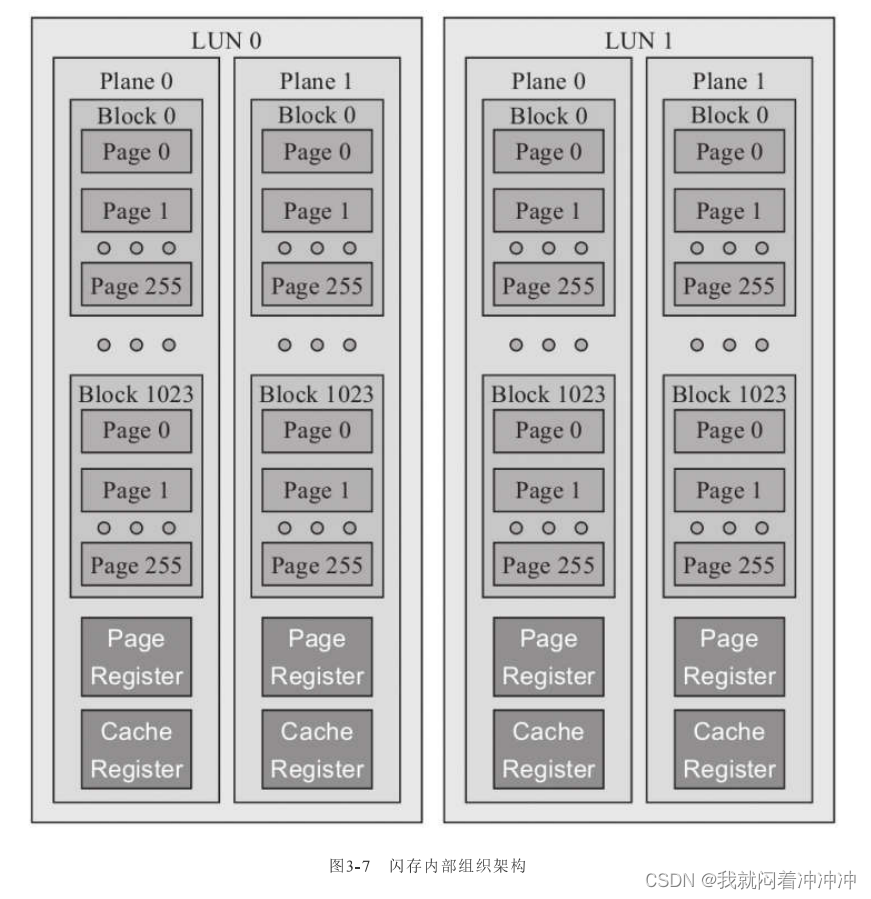

闪存芯片从小到大依此是由:cell(单元)、page(页)、block(块)、plane(平面)、die(核心)、NAND flash(闪存芯片)组成的。

一个闪存页的大小主要有4KB、8KB、16KB几种。

3.1.1 闪存器件原理

1. 闪存的特性

(1)闪存是非易失性存储器,即掉电之后数据不会丢失;

(2)闪存块(Block)需先擦除才能写入,不能覆盖写(Update in Place);

(3)闪存块(Block)具有一定的寿命。每擦除一次闪存块,都会对闪存块造成磨损,擦除到达一定次数后,闪存块要么变成坏块,要么这块闪存块上的数据变得不可靠;

(4)闪存块读的次数是有限的。读的次数多了,会造成读干扰问题;

(5)闪存天生有坏块。同时,随着SSD、的使用,会产生新的坏块。

2. 闪存基本存储单元Cell

闪存的物理结构 - 爱码网

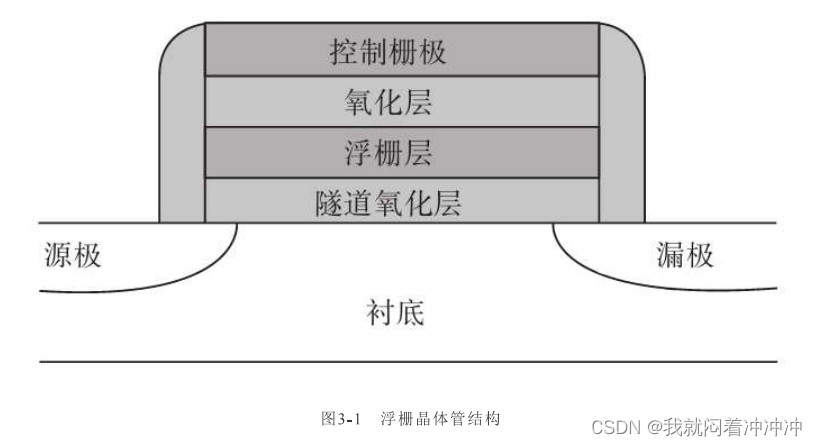

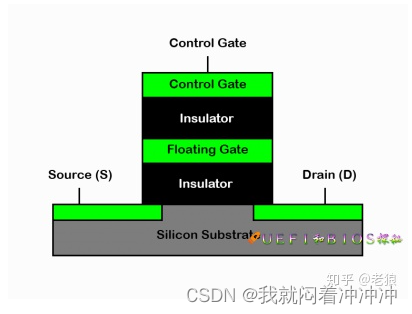

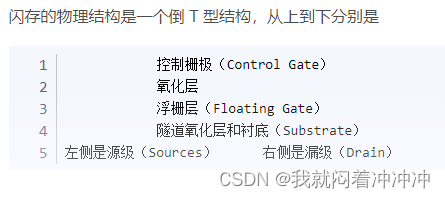

Cell:闪存基本存储单元,是闪存的 最小工作单位 ,执行数据存储的任务;它是一种类NMOS的 双层浮栅(Floating Gate)MOS管 。

闪存由源极(Source)、漏极(Drain)、浮动栅极(Floating Gate)、控制栅极(Control Gate)组成,是双栅极结构。

闪存是非易失性存储器的原因:MOS管在源极(Source)和漏极(Drain)之间电流单向传导的半导体上形成了存储电子的浮栅,浮栅上下被绝缘层包围,存储在里面的电子不会因掉电而消失。因此,闪存是非易失性存储器。

写操作是在 控制栅极 加正电压(Vpp),使电子(带负电)通过 绝缘层进入浮栅层 ;值得注意的是,该操作执行完之后,该闪存单元存储的是0!!即,此时,读取状态为0。

擦除操作是在 源极 加正电压(Vpp),利用浮栅极和漏极之间的隧道效应,把电子 从浮栅层吸引 到源极,排空浮动栅极的电子。此时,读取状态为1。

问:为什么浮栅极没有电子的时候是1,有电子是0呢????

答:闪存的工作原理_闪存原理_liukuan73的博客-CSDN博客

3.1.2 SLC、MLC和TLC

DIE,也称LUN,是接收和执行闪存命令的基本单元。

闪存根据 每个单元内可存储的数据量 分成 SLC(1bit/Cell)、MLC(2bit/Cell)、TLC(3bit/Cell)和 QLC(4bit/Cell),成本依次降低,容量依次增大(同样面积的DIE上),耐用度也依次降低。

SLC:一个存储单元存储1bit数据的闪存。

同样面积的一个存储单元,SLC、MLC、TLC分别可以存储1bit、2bit、3bit的数据,所以在同样面积的DIE上,闪存容量依次变大;

同时,一个存储单元电子划分越多,读、写、擦所要耗费的时间就越长。故而,性能上SLC>MLC>TLC。

3.1.3 闪存芯片架构

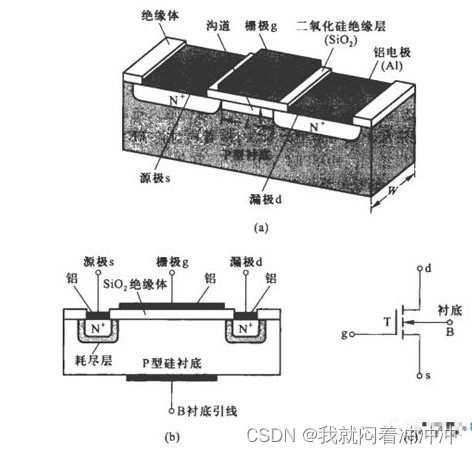

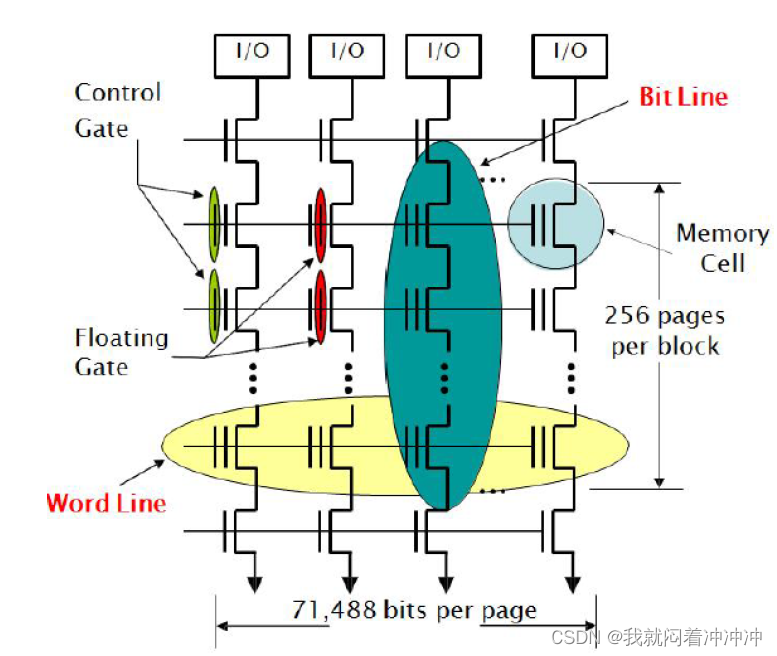

下图是一个闪存块Block的组织架构。一个Wordline(字线)对应着一个或若干个Page。一个Page有多大,那么Wordline上面就有多少个存储单元,就有多少个Bitline(位线)。一个Block当中所有的存储单元(Cell)共用一个衬底。

Wordline(WL)是字线,其控制读取和写入,故而Page是最小的读写单位。

Bitline(BL)是位线。

Wordline是将一定数量(2的n次方)的存储单元的控制栅极连接起来。当Wordline上为H时,存储单元打开,此时Bitline上就可以读或者写数据到存储单元了。

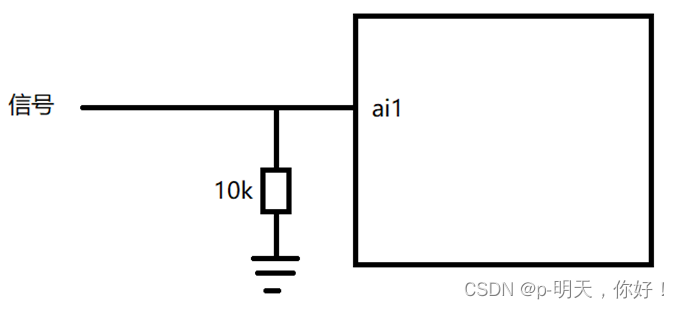

如下图,NAND 一个plane内部MOS阵列,MOS管的漏极BL=bit line,控制栅极 WL=word line,源极都连在一起,WL连接了若干个page,通过WL加不同电压和不同时间长度进行各种操作,在BL端进行读的操作。Bit Line对应的一串MOS叫做string,Block的高度一般是一个string,但是很宽,很多个WL。

一文详解闪存flash读写的原理 - 存储技术 - 电子发烧友网 (elecfans.com)

上图中,Control Gate相当于MOS管的G极(控制栅极),Floating Gate是浮栅层。

DIE/LUN是接收和执行闪存命令的基本单元。但在一个LUN中,一次只能独立执行一个命令,不能对其中一个page进行写操作的同时,又对另一个page进行读操作。

闪存块Block是最小的擦除单位。原因:一个闪存块Block中的的所有存储单元是共用一个衬底(Substrate)的。如果对某个衬底加电压,那么所有浮栅层的电子都会被吸出来。

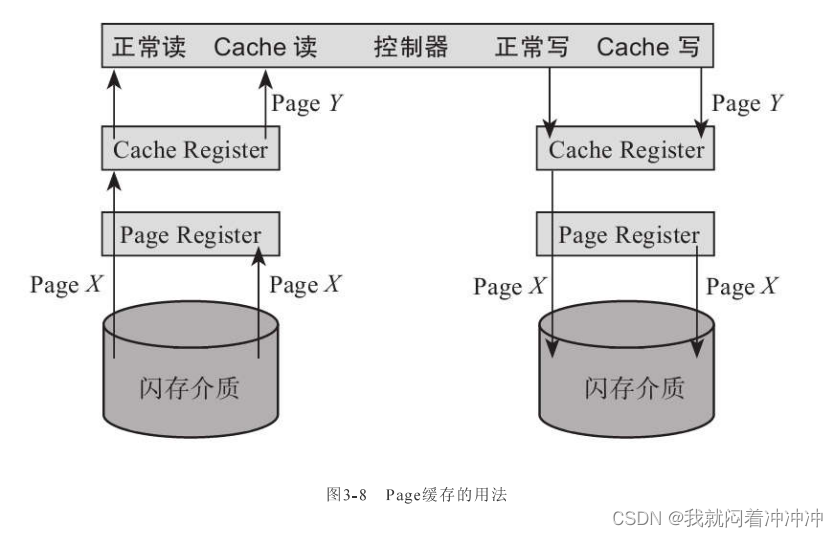

一个DIE可以分为若干个Plane,每个Plane有独立的Cache Register(高速缓冲寄存器)和Page Register(页寄存器),其大小等于一个Page的大小。

固态硬盘在写某个Page的时候,先把数据从主控传输到该Page所对应Plane的Cache Register中,再把整个Cache Register中的数据写到闪存阵列;读则相反,即闪存介质-->Cache Register-->主控。 注意:无论是从闪存介质读取数据到Cache Register,或是从Cache Register写数据到闪存介质,都是以Page为单位!!!

3.1.4 读、写、擦原理

一文详解闪存flash读写的原理 - 存储技术 - 电子发烧友网

如果浮动栅极Floating Gate中没有电子(即没有执行过写操作或执行过擦除操作),那么通过阈值电压可以控制电流的通断:

(1)当控制栅极上的电压 > 阈值电压VT时,此时没有电流,相当于开关断开,对应状态为0;

(2)当控制栅极上的电压 < 阈值电压VT时,此时有电流,相当于开关合上,对应状态为1。

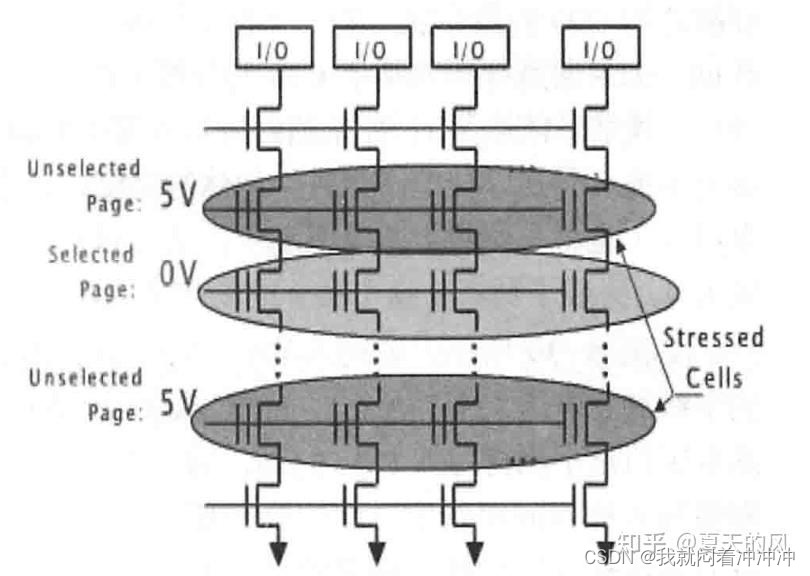

1. 读

当要读某个Page时:

(1)将该Page的Wordline(即同一个Page中所有Cell上的控制栅极CG端的导线)电势置为0(即不加电压);

(2)其他所有Page的Wordline电势升到一个值,这个电压又不至于把浮栅极Floating Gate中的电子吸出来。

之所以抬高电势,是为了让其他Page所有的Cell的源极和漏极处于导通状态;没加电压(要读取的Page上)的那些Cell,其源极和漏极的通断,完全取决于其浮栅极中是否存在电子:

1)若存在电子(即该Page已执行过写操作),处于断开状态,读到0;

2)若不存在电子(即该Page没有执行过写操作),处于导通状态,读到1。

总结:对要读的Page加低电压使电流断开,看Floating Gate中是否有电子,有电子为0, 否则为1。

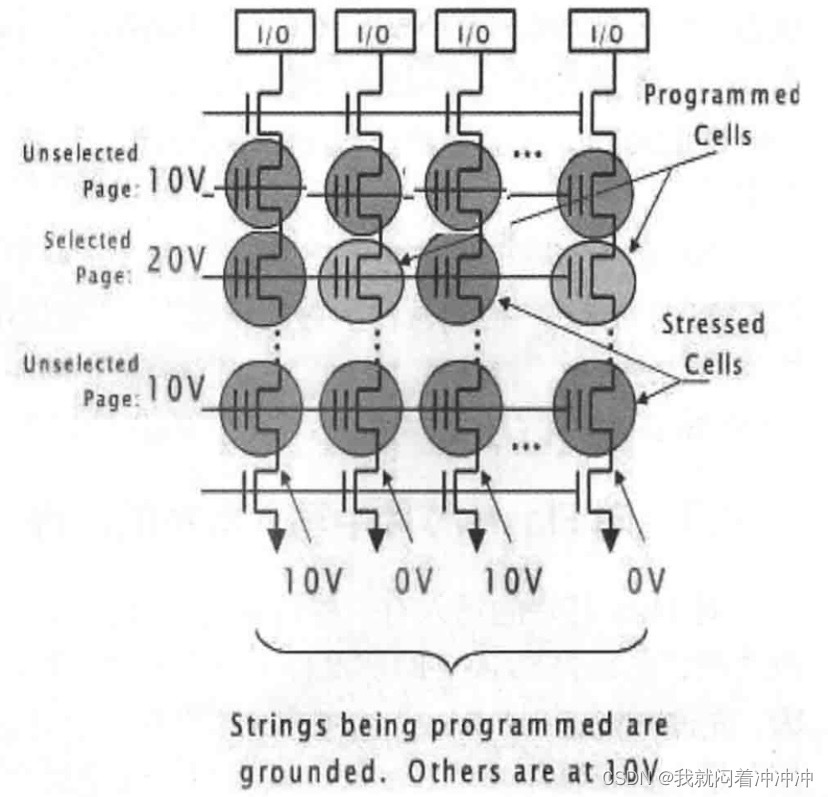

2. 写

执行写操作是对浮栅极充电子,也称为program。

写之前需先执行擦除操作,擦除之后,数据变成了1。所以,需要对写入0的浮栅极进行充电。

当写入某个Cell时:

(1)将选中Page的Wordline加高压,对应Bitline不加高压;

(2)对Page里其他Cell的Bitline加正常电压,保持电流导通;

(3)将其他Page的Wordline加正常电压,保持导通。

不需要写入数据的Cell的Wordline和Bitline电压抵消,电子不动;需要写入数据(选中)的Cell,由于电势差,将电子从Bitline吸到浮栅极中进行充电。

上面仅是示例,读写的基本单位都是Page。实际上无法对某个Cell进行写入,因为无法对同一个Page里的不同Cell既充电又放电。

3. 擦除

擦除动作,就是将一大片连续的Cell全部放电。实际操作是在衬底加电压足够长时间,把电子从浮栅极中吸出来。

擦除是以Block为基本单位,因为一个Block共用一个衬底,所以一次只能擦除一个或多个Block。擦除之后,整个Block的数据都为1。