目录

- 1.定义

- 2.电磁干扰理论

- 3.电磁干扰的流程、标准和认证

- 4.影响集成电路抗干扰性能的几个因素

- 5.减少EMC/EMI的技术

电子线路易于接收来自其他发射器的辐射信号,无论是有意或无意发射。这些电磁干扰(EMI)使得设备内毗邻的元件不能同时工作。这时就有必要进行电磁兼容(EMC)设计以避免系统内有害的电磁干扰。与大多数项目不同,EMC承诺不能只由设计来保证,必须经过测试。

1.定义

电磁兼容性是一个系统在预期的电磁环境中运行而不对其它系统产生不利影响或不受其他系统不利影响的能力。

一个系统电磁兼容应该满足:不干扰其他系统、不易受其他系统的干扰、自身不干扰。

换言之,电磁耦合性包括辐射、免疫和自兼容。电磁兼容性的每一项包括三个因素:

1)源头,谁是噪声的发射体。

2)受体,谁是噪声的接收者。

3)耦合机理,通过这种机理噪声从源头传输到受体,并产生数种不同现象。

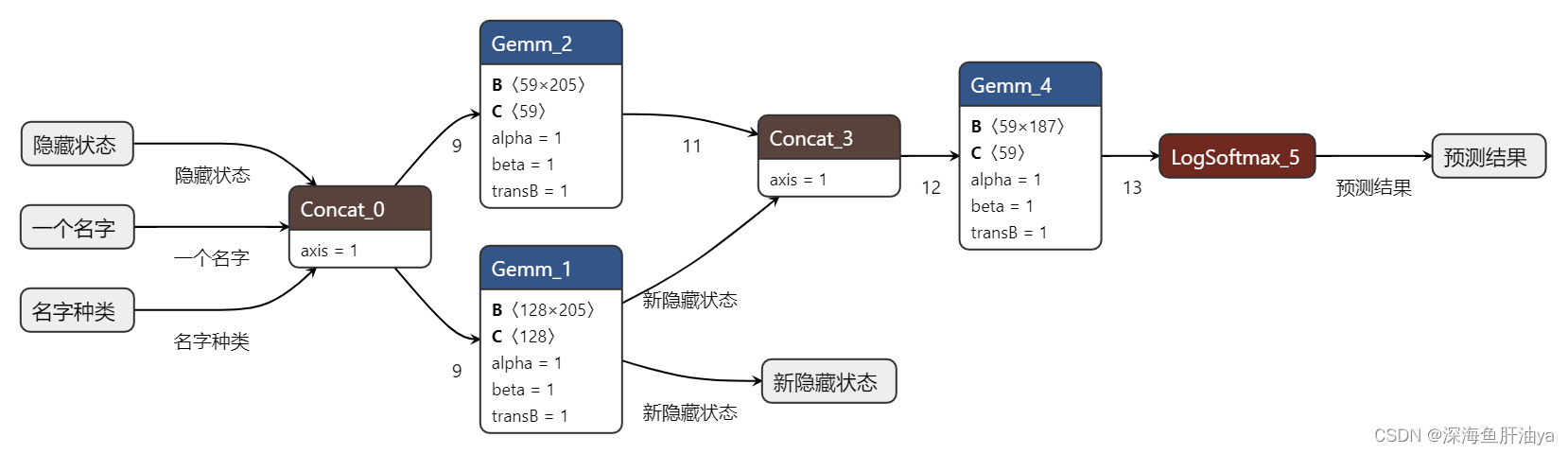

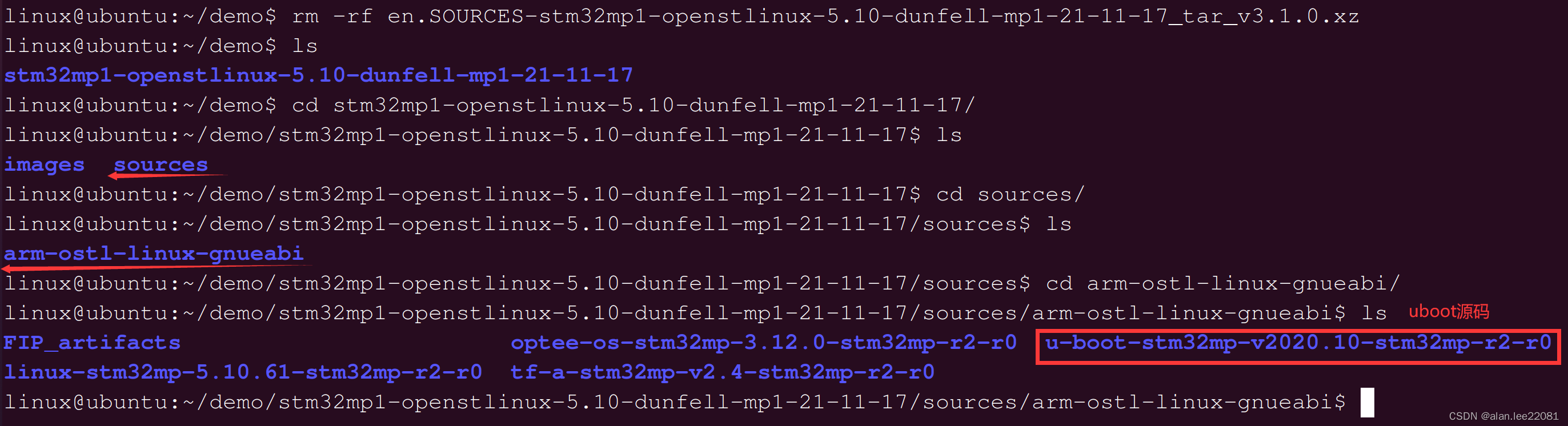

下图显示了4种基本的耦合机理:传导耦合、电容耦合、磁耦合或感应耦合、辐射耦合。每一种耦合途径可分解为一种或多种耦合机理的共同作用。

以下是接下来要用到的一些术语:

电磁干扰(EMI)是一个电子设备中破坏性的电磁能量通过辐射或传导途径传输到另一个电子设备的过程。

一个设备的电磁敏感度(EMS)水平是指对电气干扰和传导式电气噪声的抵抗能力。静电放电(ESD)和快速瞬间触发(FTB)试验确定一个设备在不良电磁环境中运行时的可靠性水平。

2.电磁干扰理论

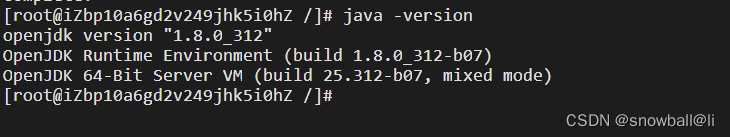

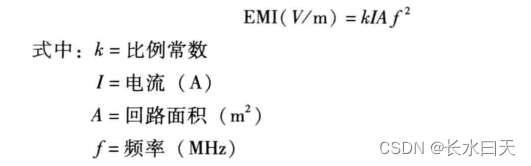

电流是产生电磁辐射的关键。当微控制器速度增加,电流的需求也增加。电流流过一个回路则产生磁场,磁场大小与回路面积成正比。回路面积定义为线路长度乘以到接地板的距离。当信号改变逻辑状态时,变化的电压产生电场。这样,电流回路生成了辐射。下面的方程显示了电流、回路面积与电磁干扰频率的关系。

由于线路板层叠要求,到接地板的距离通常固定,因此,减少辐射的关键就是减少电路板设计的线路长度。

3.电磁干扰的流程、标准和认证

目前存在几种有关EMS和EMI问题的标准,每种标准都有其应用领域,用于制成产品或设备。到目前为止,还没有应用于子体系或电子元器件的官方标准。然而,EMC测试必须在子系统中执行,以用于评估和优化电磁兼容性性能的应用。

4.影响集成电路抗干扰性能的几个因素

- 作为噪声源的微控制器

在微控制器的应用环境中,静电放电、电源、高电流或电压下的开关、射频(RF)发生器就是产生电磁干扰或噪声的一些因素。

微控制器(或其分支电路)既是源头也是受体。

1)电源和地线中的电流:作为CMOS设计的一部分,时变电流在电源和地线中流动,以数种不同方式产生辐射和传导EMI。

2)振荡器行为:当振荡器为微控制器提供时钟脉冲源时,它就是一个连续的RF源。在振荡器电路各部分流动的任何时变电流都是重要的发射源,包括流经输入、输出、电源和接地部分的电流。

3)系统时钟电路:系统时钟可能是系统中最大的噪声源,尤其随着当今PC和工作站需要更高的时钟频率。这种辐射主要由基本谐波和低阶高次谐波产生,遗憾的是,常与收音机的常用高频FM波段冲突并干扰。这就迫使监管机构对可能使用时钟并产生辐射的PC和电子设备施加电磁辐射限制。

4)输出行为:任何常见单片机的输出行为包括时钟输出、数据和地址信号,都是潜在的发射源。

5)开关噪声:开关噪声是指当一个信号激发起通路电感和负载电容的谐振而产生的干扰信号。开关噪声大到引起误操作才会引起关注,而它同样会增加额外的谐波量从而增加EMI。

6)I/O开关:I/O开关的负载包括封装引脚和焊线电感。最坏情况下的噪声依赖于开关时间。

对于一些微控制器,存储空间(地址/数据总线)通常是外部的(如SRAM、DDR等),这意味着信号在数个线路上的连续转换,这将对总体的电磁兼容产生重大影响。

- 影响电磁兼容性的其他因素

除微控制器以外,其他影响电磁兼容性的因素包括以下几个:

1)电压:较高的电源电压意味着更大的电压摆动和更多的辐射。较低的电源电压影响敏感性。

2)频率:频率越高发射越多。当晶体管因开关通断时,高频数字系统则产生电流尖脉冲,增加了总体的噪声。

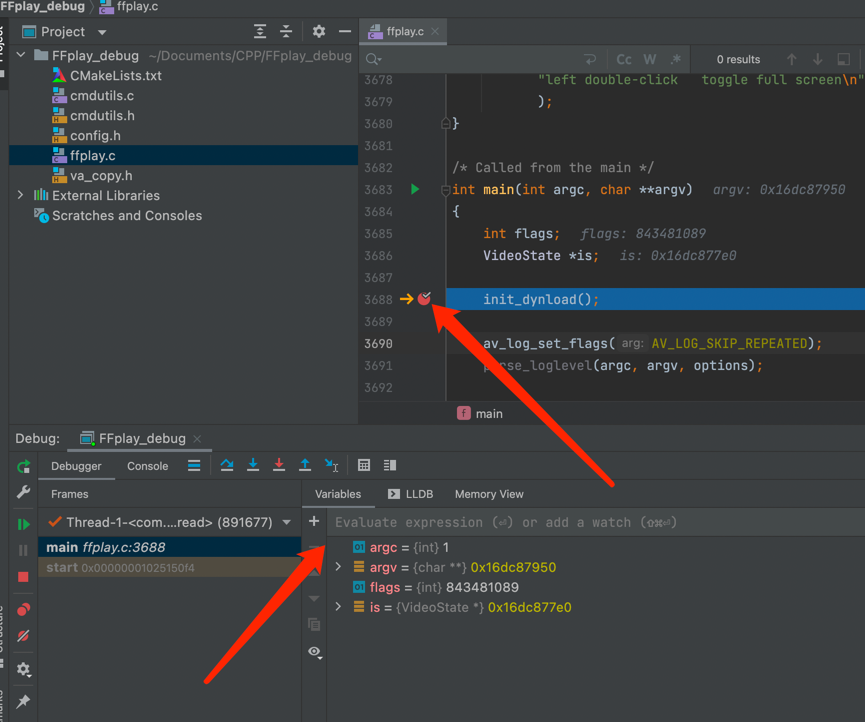

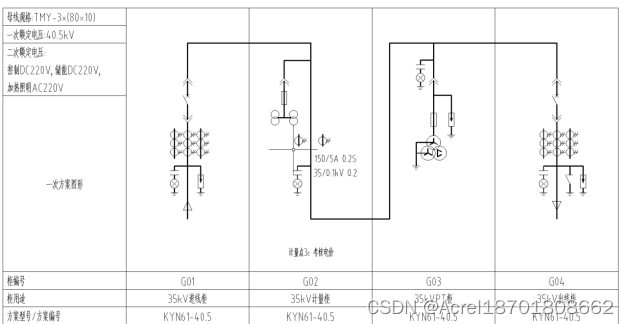

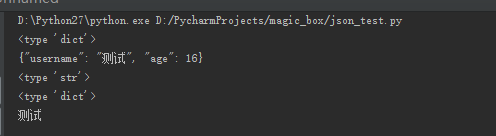

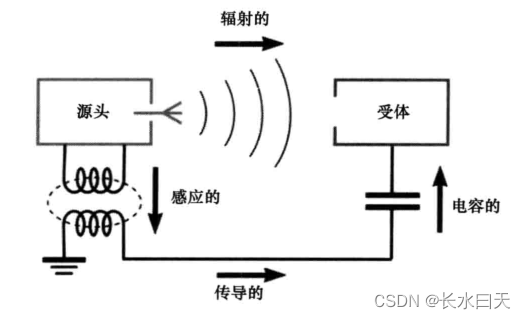

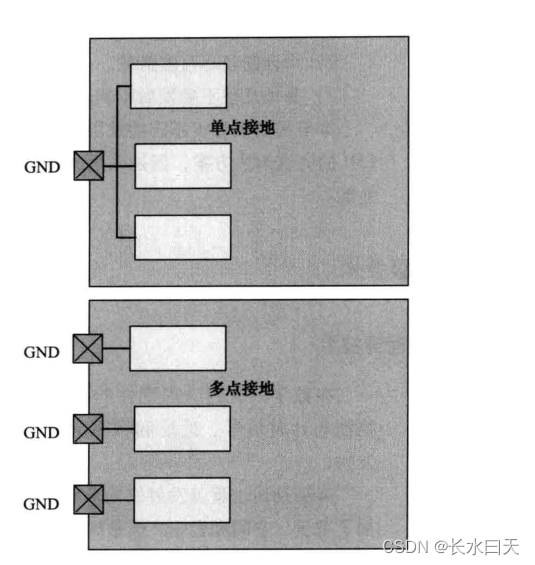

3)接地:无论是发射、敏感性或自兼容性等所有电磁兼容性问题,最重要的问题是接地不充分影响EMC。单点接地在低频率下是可以的,但高频率下有高阻抗性就不行了。多点接地最适用于高频率应用,如数字电路等(如下图)。

4)集成电路设计/印制电路板:芯片尺寸、制造工艺、版面布局(多点接地和电源引脚改进)和封装方法都会影响EMI。而且,恰当的印制电路板布局对防范电磁干扰也必不可少。

- 噪声载体

EMI可通过电磁波、传导、容性/感性耦合来传递。EMI必须到达导体才能干扰元器件。这就意味着导体的回路、超长或大面积容易受到EMI影响。

5.减少EMC/EMI的技术

防止干扰的三种办法是:在源头抑制发射、耦合路径尽可能低效、受体几乎不受发射影响。

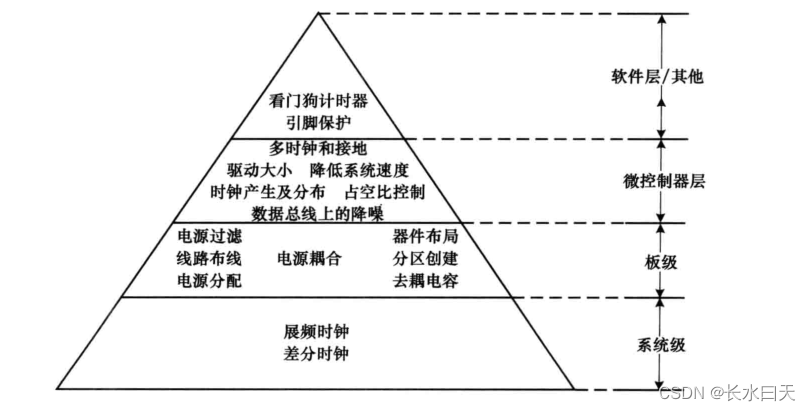

以下是一些处于不同抽象层次的常用噪声降低技术:

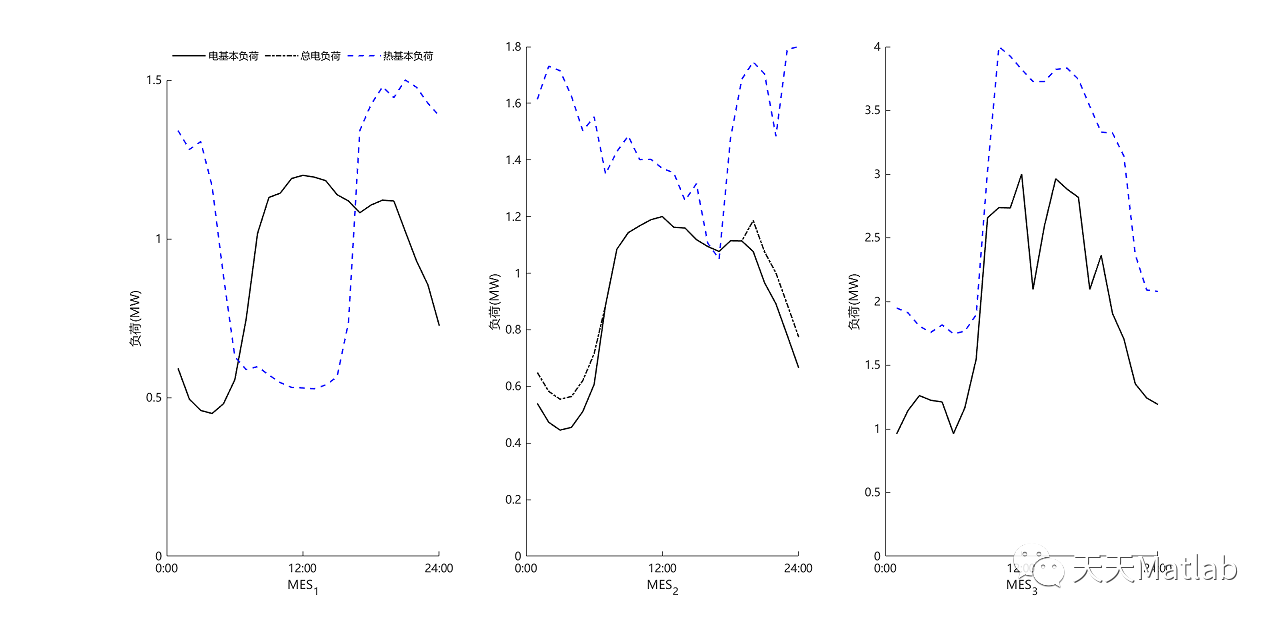

- 系统级技术:展频时钟技术、差分时钟

- 板级技术:电源输入滤波、更多的滤波器、元件布局、接地路径、线路布线、制作分区、电源耦合、印刷电路板配电和去耦电容器

- 微控制器级技术:多时钟和接地、消除竞态条件、降低系统速度、驱动器规格、时钟产生及分配、占空比考虑、降低数据总线上的噪声

- 软件层级技术:通用I/O引脚保护、数字输入引脚、数字输出和关键寄存器、复位引脚保护、振荡器和其他敏感引脚、看门狗定时器、非法指令和非法地址复位、低电压检测/低电压警告

- 其他技术:多电源和接地引脚、使用最低频率的技术

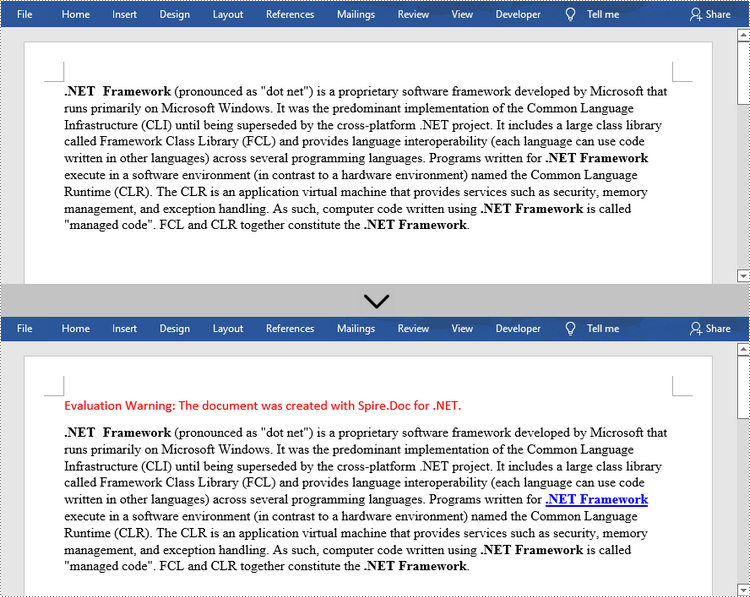

如果不处理,多余的辐射或EMI将产生严重问题。设计好的EMC很重要。本章节提供了多种不同抽象层次的指南来改善下图中总结的EMC问题。