引言

与硅基器件相比,III-V半导体具有更高的电子迁移率和峰值速度,因此更适合光电子学以外的高性能应用。目前III-V材料的不同工艺技术仍然具有挑战性,需要进一步发展。ICP-RIE(电感耦合等离子体反应性离子蚀刻)蚀刻技术使等离子体蚀刻能够在较低的压力下操作,其具有各向异性特征,蚀刻速率相当于或高于传统的反应离子蚀刻(RIE)。然而,就各种器件而言,获得近乎完美的各向异性轮廓的关键制造步骤对等离子体蚀刻化学和掩模材料的选择都很敏感。

实验与讨论

实验在表面技术系统(STS)反应器中进行,该反应器装备有最大可用功率为900 W、13.56 MHz的RF线圈发生器。本研究中使用的气体是BCl3、Cl2、Ar、N2和O2。在所有的实验中,电极的温度固定在25℃。为了避免仅使用氯化学物质污染ICP反应器,我们通过两个专用的反应室分别形成金属掩模和光致抗蚀剂掩模。在每次运行之间进行5分钟的氧气清洗程序,以从反应器侧壁去除任何聚合物,最大限度地减少污染,并保持工艺的可重复性。

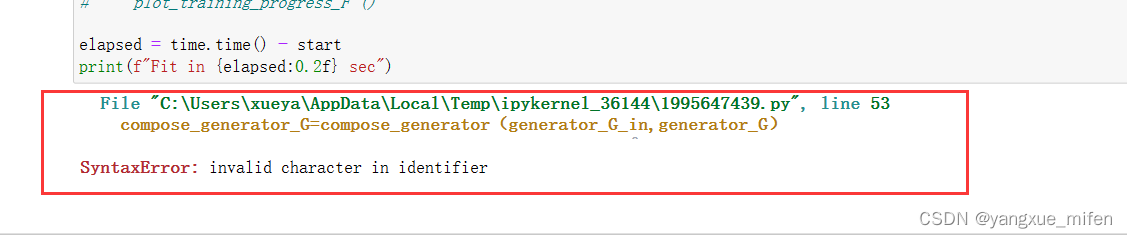

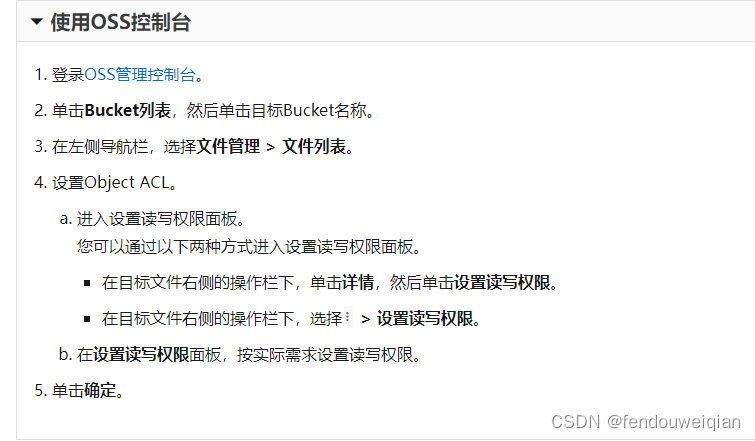

英思特提供了不同蚀刻剂特性之间的一般比较,并且讨论了适用于这种蚀刻工艺的掩模材料。我们采用自上而下的方法,使用有机或无机掩模,结合光刻方法(即剥离)、金属沉积和干法蚀刻,使我们能够获得良好控制的密度、直径、间距和空间位置。图1展示了使用6 m厚的光刻胶作为有机掩模材料在砷化镓晶片上图案化和转移测试几何图形的工艺流程图。然后将晶片切割成不同的样品,并针对不同的研究配方进一步设定成小批量(1cm2)。在蚀刻过程之后,垂直于沟槽轴劈开每个样品以观察它们的轮廓。

图1:砷化镓沟槽制造工艺流程图

图1:砷化镓沟槽制造工艺流程图

如图1b所示,我们观察到,当压力从10毫托(配方T2)升高到30毫托(配方T5)时,蚀刻速率(红色曲线)从1.8米/分钟逐渐增加到5.5米/分钟。较高压力下蚀刻速率的增加归因于活性氯物质浓度的增加,这增强了化学成分的蚀刻能力。与较低的压力相比,增加压力可以提高光刻胶掩模上的选择性(蓝色曲线)。在较高压力条件下,可以在砷化镓衬底上使用较薄的光致抗蚀剂层。后者简化了小尺寸转移掩模的光刻构图。

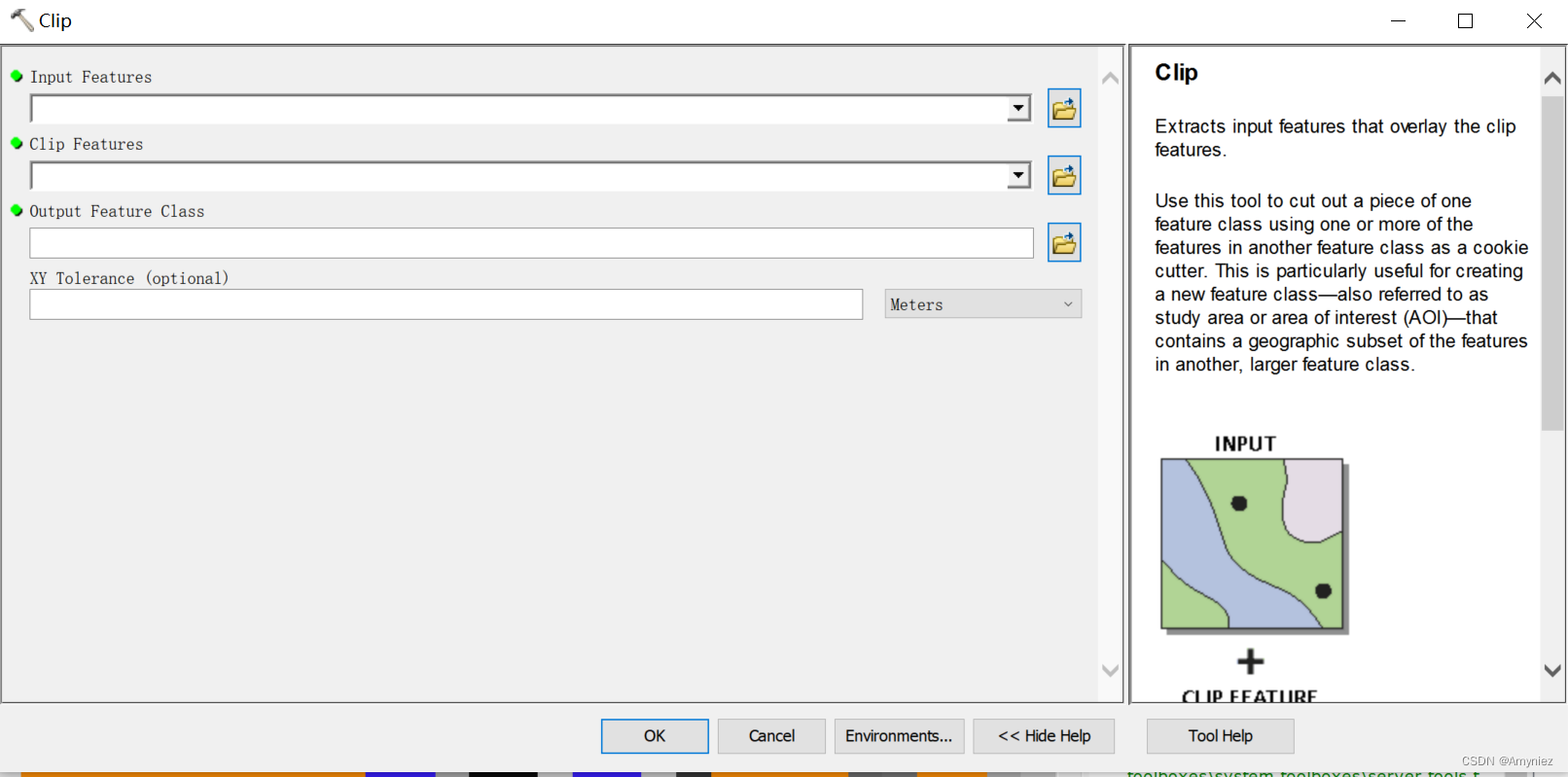

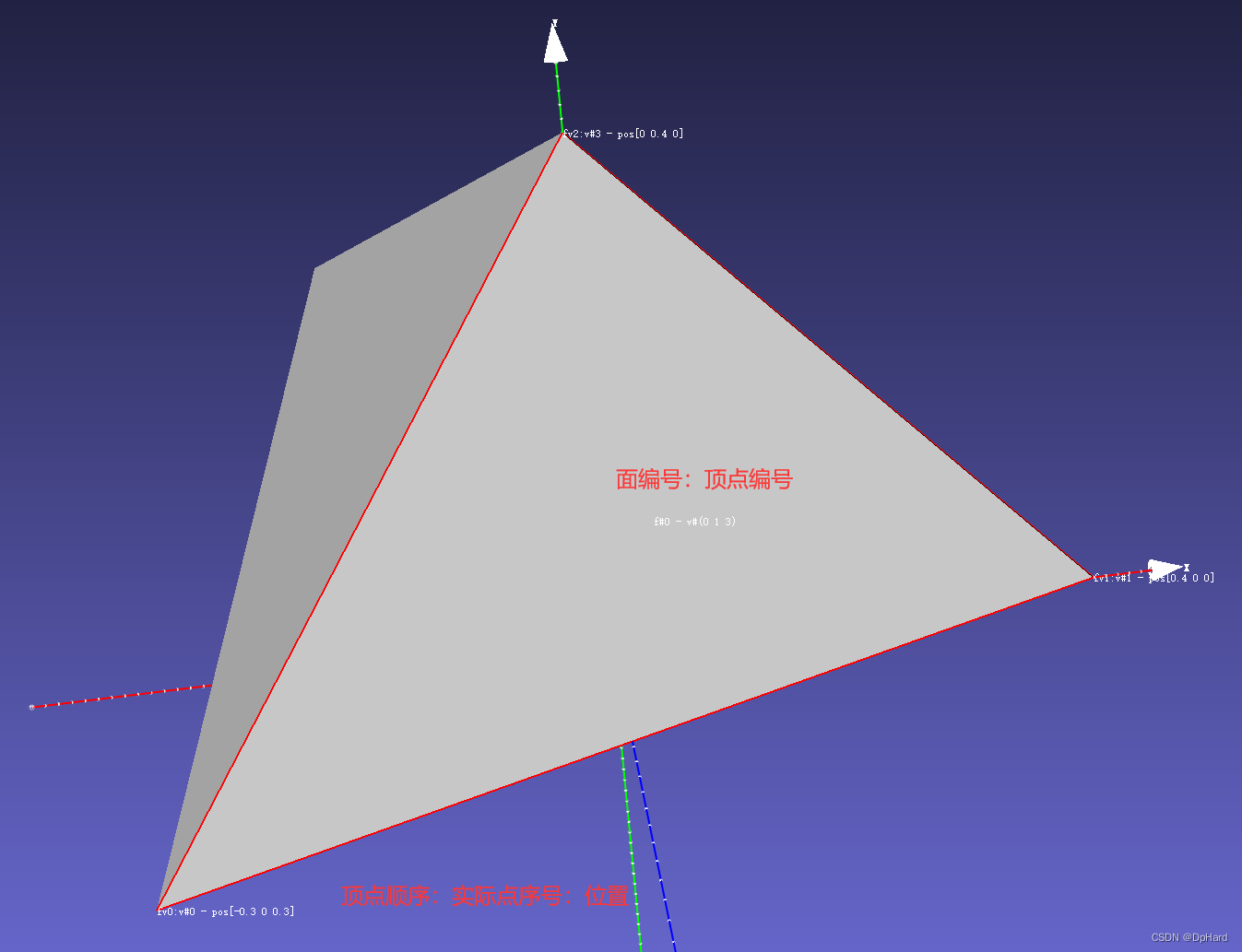

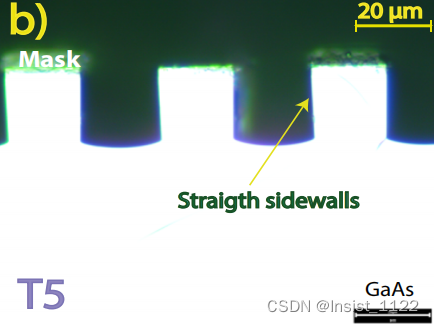

图2展示了不同工艺配方获得沟槽的横截面。我们观察到,弯曲效应对掩模开口尺寸很敏感,如图2a所示,并且如果气体混合物BCl3/Cl2的比率在20左右,则对于最大的掩模开口,弯曲效应得到改善。当压力增加到30毫托(T4)时,侧壁钝化恶化并出现弯曲效应。这个问题可以通过增加N2流速(T5)来限制,如图2b所示。工艺T5在30毫托,BCl3/Cl2比为20∶1,并添加5 sccm的N2气体,这适用于需要高纵横比和良好轮廓控制的微制造器件,因为该配方在侧壁上呈现低弯曲效应。该配方还具有提供高蚀刻速度和对抗蚀剂掩模的良好选择性的优点。一般来说,用光获得的抗蚀剂掩模光刻必须垂直转移。然而,在衬底顶部和抗蚀剂之间形成的侧壁角度从来不是完美的90度,抗蚀剂可能随着方向而凹陷活性蚀刻等离子体并暴露衬底脊的顶部,导致恶化(即粗糙)。为了避免侧壁粗糙,选择抗蚀剂厚度,使得在蚀刻过程中仅消耗一半的抗蚀剂。

图2:为两种工艺配方获得的沟槽的横截面

结论

利用英思特优化的BCl3/Cl2/Ar/N2等离子体化学条件,我们优化了砷化镓衬底在微米和纳米尺度上的ICP蚀刻工艺。对于要求直而光滑的侧壁的微器件制造,光致抗蚀剂掩模或Cr掩模比Ni掩模具有更好的效果。尤其是对于纳米尺度器件的制造,Cr掩模对于增加选择性以及降低表面粗糙度是必要的。本文的工作为利用III-V族半导体化合物实现微电子学、微系统和光电电子学中的各种应用的微器件和纳米器件铺平了道路。