PLA

一、PLA结构讲解

PLA是Aduc7126内部的可编辑逻辑阵列,Aduc7126总共有16个element,分为两组,如下图所示。

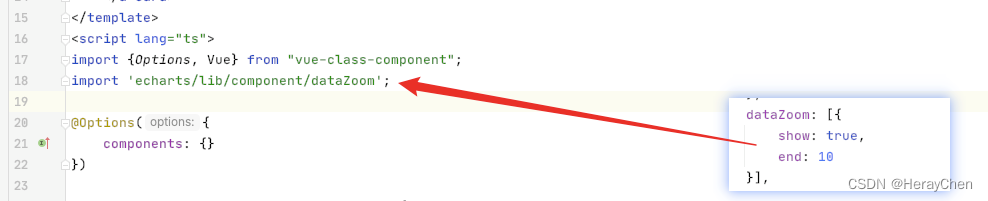

下图是PLA的其中一个element结构图,按照由左至右进行讲解:

- 左边MUX0、MUX1、MUX2、MUX3都是选择器,用于选择LUT的输入。各选择器特点如下:

- MUX0输入来自其他element

- MUX1输入来自其他element

- MUX2输入一个来自MUX0,一个来自PLADIN

- MUX3一个输入来自MUX1,一个来自外部引脚

- LUT总共有16中逻辑运算功能

- 然后是D触发器,D触发器的时钟可选,参考PLACLK寄存器,D触发器的作用个人理解是为了和外部时钟同步

- MUX4选择器用于选择LUT输出是否经过D触发器。

PS:1)PLA转换结果都保存在PLAOUT寄存器;2)PLALCK可以用于锁定PLADIN,使其不能修改

二、PLA其他功能

1、PLA中断

2、PLA作为ADC转换起始源

![[CSCCTF 2019 Qual] FlaskLight](https://img-blog.csdnimg.cn/49b4617587d44793b099b7c00a44ce59.png)