理想振荡器只有电感和电容,会一直振荡下去。但是实际的振荡器存在一定的寄生电阻并联在RC两端,会使振幅变小。因此需要RC旁边再并联一个负电阻以此来抵消寄生电阻的影响。一般会选择负阻提供的能量为寄生电阻能量的的2-3倍。如果负阻跟RC并联,那么负阻的阻值要<2-3倍寄生电阻阻值。如果负阻和RC串联,那么负阻的阻值要>2-3倍寄生电阻阻值。

下面讲如何通过仿真仿出RC网络寄生电阻和振荡频率的大小。

LC_VCO设计的核心是确定L和C的值。随着L值越大,其功耗也越大,相位噪声越好;C的值越大,相位噪声越小,功耗也越小。一般取f*L=5,先确定频率的值,然后根据频率确定L的值,再根据下式确定C的值。

取L为1nH,C为440fF,通过上式计算理论值为7.59GHZ

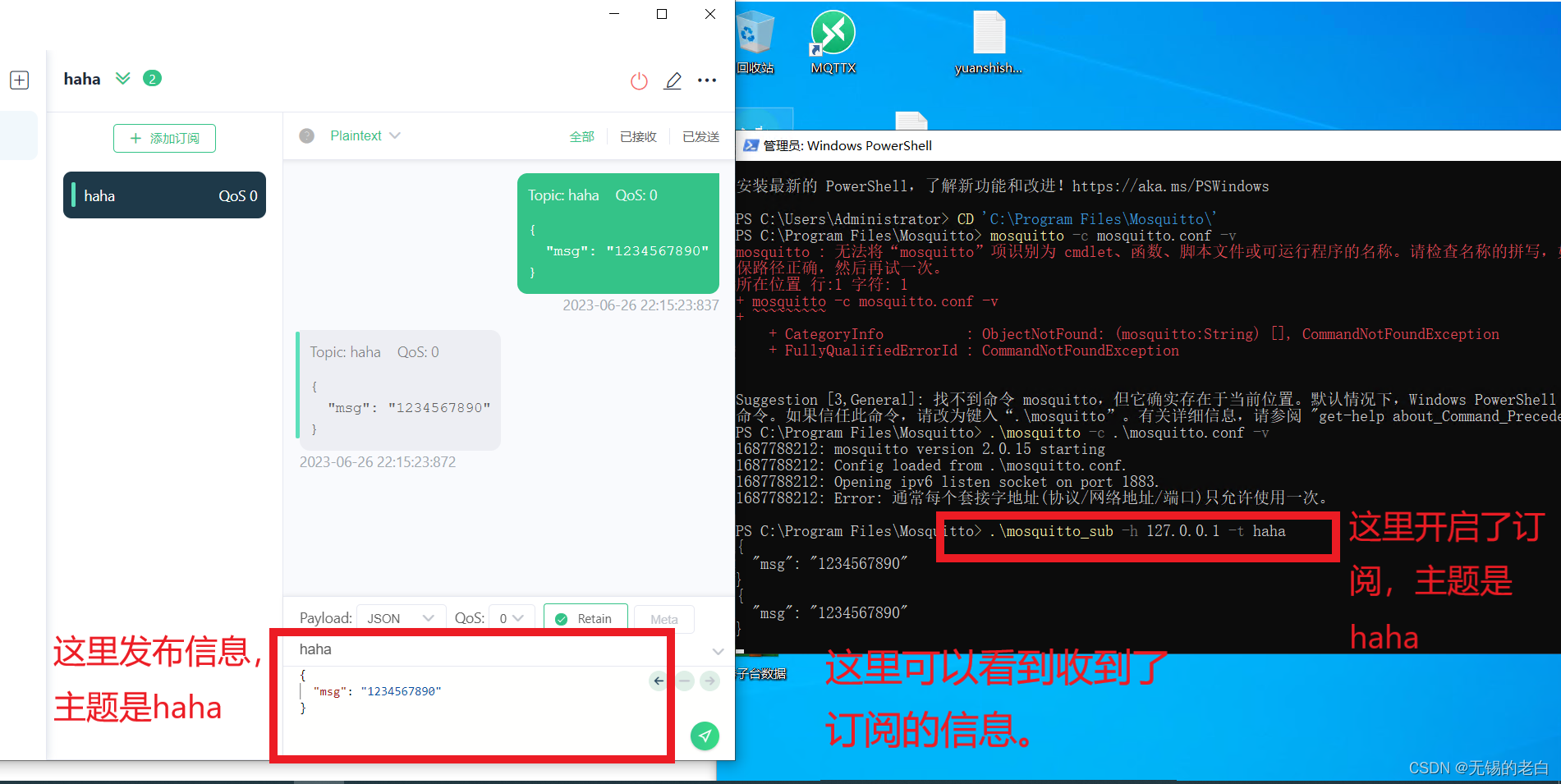

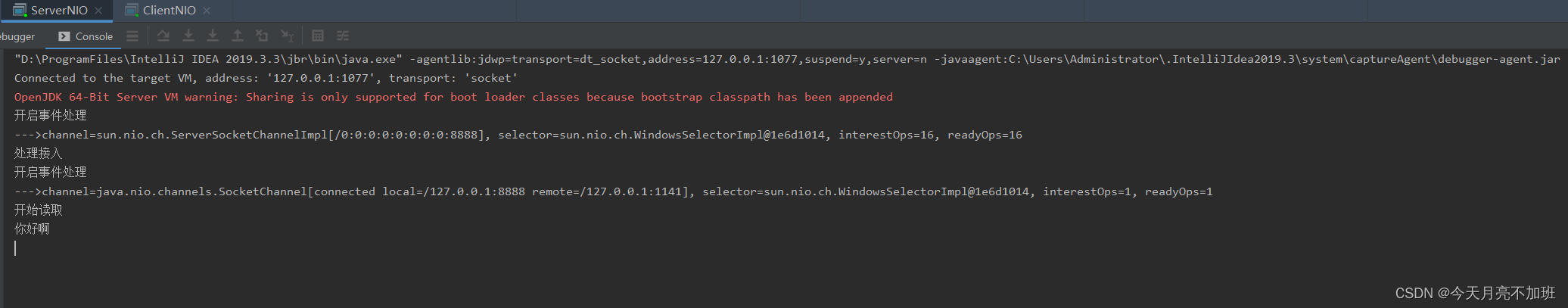

ADE仿真后,result-direct plot-main form,如下图,点击Z11

仿真结果f=7.66GHZ与理论结果差不多,寄生电阻 为2.23KΩ

仿真电感值和Q值

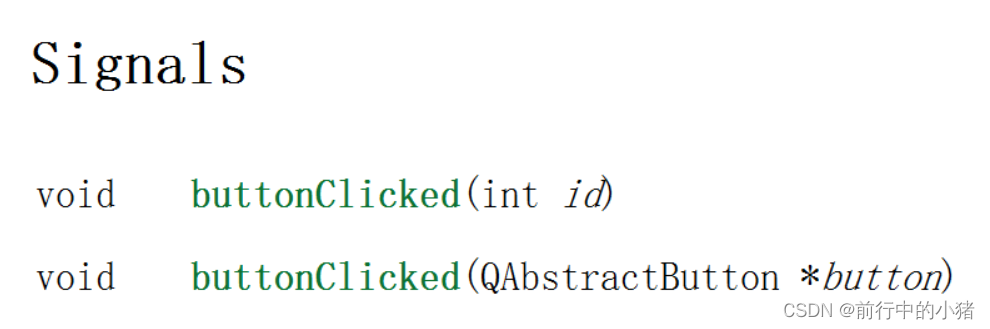

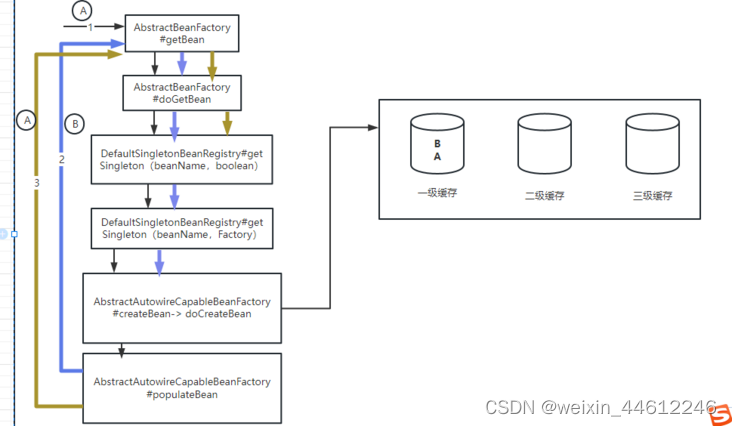

imag(Z)代表虚部,real(Z)代表实部。

仿真方法

上面右图imag为虚部,real为实部。计算公式如下图,xval函数为取横坐标

电感自谐振频率仿真

在电感上并联一个ac电流源仿ac仿真查看dB20

最常见的LC振荡器有两种:一种是带尾电流源的结构,一种是去掉尾电流源的结构。两种结构各有优缺点。带尾电流源的结构的LC振荡器,其功耗相对好控制,但其尾电流源的闪烁噪声,会通过差分对管的混频特性上变频变成相位噪声。解决的办法,通常是在尾电流源并联一个大电容,相当于提供一个低通滤波器的作用,电容大小的选取,要使低通滤波器的截止频率位于基波频率和2

之间。去掉尾电流源的结构,可以有效的克服尾电流源产生的相位噪声,但其缺点是降低了输出节点的阻抗。当差分信号相差大于一个

时,两个MOS管必然有一个进入线性区,使得差分信号有了一个到地的低阻抗通路存在,这样就会消耗电感电容振荡回路的Q值,从而恶化相位噪声。但在低压工艺下,我们一般选取没有尾电流的电路结构,因为信号的摆幅对相位噪声影响特别明显。