文章目录

-

- 概要

- 整体架构流程

- 技术名词解释

- 技术细节

- 小结

概要

提示:这里可以添加技术概要

例如:

实际运放与理想运放具有很多差别。理想运放就像一个十全十美的人,他学习100 分,寿命无限长,长得没挑剔,而实际运放就像我们每一个个体,不同的人具有不同的特点。要理解这些差别,就必须认识实际运放的参数.

整体架构流程

提示:这里可以添加技术整体架构

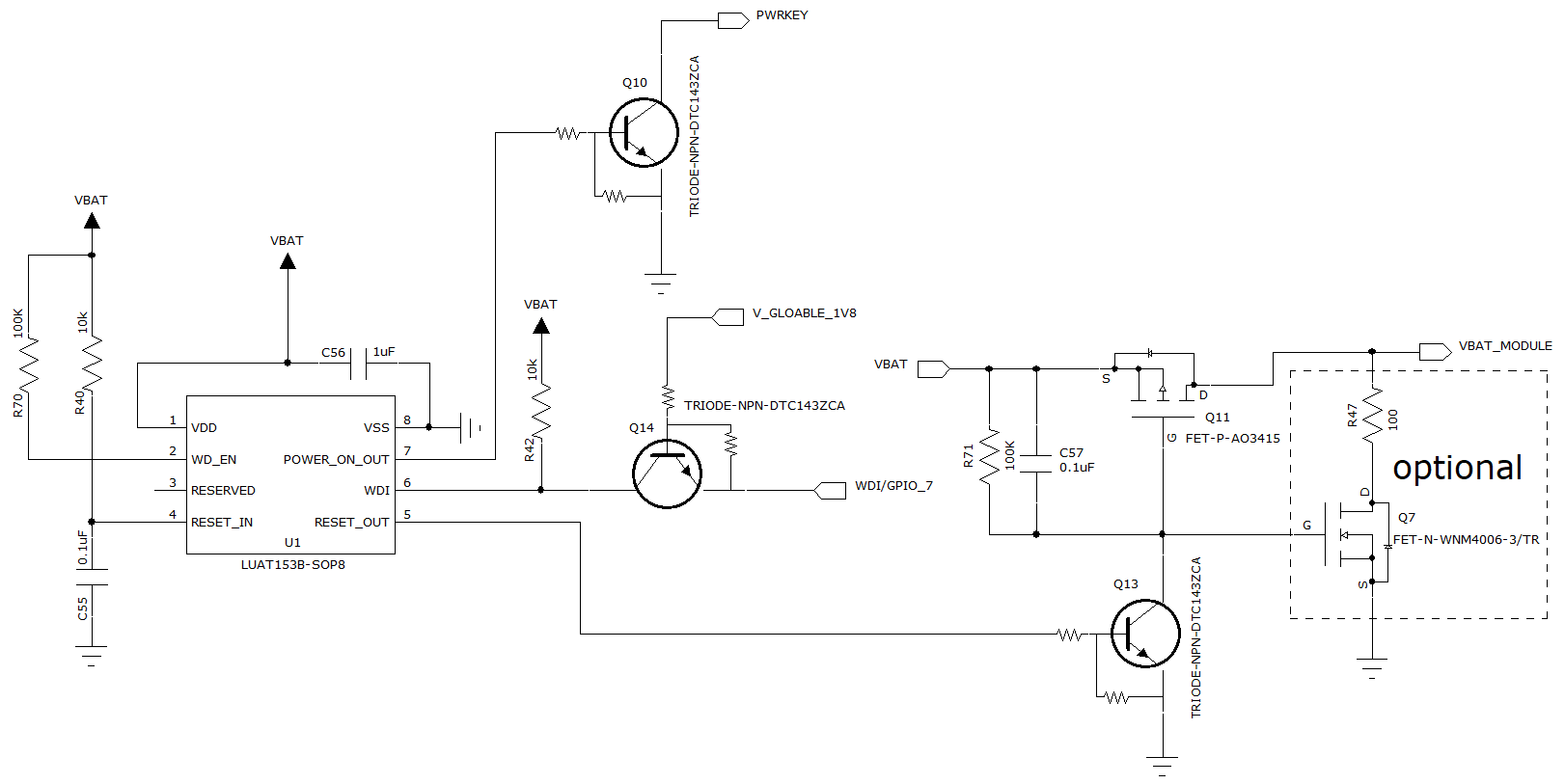

图是用于描述实际运放几个关键参数的等效模型。模型中,第一个黄色运放是一个近似的理想运放,只有A。不是无穷大,其余都是理想的。第二个运放是一个理想运放,它组成了一个电压跟随器。我们结合这个模型,由重要到次要,依序介绍运放的几个关键参数。

运放:运放是运算放大器的简称。在实际电路中,通常结合反馈网络共同组成某种功能模块。由于早期应用于模拟计算机中,用以实现数学运算,故得名“运算放大器”,此名称一直延续。运放是一个从功能的角度命名的电路单元,可以由分立的器件实现,也可以实现在半导体芯片当中。随着半导体技术的发展,如今绝大部分的运放是以单片的形式存在。现今运放的种类繁多,广泛应用于几乎所有的行业当中。

技术名词解释

1. -3db带宽

1.定义︰

运放闭环使用时,某个指定闭环增益(一般为1或者2、10等)下,增益变为低频增益的0.707倍时的频率。分为小信号(输出200mV以下)大信号(输出2V)两种。

2.理解∶

它直接指出了使用该运放可以做到的闭环放大电路的-3dB带宽。因为前述的两个参数,单位增益带宽和增益带宽积,其实都是对运放开环增益性能的一种描述,来自开环增益/频率图。而这个参数是对运放接成某种增益的放大电路实施实测得到的。

3.注意:

运放参数中一般不描述开环增益的-3dB带宽。

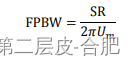

2.满功率带宽

1.定义︰

将运放接成指定增益闭环电路(一般为1倍),连接指定负载,输入端加载正弦波,输出为指标规定的最大输出幅度,此状态下,不断增大输入信号频率,直到输出出现因压摆率限制产生的失真(变形)为止,此频率即为满功率带宽。

2.理解∶

比-3dB带宽更为苛刻的一个限制频率。它指出在此频率之内,不但输出幅度不会降低,且能实现满幅度的大信号带载输出。

满功率带宽与器件压摆率密切相关︰

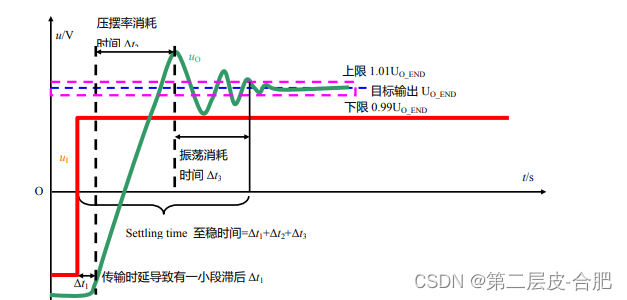

3.至稳时间

1.定义∶

运放接成指定增益(一般为1),从输入阶跃信号开始,到输出完全进入指定误差范围所需要的时间。所谓的指定误差范围,一般有1%,O.1%几种。

2.优劣范围︰

几个ns 到几个ms。

3.理解∶

至稳时间由三部分组成,第一是运放的延迟,第二是压摆率带来的爬坡时间,第三是稳定时间。很显然,这个参数与SR密切相关,一般来说,SR越大的,至稳时间更小。

对运放组成的ADC驱动电路,至稳时间是一个重要参数,越小越好。

传统中文资料中,将Settling time 译成建立时间,我个人认为译为“至稳时间”较好。Settle 的本意是沉淀到稳定、一个漂泊的人找到落脚点被安置好的意思,而Settling time本身的电学定义,也是指电路输出由一个稳态进入另一个稳态所需要的时间,它和“建立"一词,没有什么必然联系。

4.相位裕度

1.相位裕度定义∶

在运放开环增益和开环相移图中,当运放的开环增益下降到1时,开环相移值减去-180°得到的数值。

2.增益裕度定义︰

在运放开环增益和开环相移图中,当运放的开环相移下降到-18O°时,增益dB值取负,或者是增益值的倒数。

理解︰

相位裕度和增益裕度越大,说明放大器越容易稳定。

3.注意

的是,很多器件在描述开环特性时,在相位图中纵轴存在定义标注不完全一致的现象,有的是正度数、有的是负度数——不同的定义有不同的解释,都合理。但容易给读者造成混乱。我们需要知道的是,所有运放,在任何频率下,都只存在滞后相移,即相移为负值,图中右侧的红色标注即为相移。在极低频率处,相移接近于0°且小于0°,随着频率的上升,很快相移就进入到稳定的-90°,然后走向-180°甚至-270°。知道了这个规律,数据手册中无论怎么标注,你都能轻松应对了。

这样理解,相位裕度其实就是开环增益为OdB时的开环相移和-180°的距离。

技术细节

提示:这里可以添加技术细节

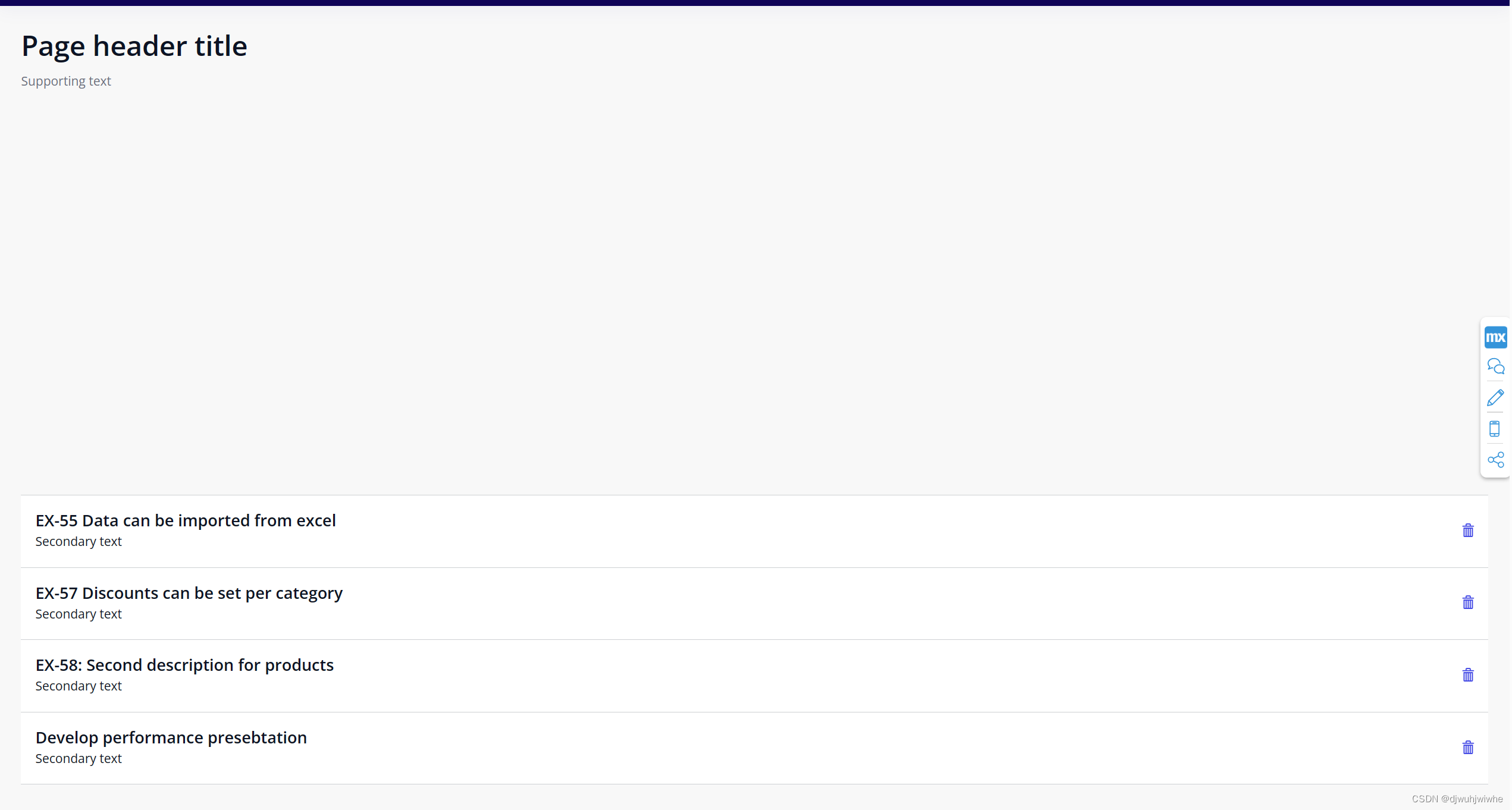

至稳时间示意图

小结

提示:这里可以添加总结

例如:

提供先进的推理,复杂的指令,更多的创造力。

![[Spec] WiFi P2P Discovery](https://img-blog.csdnimg.cn/bc493d70bc014342aba6759bbc154e46.png)