目录

概要

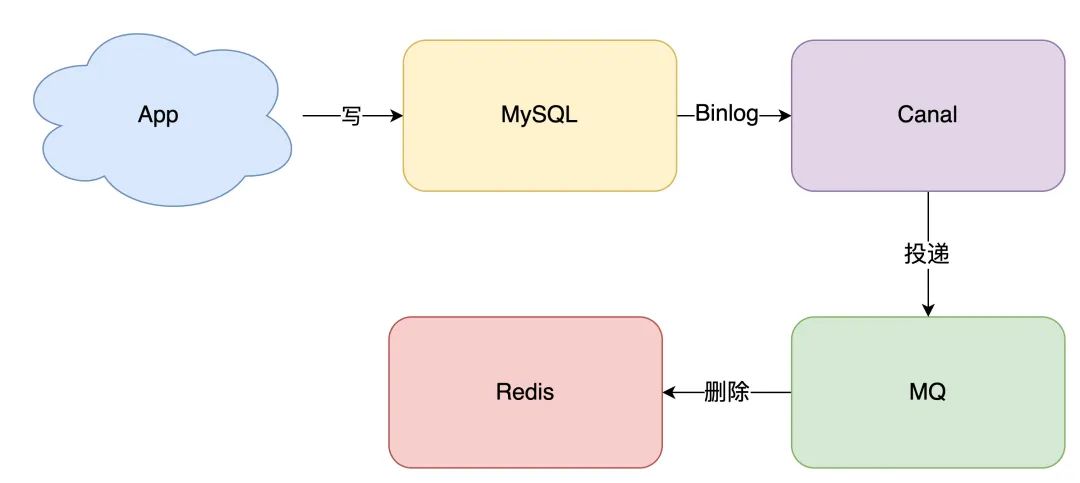

整体架构流程

技术名词解释

1.输入电压范围

2.优劣范围:

3.理解

技术细节

1.共模抑制比

2.优劣范围

3.理解

小结

概要

提示:这里可以添加技术概要

实际运放与理想运放具有很多差别。理想运放就像一个十全十美的人,他学习100 分,寿命无限长,长得没挑剔,而实际运放就像我们每一个个体,不同的人具有不同的特点。要理解这些差别,就必须认识实际运放的参数.

整体架构流程

提示:这里可以添加技术整体架构

图是用于描述实际运放几个关键参数的等效模型。模型中,第一个黄色运放是一个近似的理想运放,只有A。不是无穷大,其余都是理想的。第二个运放是一个理想运放,它组成了一个电压跟随器。我们结合这个模型,由重要到次要,依序介绍运放的几个关键参数

运放:运放是运算放大器的简称。在实际电路中,通常结合反馈网络共同组成某种功能模块。由于早期应用于模拟计算机中,用以实现数学运算,故得名“运算放大器”,此名称一直延续。运放是一个从功能的角度命名的电路单元,可以由分立的器件实现,也可以实现在半导体芯片当中。随着半导体技术的发展,如今绝大部分的运放是以单片的形式存在。现今运放的种类繁多,广泛应用于几乎所有的行业当中。

技术名词解释

提示:这里可以添加技术名词解释

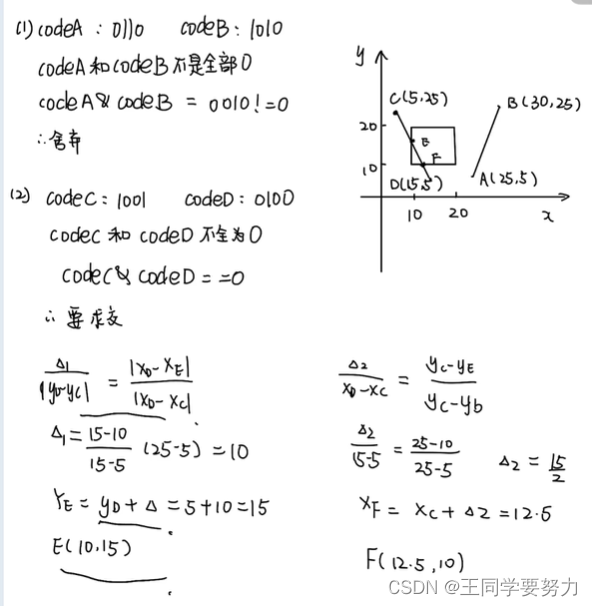

1.输入电压范围

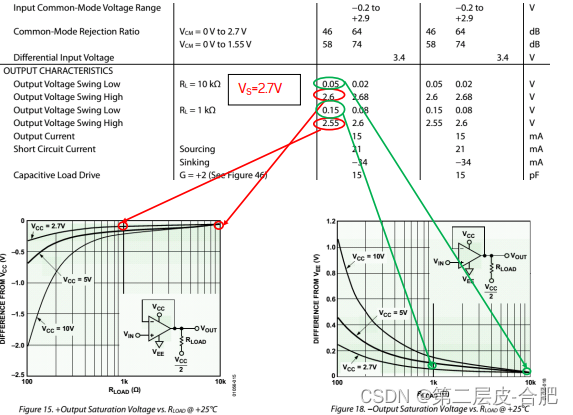

定义︰在给定电源电压和负载情况下,输出能够达到的最大电压范围。或者给出正向最大电压VOH以及负向最小电压VOL——相对于给定的电源电压和负载;或者给出与电源轨(rail)的差距。

2.优劣范围:

一般运放的输出电压范围要比电源电压范围略窄1Ⅳ到几V。较好的运放输出电压范围可以与电源电压范围非常接近,比如几十mV的差异,这被称为“输出至轨电压。这在低电压供电场合非常有用。当厂家觉得这个运放的输出范围已经接近于电源电压范围时,就自称"输出轨至轨”,表示为Rail-to-rail output,或 RRO。

3.理解

在没有额外的储能元件情况下,运放的输出电压不可能超过电源电压范围,随着负载的加重,输出最大值与电源电压的差异会越大。这需要看数据手册中的附图。

输出电压范围,或者输出至轨电压有如下特点︰

正至轨电压与负至轨电压的绝对值可能不一致,但一般情况下数量级相同;至轨电压与负载密切相关,负载越重(阻抗小)至轨电压越大;

至轨电压与信号频率相关,频率越高,至轨电压越大,甚至会突然大幅度下降;至轨电压在20mV以内,属于非常优秀。

图摘供电的80MHz,RRIO(输入输出均轨至轨)放大器AD8031。其输入范围超出了电源O-2.7V),为-0.2V-29V,输出非常接近电源,为0.02v到2.68V,仅有20mV的至轨电压。

技术细节

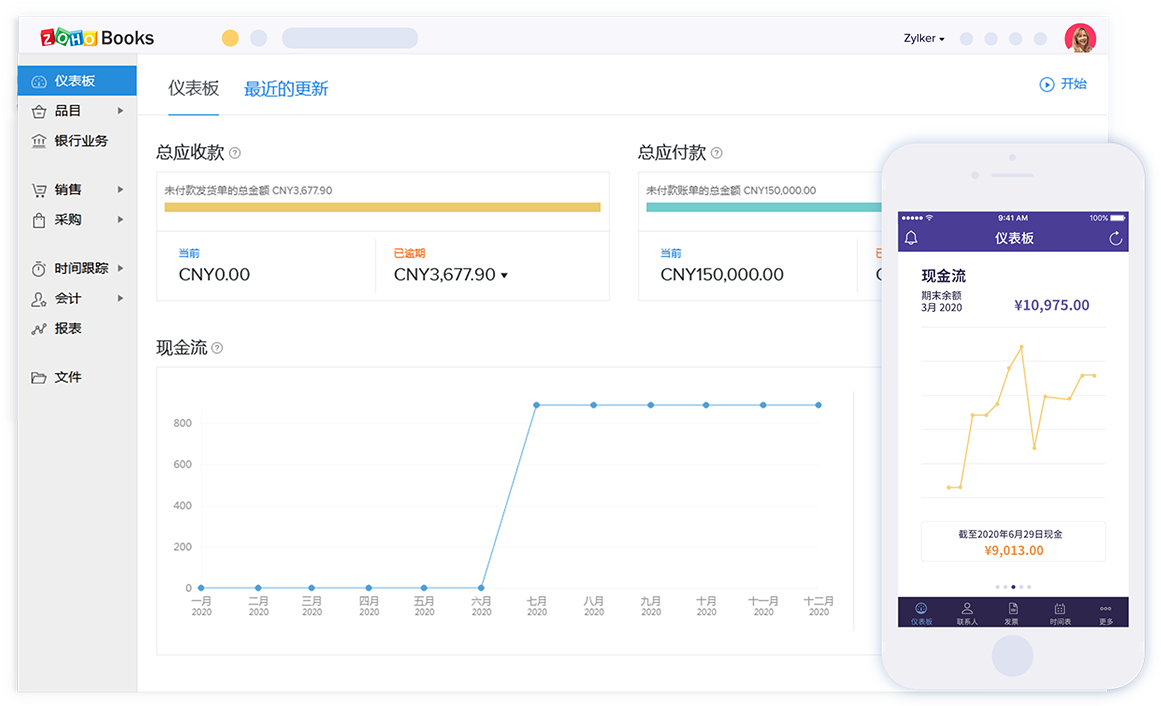

1.共模抑制比

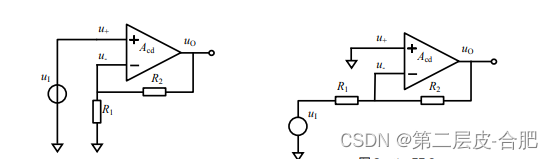

定义∶运放的差模电压增益与共模电压增益的比值,可以用倍数表示,也可用db表示。

为了说明差分放大电路抑制共模信号及放大差模信号的能力,常用共模抑制比作为一项技术指标来衡量,其定义为放大器对差模信号的电压放大倍数Aud与对共模信号的电压放大倍数Auc之比,称为共模抑制比,英文全称是Common Mode Rejection Ratio,因此一般用简写CMRR来表示,符号为Kcmr,单位是分贝db。

差模信号电压放大倍数Aud越大,共模信号电压放大倍数Auc越小,则CMRR越大。此时差分放大电路抑制共模信号的能力越强,放大器的性能越优良。当差动放大电路完全对称时,共模信号电压放大倍数Auc=0,则共模抑制比CMRR→∞,这是理想情况,实际上电路完全对称是不存在的,共模抑制比也不可能趋于无穷大。

2.优劣范围

优劣范围:一般运放都有60dB以上的CMRR,高级的可达140dB以上.

3.理解

此式为共模增益、差模增益对输出影响的标准式,也是CMRR对电路产生影响的根源。一般情况下,差模增益远大于共模增益,即 CMRR很大,导致用户一般不需要考虑共模增益对输出的影响。

当CMRR不是无穷大时,共模增益的存在,对反相比例器产生的效果等同于开环增益下降。分母和分子中是同时变化的,这与同相比例器不同。

细致分析,可以认为CMRR不是无穷大,或者共模增益的存在,对同相比例器的影响要大于对反相比例器的影响。但总体来说,这点影响是微乎其微的。

小结

提示:这里可以添加总结

影响减法电路共模抑制比的因素有两个,第一是运放本身的共模抑制比,第二是对称电路中各个电阻的一致性。其实更多情况下,实现这类电路的高共模抑制比,关键在于外部电阻的一致性。此时,分立元件实现的电路,很难达到较高的 CMRR,运放生产厂家提供的差动放大器就显现出了优势。

![[RocketMQ] Consumer消费者启动主要流程源码 (六)](https://img-blog.csdnimg.cn/70d00419aa744d6a8f7bfe8c684a47d7.png)