一、项目整

这是我们做过的一个项目,若有需求,请联系我。开放PCB和软件技术。

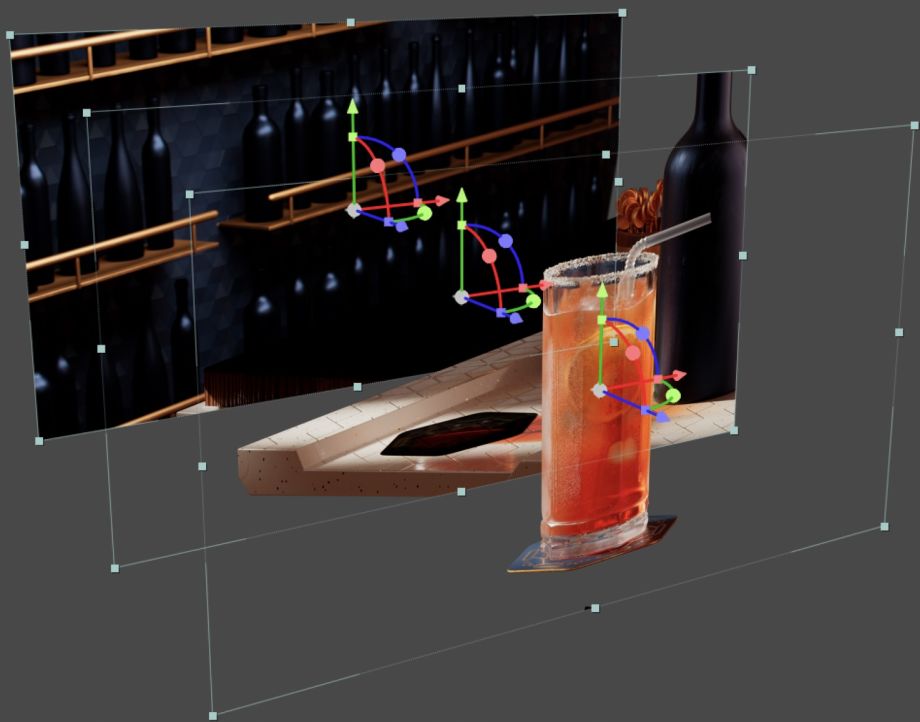

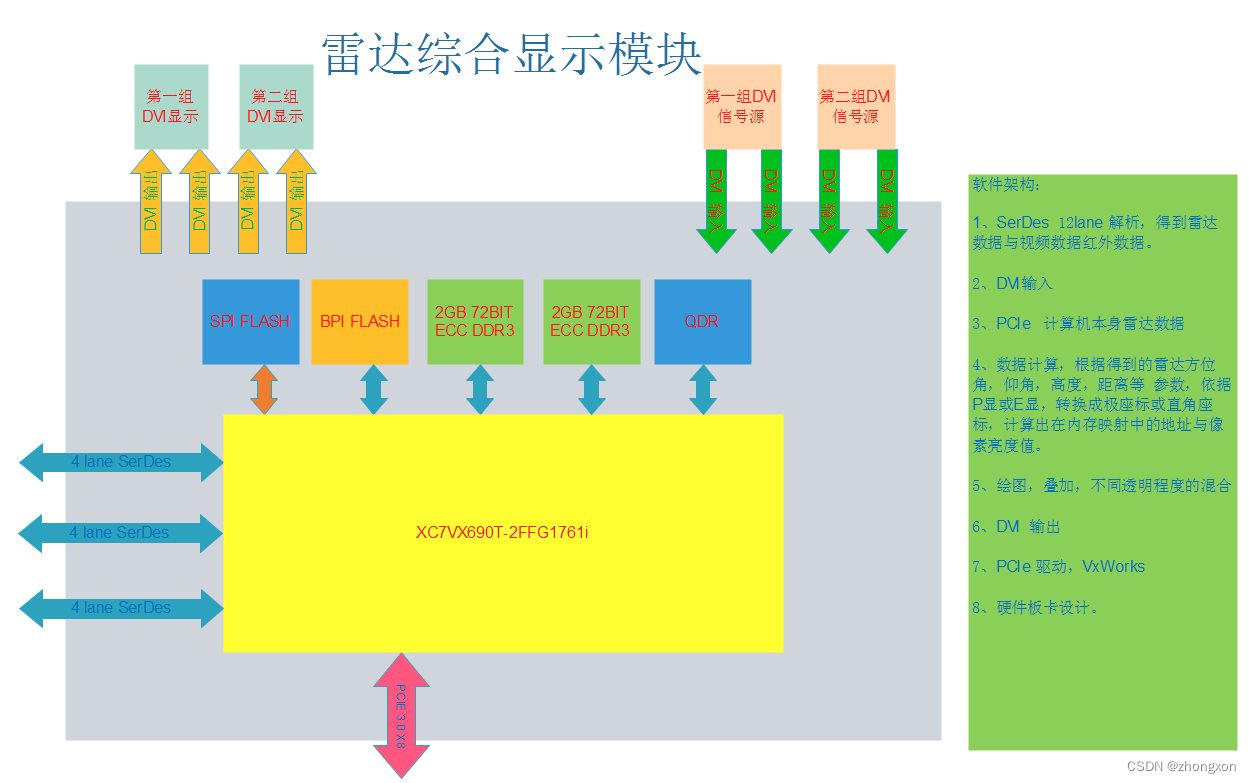

以FPGA为核心,开发设计具有多路图像/视频采集、处理、传输、显示等功能的嵌入式视频模块。可对多路SerDes接口输入的高速串行视频流数据进行解析,将解析出的雷达、红外及可见光图像视频与显卡DVI输出的图形视频进行融合,实现图形、雷达、红外及可见光图像等多种视频的综合显示。对外接口包括12路SerDes输入/输出,4路DVI输入和4路DVI输出,以及一个x8 的PCIe3.0 接口,上位机采用 VxWorks系统。

二、显示界面描述

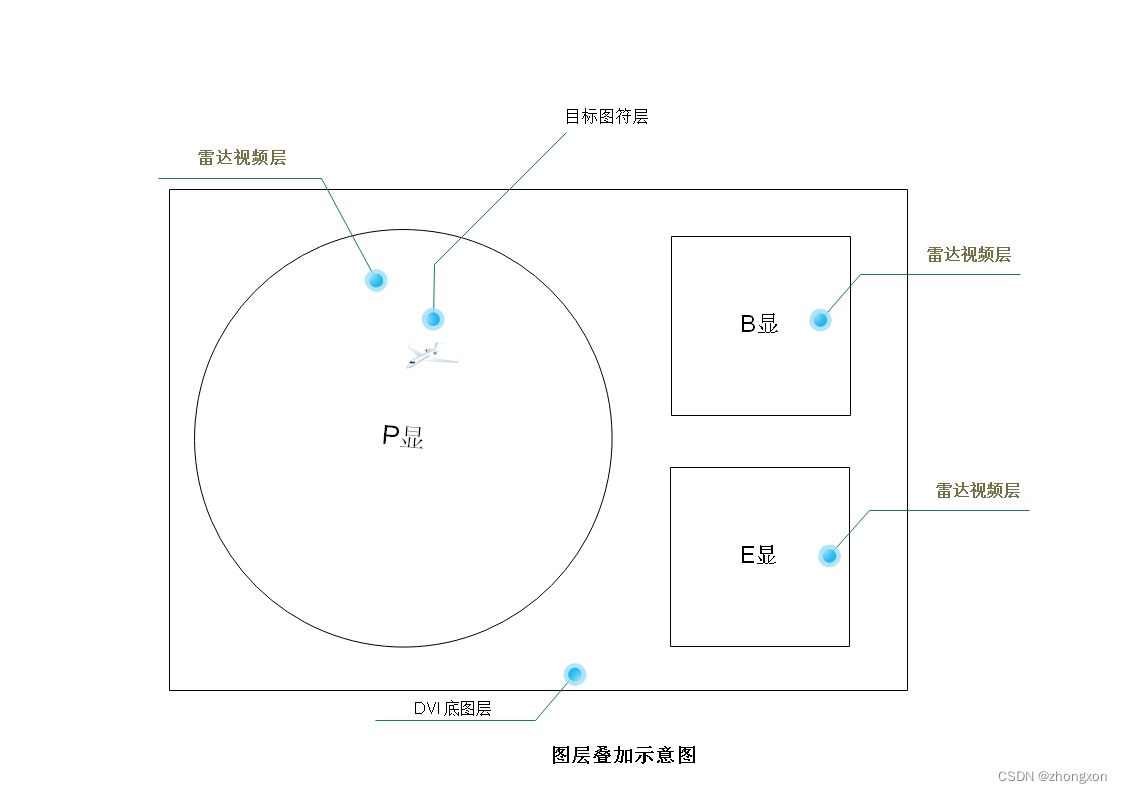

1.支持不少于3层的多图层、多窗口的图形与图像视频的透明/混合叠加显示;

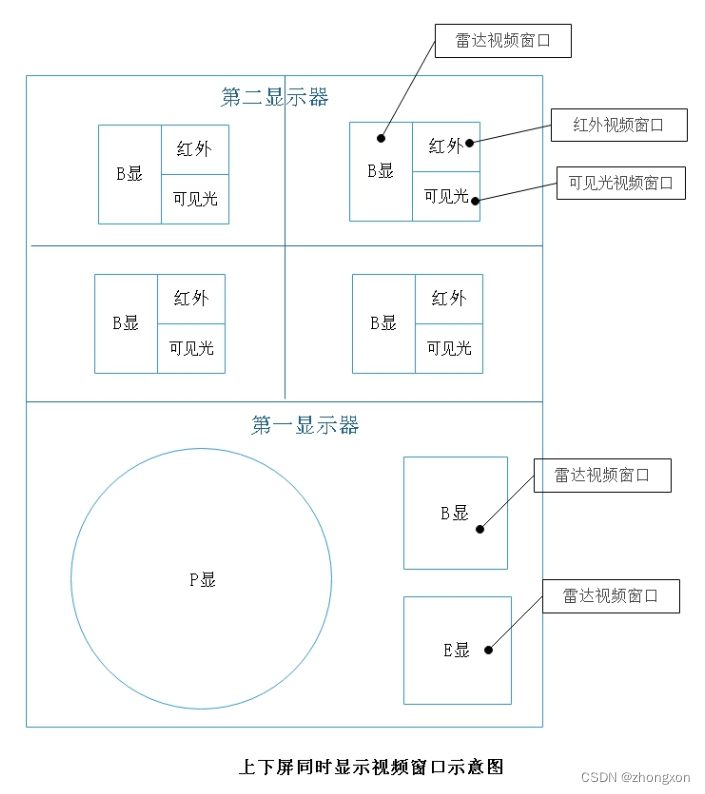

2.支持最多15个视频窗口同时双屏显示;

3.窗口显示位置及尺寸可调整,视频窗口间的遮挡关系可设置;

4.各窗口在上下屏均可显示,同一窗口不跨屏显示,第一显示器与第二显示器可同时自由组合显示视频窗口;

5. 第一显示器与第二显示器的界面(含图像和视频)可任意切换;

三、雷达视频的显示要求

1. 支持4路雷达视频(382改雷达S/C阵面、364改雷达H/I阵面)接入,且支持382改雷达和364改雷达双阵面的同窗显示;

2. 视频源及扫描线的颜色可调;

3. 显示方式:支持P显、B显、E显,显示窗口位置、大小可调;

4. 量程控制:支持多种量程显示;

5.余辉:支持P显、B显、E显的余辉功能,可通过设置从最亮到最暗的衰减时间控制余

辉快慢;

6. 支持雷达视频的偏心显示;

7. 支持雷达视频的时戳提取;

8. P显分辨率支持1000*1000,B显/E显分辨率支持800*800;

四、红外、可见光显示要求

1. 支持6路红外视频和5路可见光视频输入;

2. 支持图像视频缩放;

3. 支持输入视频最高分辨率1024*1024;

4. 显示窗口位置、大小可调;

5. 支持红外图像视频以任意方位角为中心放大显示,显示范围可调。

五、状态监控

1. 可输出本模块上雷达、可见光以及二次图形等功能模块的工作状态信息:

2. 可测试/监视本模块的电压、温度等信号。

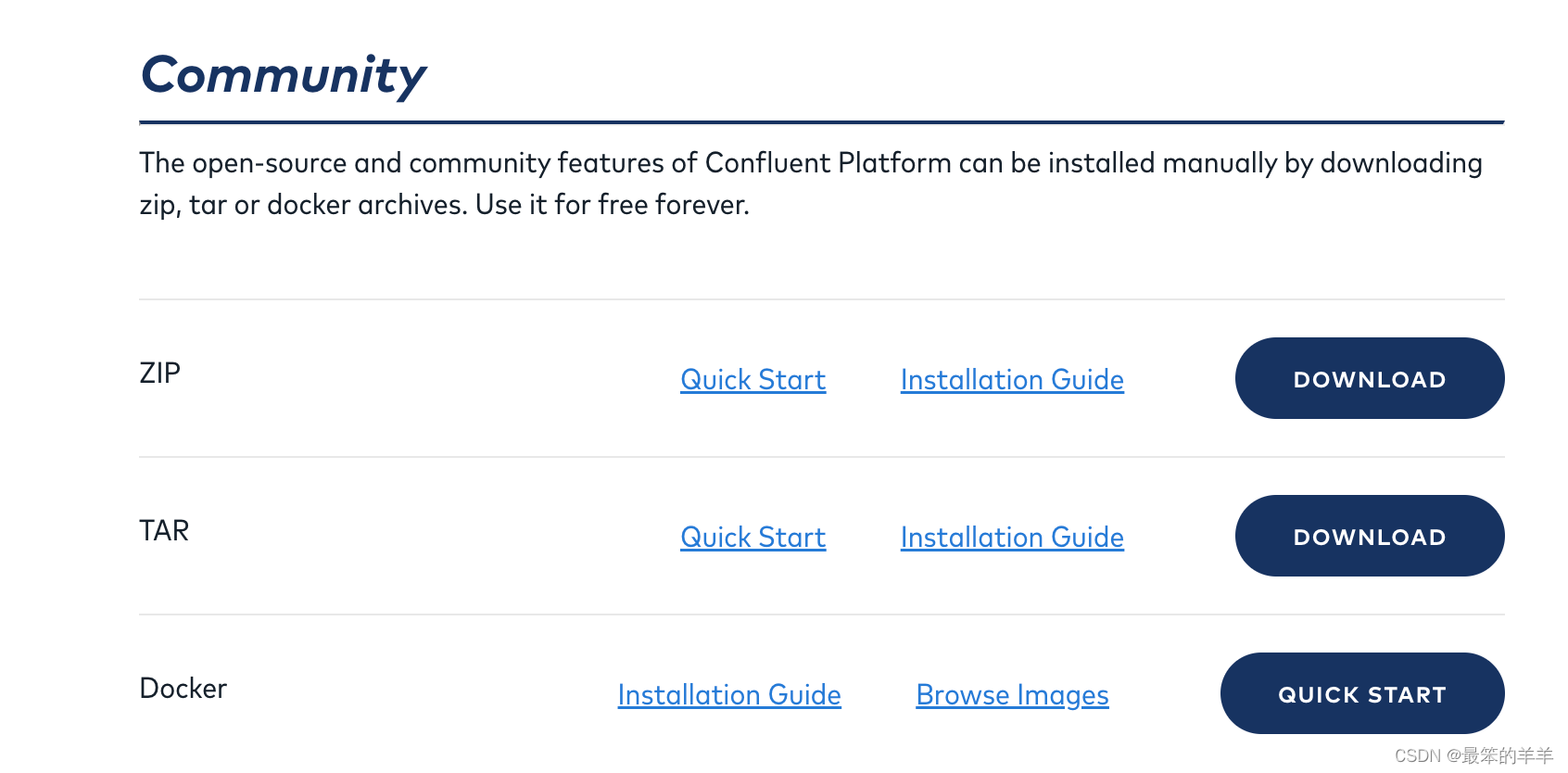

六、硬件的实现

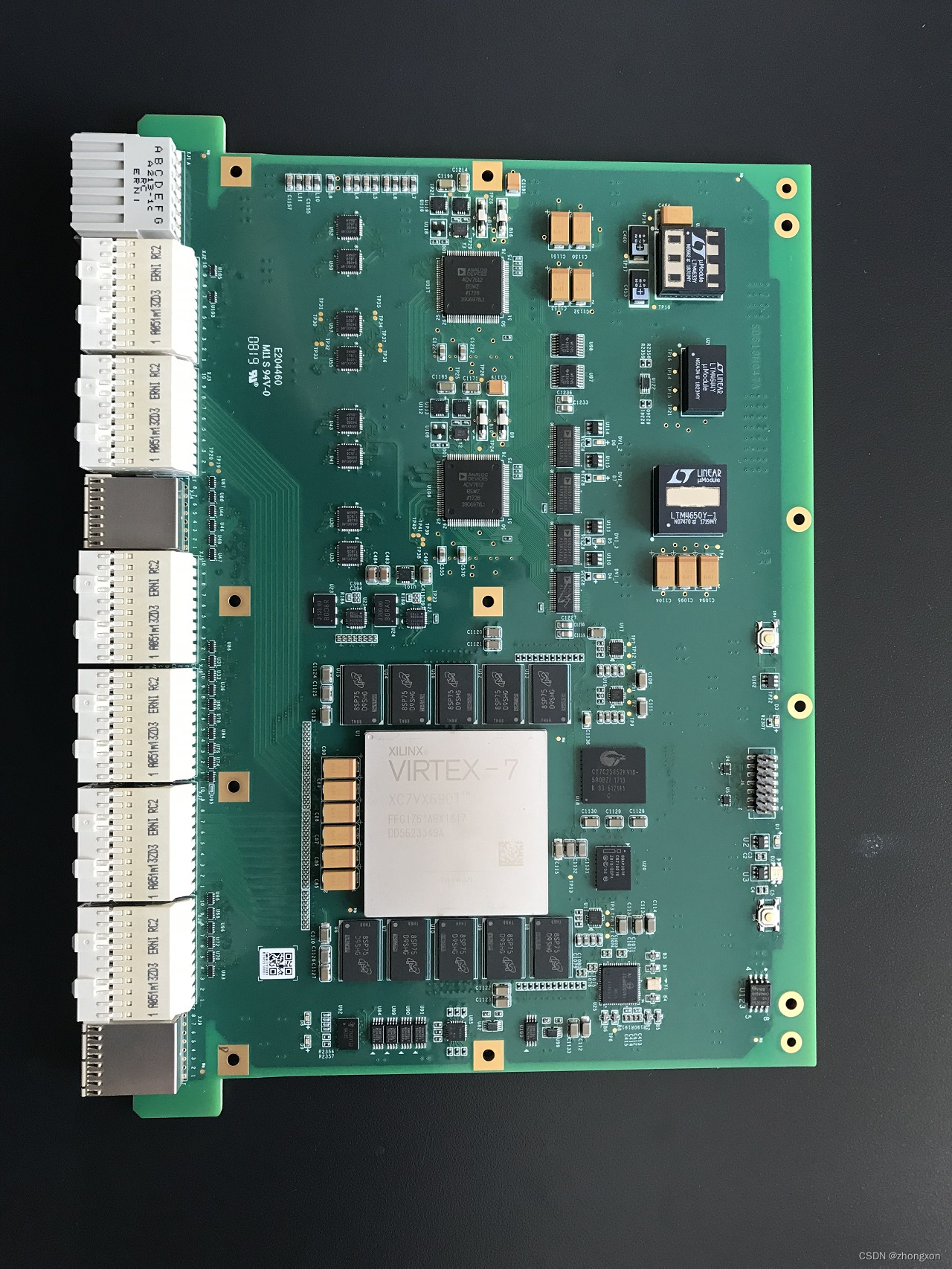

板卡采用6U CPEX 架构,尺寸为233mm X 160mm。

硬件框图如下:

1、选用大规模XILINX FPGA XC7VX690T-2FFG1761i,有693120 个Logic Cells,有Block RAM 52920kb,有DSP Slices 3600,有9个MGT Bank。应该足够本项目使用。

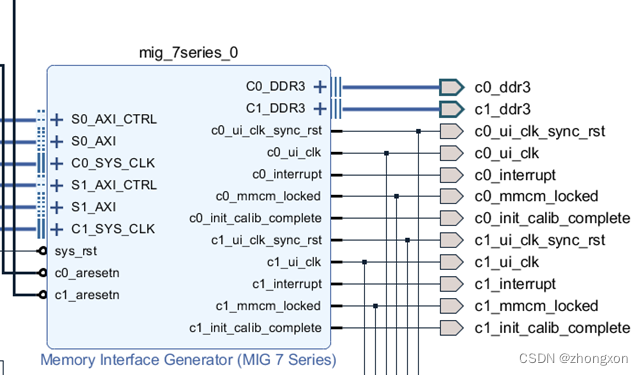

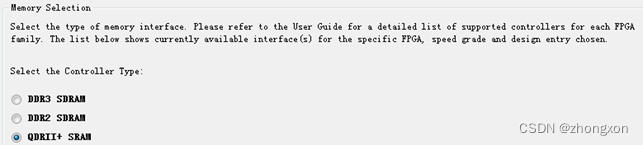

2、4GB双通道72bit DDR3与72Mbit QDR存储架构,能比较妥善合理的解决大量图像视频数据的读写,采集,处理,与输出。频繁的随机读写的数据可以存放在QDR中。

3、SPI Flash,存放断电后需要保留的参数。

4、BPI Flash 存放的就是FPGA本身的程序,或者需要动态加载应用程序时的引导程序。

5、12路SerDes,接收雷达数据与红外、视频图像数据。

-

-

-

- 接口标准:CML接口

- 耦合方式:交流耦合

- 耦合电容放置位置:接收端

- 发送端差分电平:450mV~800mV

- 接收端差分电平:100mV~1200mV

- 速率:4.0Gbps(推荐板载时钟100MHz)

- 编码方式:8B/10B

- 同步码:K28.5

-

-

6、4路DVI 采集,直接用FPGA的LVDS引脚,前端加LVDS接收缓冲类的芯片。

-

-

-

- 标准TMDS电平信号

- 分辨率1600*1200

- 2组4路(二选一)DVI输入

-

-

7、4路DVI输出,直接用FPGA引脚加CML到TMDS驱动芯片。

-

-

-

- 标准TMDS电平信号

- 分辨率1600*1200

- 2组(4路)同源DVI显示输出

-

-

8、PCIe Gen3 X8接口。直接利用FPGA的硬核,XC7VX690T每片内有3个这样的核。支持DMA数据传输。

9、电源接口

电源输入:DC12V+-5%,DC5V+-5%

功耗<70W

MTBF不小于50000h;

MTTR < 0.5h

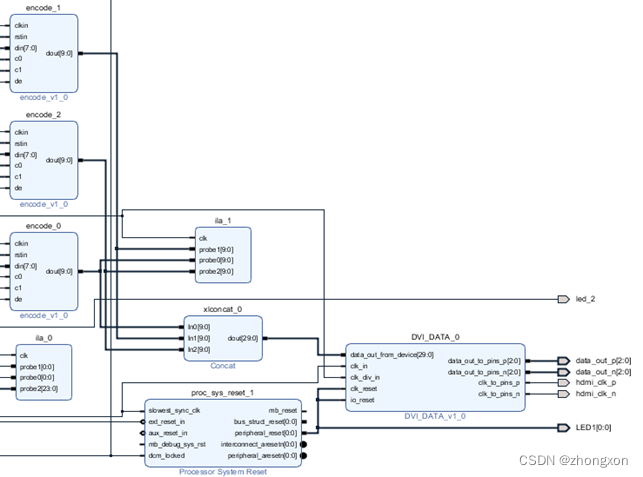

七、软件的实现

1、采用软核MicroBlaze核作为系统控制。

2、DDR3控制器

3、QDR控制器

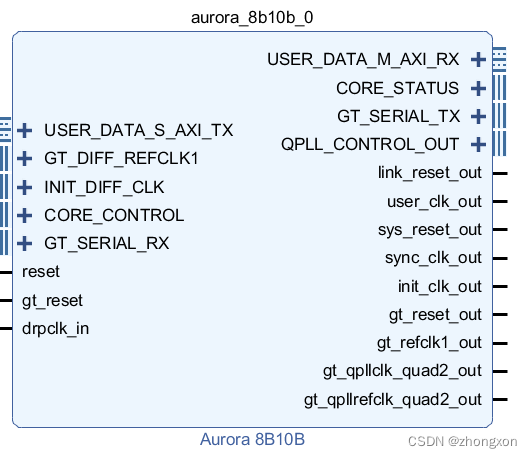

4、SerDes 通信

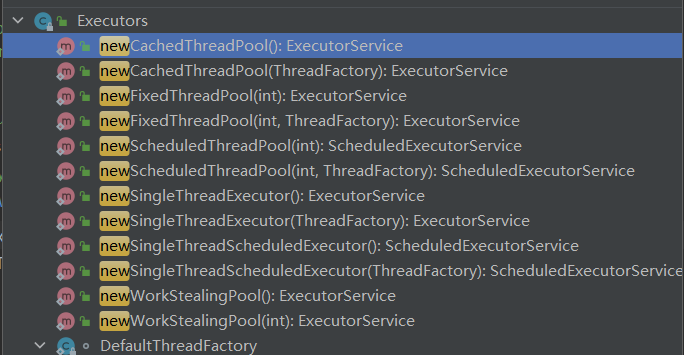

例化3个这样的IP core,每个核4个lane,三个核共12个lane。完成雷达数据,红外数据,可见光图像数据的接收(收发)。数据解析需要Verilog编程实现。

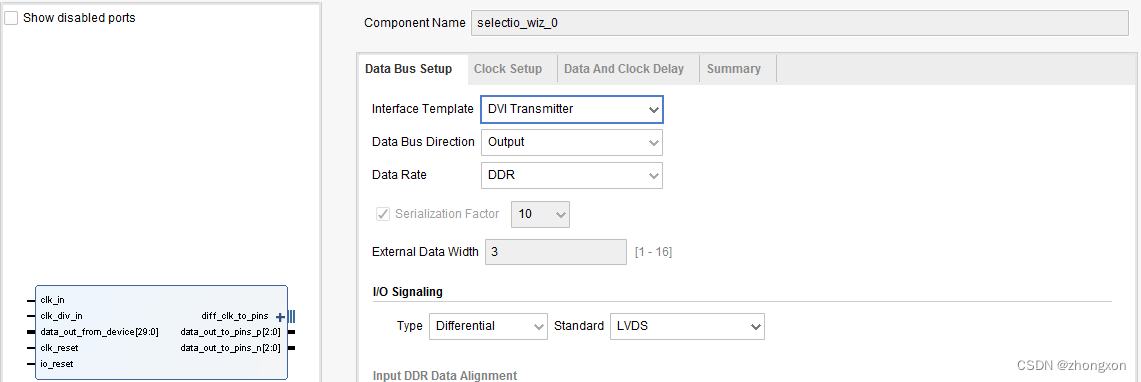

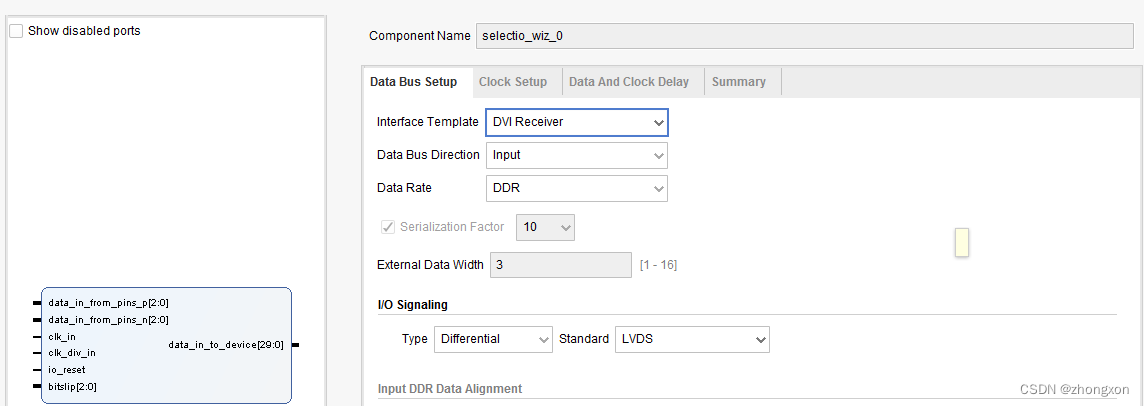

5、DVI收发

DVI 的 Transmitter与 Recvier可以直接利用XILINX 的IP CORE 。而编码与解码部分用Verilog编写程序。就是图中的encode。

八、软件要求

操作系统:支持VxWorks6.8.2

驱动:支持PCIe 3.0

![NSSCTF MOBILE [SWPU 2019]easyapp 详细题解](https://img-blog.csdnimg.cn/b0a20cb2d66840eab40f720d333a3afe.png)