文章目录

- SCTRL_ELx 介绍背景

- ARMv8 SCTLR_ELx 介绍

- ARMv9 SCTLR_ELx 介绍

SCTRL_ELx 介绍背景

由于在做DFD 测试过程中需要测试 EL1 状态下的 self-hosted trace 功能,但是这个测试是在UEFI中做的,在开发验证阶段UEFI默认是运行在EL3 下的,所以如果要完成测试就需要从EL3跳转到EL1, 由于在查找EL3 跳转到EL1的汇编代码时,发现ARMv8和ARMv9下两者在 SCTRL_EL3的配置是有差异的,所以就引入了下文对 SCTRL_ELx的介绍。

首先看下 ARMv8/ARMv9 从 EL3 跳转到 EL1 的汇编代码:

ARMv8:

mrs x0, scr_el3

orr x0, x0, #(0x1 << 15) // 设置 SCR_EL3 的 HCE 位为 1

msr scr_el3, x0

mov x0, #(0x3 << 22) // 设置 SPSR_EL3 的 M[4:0] 位为 0b11011,即 EL1h 模式

msr spsr_el3, x0

adr x0, el1_entry_func // 设置 x0 寄存器为 EL1 的入口地址

msr elr_el3, x0 // 将 EL1 的入口地址存入 ELR_EL3

eret // 执行 ELRET 指令,跳转到 EL1

el1_entry_func:

// Set up TRBE

MOV w0, #0

LDR x0, =TRBE_BASE_ADDRESS // BASE=0x90000000 Trace Buffer Base pointer address

MSR TRBBASER_EL1, x0

ARMv9:

mrs x0, sctlr_el3

orr x0, x0, #(0x1 << 28) // 设置 SCTLR_EL3 的 EE 位为 1

msr sctlr_el3, x0

mov x0, #(0x1 << 3) // 设置 HCR_EL2 的 RW 位为 1,使得 EL2 可以访问所有寄存器

msr hcr_el2, x0

mov x0, #(0x3 << 0) // 设置 CPTR_EL2 的 TFP、TCM、TWE 和 TCP 位为 0b1111,使得 EL2 可以访问所有 CP15 寄存器

msr cptr_el2, x0

mov x0, #(0x3 << 2) // 设置 SCR_EL3 的 RES1[2:0] 位为 0b011,即禁用 EL3 的访问权限检查

msr scr_el3, x0

adr x0, el1_entry_func // 设置 x0 寄存器为 EL1 的入口地址

msr elr_el3, x0 // 将 EL1 的入口地址存入 ELR_EL3

eret // 执行 ELRET 指令,跳转到 EL1

el1_entry_func:

// Set up TRBE

MOV w0, #0

LDR x0, =TRBE_BASE_ADDRESS // BASE=0x90000000 Trace Buffer Base pointer address

MSR TRBBASER_EL1, x0

ARMv8 SCTLR_ELx 介绍

armv8 架构中,SCTLR_ELx 寄存器是系统控制寄存器,用于控制系统的运行状态和特性。它包含了多个位域,每个位域控制某个特定的系统行为。以下是一些常见的位域及其功能:

- M: 控制系统的运行模式,0表示使用AArch32模式,1表示使用AArch64模式。

- C: 控制缓存的使能和行为。

- I: 控制指令缓存的使能和行为。

- A: 控制对齐检查的行为。

- D: 控制数据缓存的使能和行为。

- Z: 控制EL0使用的异常向量表。

armv9 架构中的 SCTRL_ELx 寄存器与armv8架构中的类似,但有一些新的位域,如:

- EE: 控制异常的使能和行为。

- UCE: 控制对未缓存的内存的访问。

- FPE: 控制浮点异常的行为。

- E0E: 控制EL0的异常向量表。

- EAE: 控制对齐检查的行为。

- WXN: 控制可执行代码的写保护。

总的来说,SCTLR_ELx 寄存器是非常重要的系统控制寄存器,它可以控制系统的运行模式、缓存的行为、对齐检查和异常的行为等。在系统的启动过程中,操作系统会初始化 SCTLR_ELx 寄存器的各个位域,以确保系统的正常运行。

ARMv9 SCTLR_ELx 介绍

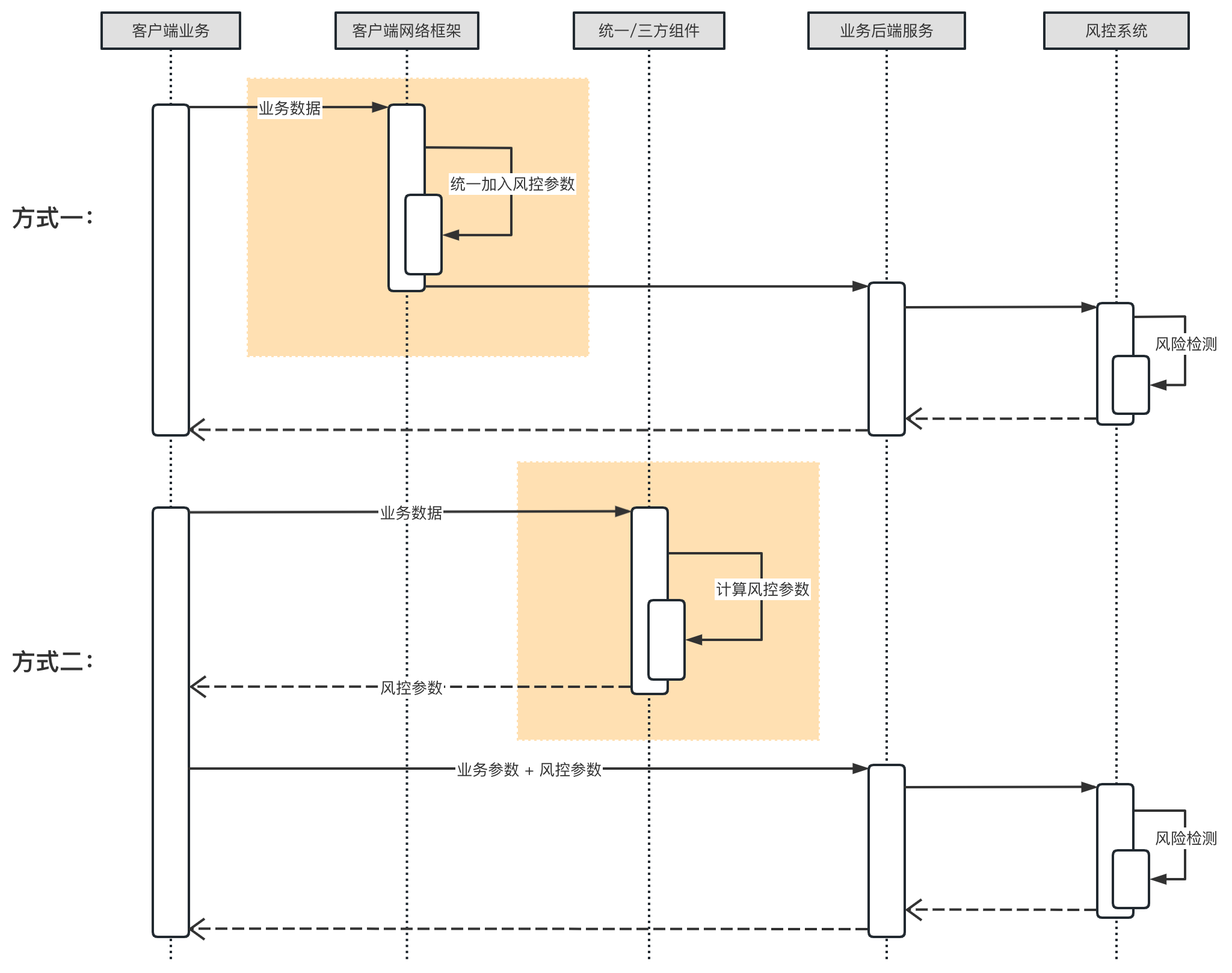

ARMv9 中的 SCTLR_ELx 寄存器是系统控制寄存器,用于控制处理器的系统配置和行为。其中,x 可以是 0、1、2 或 3,分别代表 EL0、EL1、EL2 和 EL3。

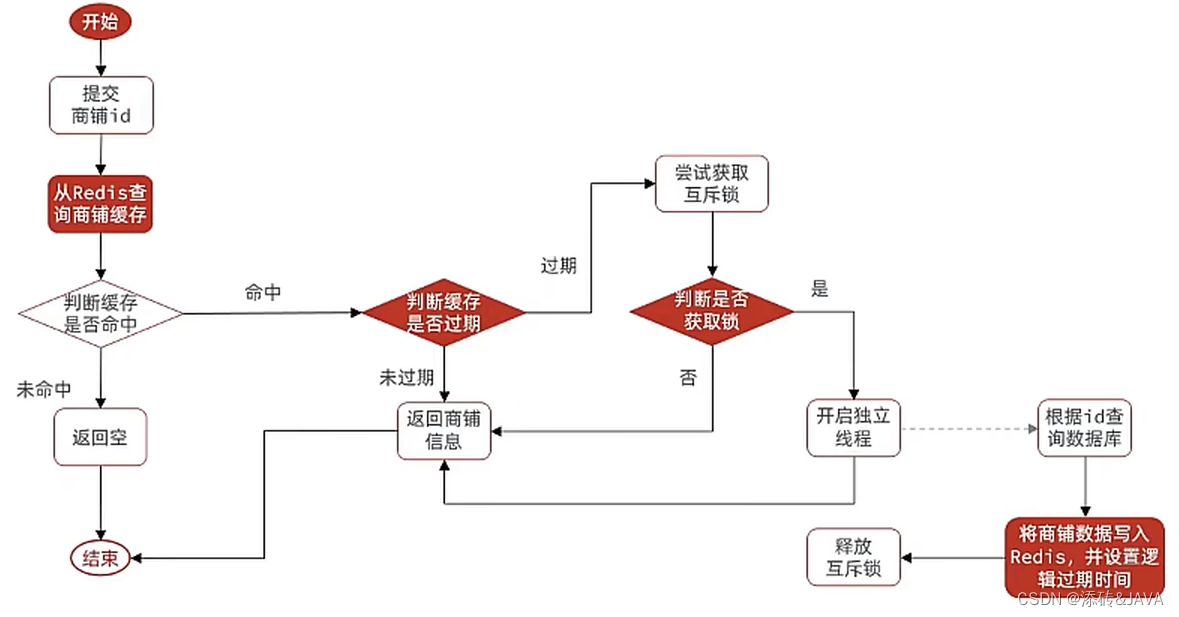

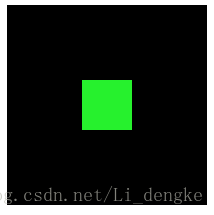

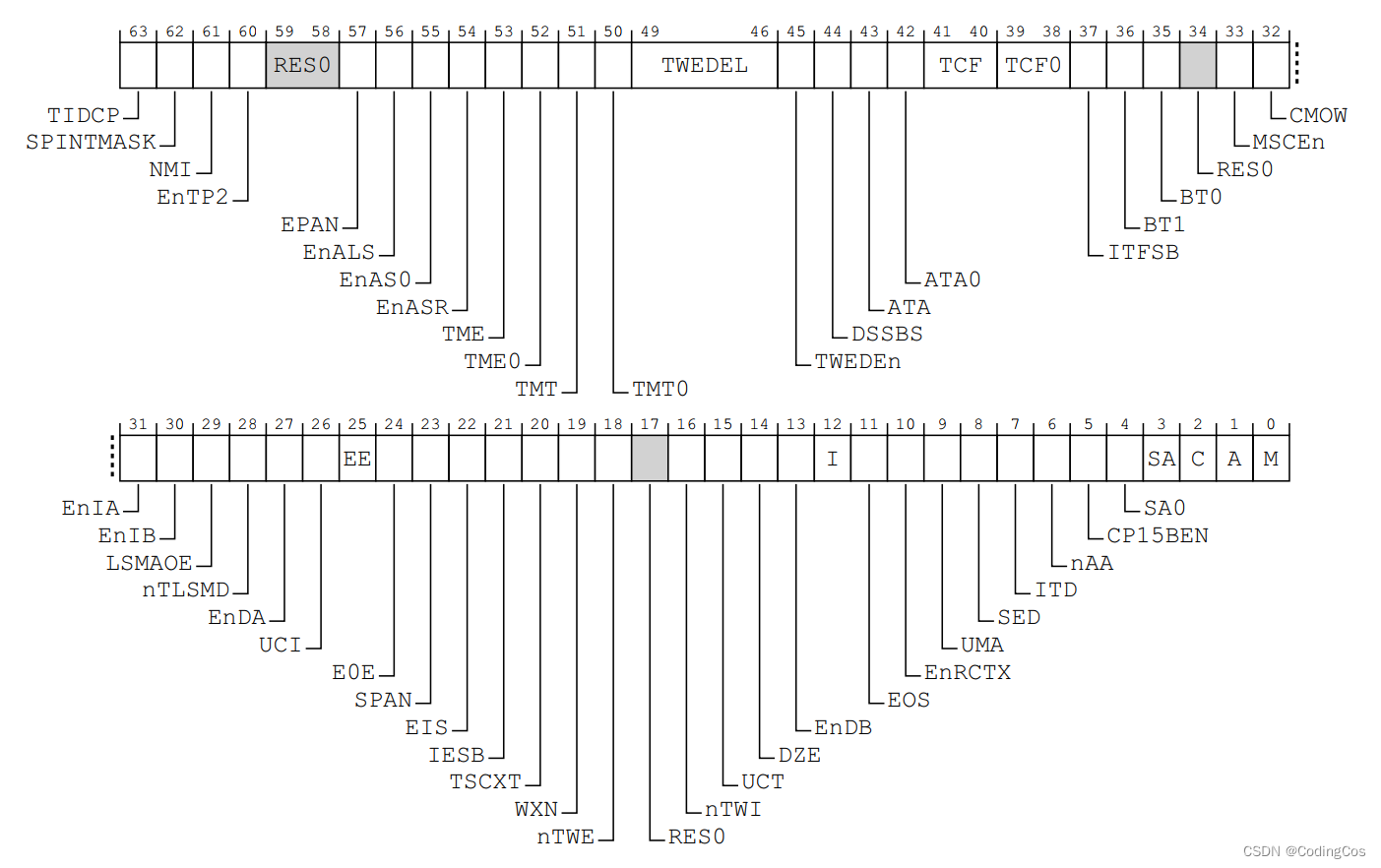

下图为 SCTLR_EL1:

SCTLR_ELx 寄存器的具体功能和位定义如下:

- M: MMU Enable bit。当该位为 1 时,启用 MMU。

- A: Alignment check enable bit。当该位为 1 时,启用地址对齐检查。

- C: Cache enable bit。当该位为 1 时,启用数据和指令缓存。

- SA0: Stack Alignment Check for EL0. 当该位为 1 时,启用 EL0 栈的地址对齐检查。

- SA: Stack Alignment Check bit。当该位为 1 时,启用所有栈的地址对齐检查。

- CPAC: Coprocessor Access Control。用于控制协处理器的访问权限。

- I: Instruction cache enable bit。当该位为 1 时,启用指令缓存。

- D: Data cache enable bit。当该位为 1 时,启用数据缓存。

- UCI: User Cache Inhibit。当该位为 1 时,禁用用户空间的缓存。

- EE: Exception Endianness。当该位为 1 时,异常处理使用大端模式。

- E0E: Endianness of EL0。当该位为 1 时,EL0 使用大端模式。

- WxN: Write permission implies XN. 当该位为 1 时,写权限也意味着禁用执行权限。

- WXN: Write permission implies Execute Never。当该位为 1 时,写权限也意味着禁用执行权限。

- nTWE: Not trap WFE。当该位为 1 时,WFE 指令不会陷入到睡眠状态。

- nTWI: Not trap WFI。当该位为 1 时,WFI 指令不会陷入到睡眠状态。

- UCT: User Cache Type。用于控制用户空间的缓存类型。

- nTLSMD: Not trap Load/Store Multiple Decrement。当该位为 1 时,LDM 和 STM 指令不会陷入到睡眠状态。

- nTLE: Not trap Little-endian。当该位为 1 时,处理器不会陷入到睡眠状态,即使在小端模式下。

- EE_LITTLE: Exception Endianness Little-endian。当该位为 1 时,异常处理使用小端模式。

- SPINTMASK 位域控制了EL1级别的中断控制器(GIC)的中断屏蔽。当spintmask被设置为1时,GIC中断被屏蔽,当spiintmask被设置为0时,GIC中断被开启。

- NMI bit位域控制了EL1级别的非屏蔽中断(NMI)的行为。当nmi bit被设置为1时,NMI被屏蔽,当nmi bit被设置为0时,NMI被开启。

SCTLR_ELx 寄存器中的一些位在不同的 EL 中具有不同的行为和意义。例如,EE 位在 EL1 和 EL2 中分别用于控制异常处理的字节顺序。

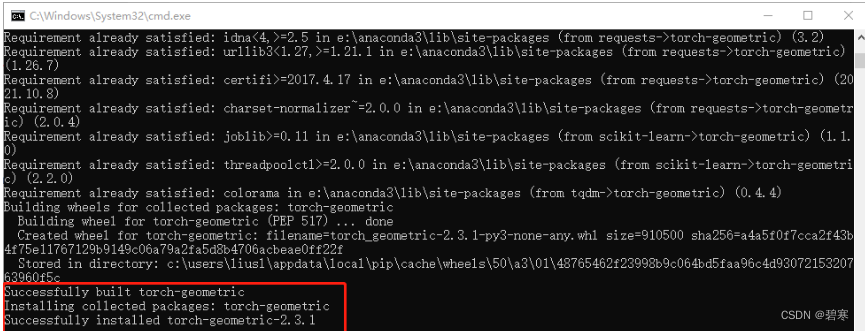

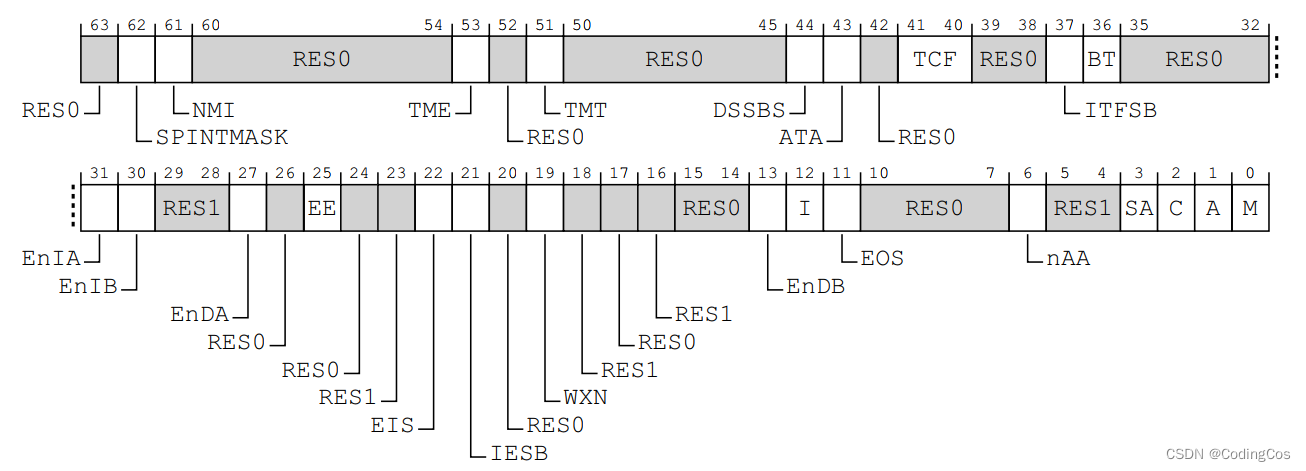

下图为 SCTLR_EL3:

在 armv9 架构中,SCTLR_EL3 寄存器还包含了tme和tmt bit位域,用于控制EL3级别的内存访问。它们的作用如下:

- tme 位域控制了EL3级别的内存加密(Transparent Memory Encryption)的使能。当tme被设置为1时,EL3级别的内存访问将被加密,当tme被设置为0时,EL3级别的内存访问将不被加密。

- tmt bit位域控制了EL3级别的内存隔离(Transparent Memory Tagging)的使能。当tmt bit被设置为1时,EL3级别的内存访问将被隔离,当tmt bit被设置为0时,EL3级别的内存访问将不被隔离。

总的来说,tme和tmt bit位域的作用是控制EL3级别的内存访问的加密和隔离。在一些安全性要求较高的系统中,这些位域的设置可以提高系统的安全性和保护机密数据。

推荐查阅:ChatGPT