目录

1.power gating

2.level shift

3.IR-drop

1.power gating

power gating 的设计重点如下:

1)Power Switch的设计;

2)Power Gating controller的设计;

3)retention register和isolation cell的选择及插入;

4)Power Gating对area和timing的影响;

5)clock和reset模块的设计;

6)Power State transaction的verfication;

7)针对manufacturing的DFT设计策略;

摘自https://www.cnblogs.com/-9-8/p/5487239.html

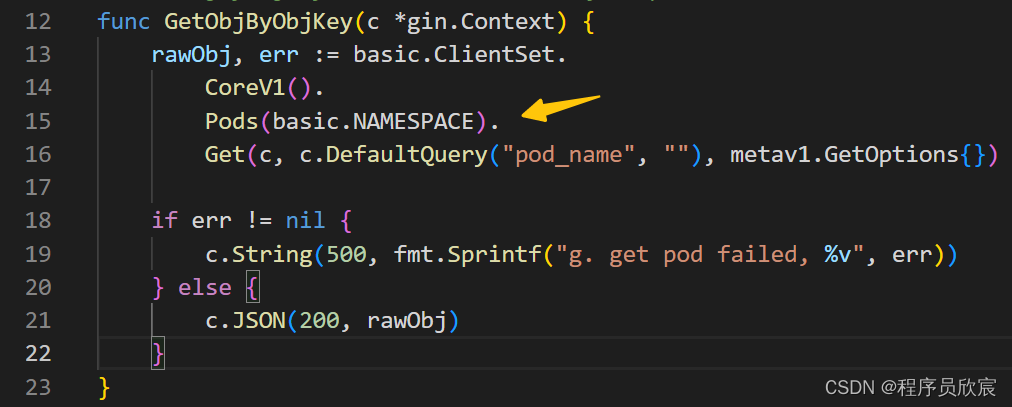

可以看出power gating是一整套的power控制逻辑,包括power switch

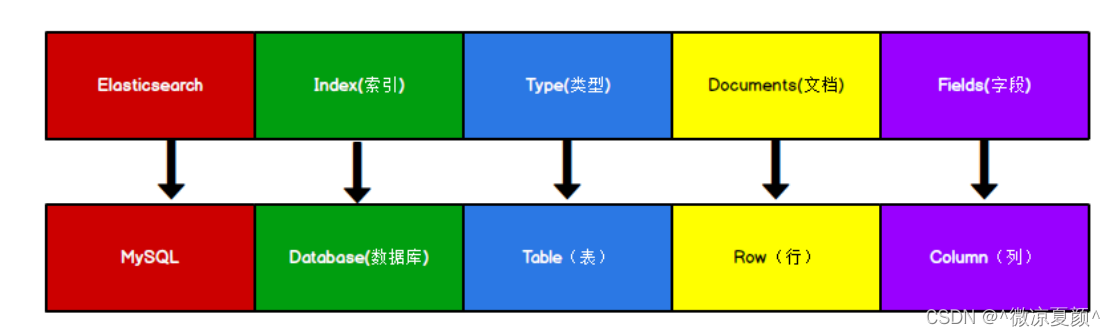

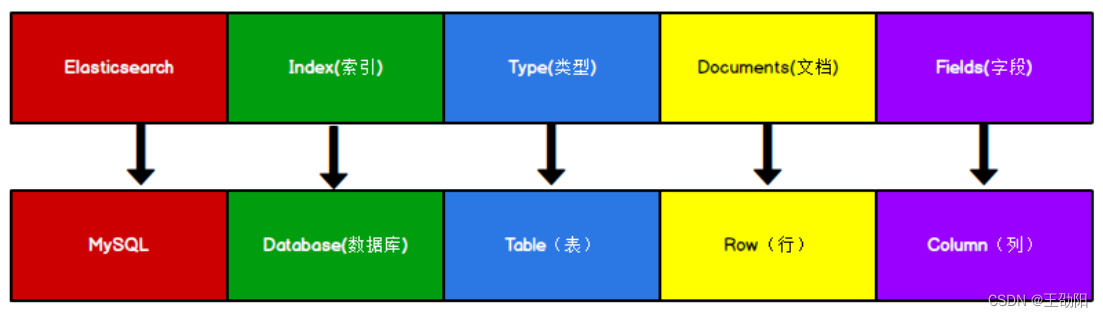

2.level shift

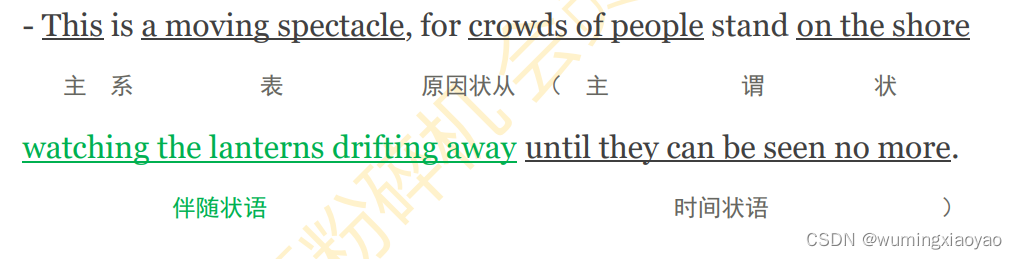

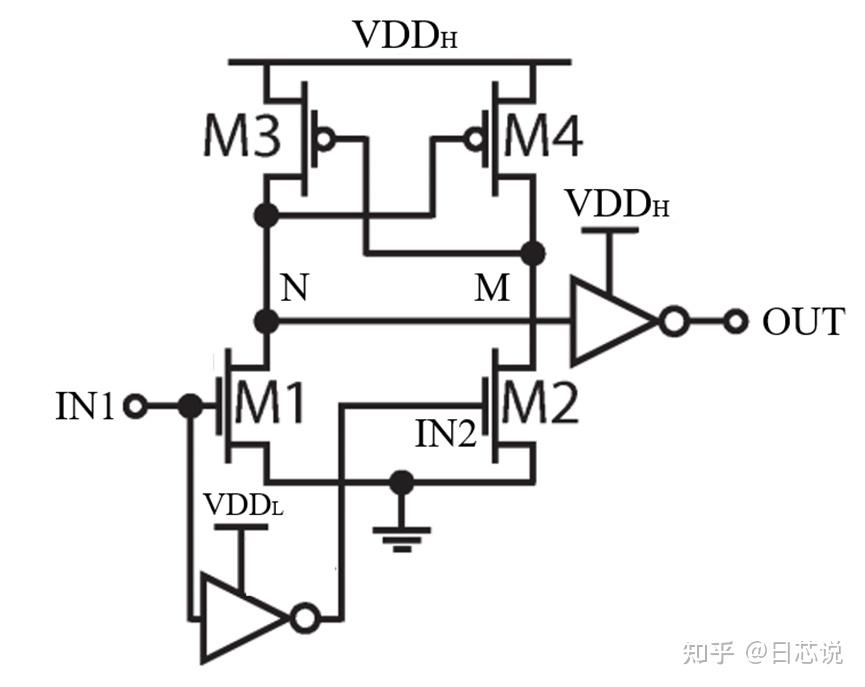

用于在高低不同的电压域中传输信号。下图是一个低电压域传输到高电压域的LS结构图,可以看出LS是需要同时接VDDL和VDDH的。

Level shifter是两条row高度的cell,其中含有VDD,VSS和VDDL(VDDH)。VDDL和VDDH是secondary power pin。在画power时,需要将其画成一个额外的power rail,确保每个Level shift cell secondary power pin的正常供电。

参考:

通向彼岸的桥梁 Level Shift 电压电平转换器 - 知乎

MOS晶体管级level shifter实用原理解析 - 知乎

低功耗基础概念——Level Shifter cell_mos level shifter_时钟树上的小猴子的博客-CSDN博客

3.IR-drop

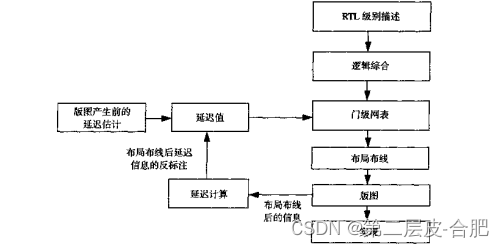

欧姆定律 V = I.R 所以IR-drop就是电压降,由于电源到cell之间有布线的电阻等影响,实际到cell的电压会低于电源电压;又当晶体管大范围开关时,会有电流通过,也会导致电压的波动。

芯片signOff就是要考虑这种IR-drop对电路正常工作,setup/hold的影响。保证在IR-drop的最差情况,芯片也能正常工作。

具体请参考:

浅谈power signoff之什么是IR drop

芯片设计IR-Drop介绍 - 知乎