目录

1. 什么是流片

2. CLB

3. 如何解决亚稳态(Metastability)

4. 什么是可综合

5. 什么是双边沿、上升沿、下降沿

6. IOB

7. PLL

8. IP核

9. 时序分析

10. 时钟域

11. 约束文件

12. 用VERILOG实现消除一个glitch

滤掉小于1个周期glitch

滤掉大于1个周期且小于2个周期glitch

第一时间更新,以及更多更及时的技术资讯和学习技术资料,请关注公众号:CTO Plus

在前面的文章中也介绍过FPGA的设计流程、FPGA综合工具的介绍,也推荐过一些书籍和优秀的开源项目,以及弄清HDL与verilog的区别,以及Verilog HDL、VHDL、SpinalHDL、system verilog的介绍,这些都属于FPGA设计的基础知识和资源。本篇FPGA基本设计概念是指FPGA中的基本组成部分、常用术语和设计流程等。弄清FPGA基本设计概念的目的和意义在于:

1. 理解FPGA的基本组成部分和工作原理,为FPGA应用开发奠定基础;

2. 掌握FPGA常用术语和设计流程,能够更好地进行FPGA应用开发;

3. 了解FPGA的设计流程和调试方法,能够更快地定位和解决问题。

FPGA基本设计概念在FPGA应用开发中具有重要的意义,它是FPGA应用开发的基础和前提,只有掌握了FPGA基本设计概念,才能更好地进行FPGA应用开发。

上一篇文章已经介绍了13个FPGA开发设计中的一些基础概念,详情请参考:初学者必须弄懂的一些基本FPGA设计概念(1)

FPGA专栏:https://blog.csdn.net/zhouruifu2015/category_5690253

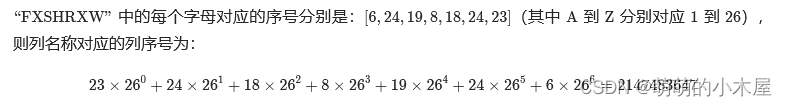

1. 什么是流片

流片(Place and Route)是指将设计好的电路布局(Placement)和连接(Routing)的过程,也是 FPGA 设计中的重要环节之一。在流片过程中,需要将逻辑电路映射到 FPGA 的物理资源上,并进行时序优化和时钟分配等操作,以实现电路的正确性和稳定性。

2. CLB

配置逻辑块,CLB和LUT是FPGA中的基本逻辑单元,用于实现逻辑功能。

3. 如何解决亚稳态(Metastability)

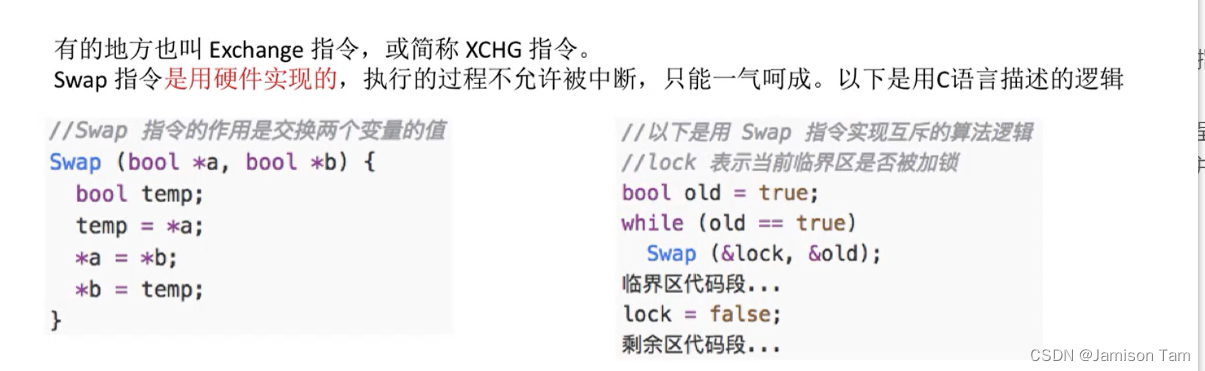

亚稳态 (Metastability) 是数字电路中的一种常见问题,它是指当一个输入信号在时钟边沿到来时,由于时序关系不当,导致输出信号在一段时间内处于不稳定状态,无法确定输出的正确值,即触发器无法在某个规定时间段内达到一个可确认的状态。这种不稳定状态可能持续很短的时间,也可能持续很长的时间,甚至可能一直持续下去,导致电路无法正常工作。

当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

亚稳态通常发生在异步电路中,因为异步电路中的信号没有时钟信号的同步,信号的传输和处理具有不确定的时序关系。亚稳态的产生是由于输入信号的传输延迟与时钟信号的边沿到来时刻之间的差异,导致输入信号在时钟边沿到来时,可能处于不稳定状态,输出信号也随之处于不稳定状态。

为了解决亚稳态问题,需要采取一些措施来确保电路的正确性和稳定性:

1. 引入同步器件:(引入同步机制,防止亚稳态传播)使用锁存器、触发器等同步器件来消除亚稳态问题,将异步信号同步到时钟信号的边沿上,确保输入信号和输出信号的时序关系确定。

2. 增加滤波器:在输入信号和输出信号之间增加滤波器,以滤除亚稳态信号,确保输出信号的稳定性和正确性。

3. 增加冗余电路:增加冗余电路来提高电路的容错能力,当亚稳态出现时,可以通过冗余电路来恢复正常的输出信号。

4. 优化时序设计:优化电路的时序设计,合理设置Setup时间和Holdup时间,确保输入信号在时钟边沿到来时稳定,并且输出信号在时钟边沿后能够稳定输出正确的值。

5. 降低系统时钟频率。用反应更快的Flip-Flop。改善时钟质量,用边沿变化快速的时钟信号。

总的来说,解决亚稳态问题需要设计人员根据具体的设计要求和时序要求,采取一些措施来确保电路的正确性和稳定性。在实际设计中,需要综合考虑各种因素,包括电路的复杂度、性能要求、成本和可靠性等,以选择最合适的解决方案。关键是器件使用比较好的工艺和时钟周期的裕量要大。

4. 什么是可综合

可综合(Synthesizable)是指硬件描述语言(如 Verilog、VHDL)编写的电路代码可以被综合工具转换成硬件电路。可综合的代码需要符合一定的规范和约束条件,以保证综合后的电路的正确性和可靠性。在 FPGA 设计中,可综合的代码可以被综合工具转换成 FPGA 的逻辑电路,从而实现电路的功能和性能。

5. 什么是双边沿、上升沿、下降沿

双边沿:指输入信号的上升沿和下降沿都会被检测到,常用于时钟信号的检测。

上升沿:指输入信号从低电平到高电平的过渡,常用于时钟信号的检测。

下降沿:指输入信号从高电平到低电平的过渡,常用于时钟信号的检测。

6. IOB

输入输出块,用于FPGA与外部设备的通信。

7. PLL

锁相环,用于FPGA中的时钟管理和时序控制。

8. IP核

知识产权核,是一种可重用的硬件模块,用于快速构建FPGA应用。

9. 时序分析

用于分析FPGA中的时序关系,确保FPGA设计的正确性。

10. 时钟域

FPGA中的时钟信号的传输和处理的区域,用于保证时序正确性。

11. 约束文件

用于指定FPGA设计中的时序约束和资源约束,确保FPGA设计的正确性。

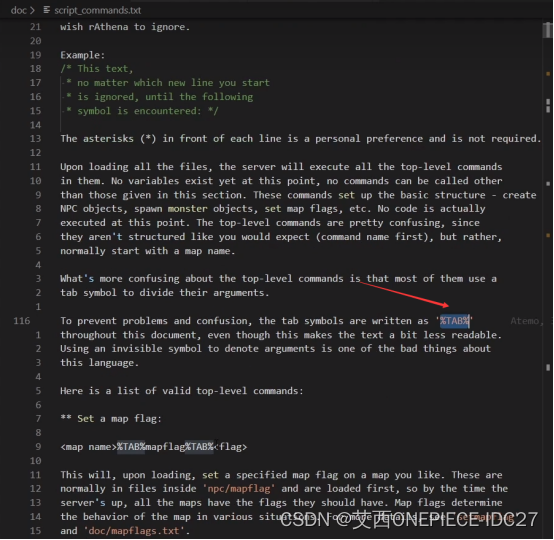

12. 用VERILOG实现消除一个glitch

滤掉小于1个周期glitch

module glitch_filter(input clk, input glitch_in, output reg glitch_out);

reg [1:0] state;

always @(posedge clk) begin

case (state)

2'b00: begin

if (glitch_in == 1'b1) begin

state <= 2'b01;

glitch_out <= 1'b1;

end else begin

state <= 2'b00;

glitch_out <= 1'b0;

end

end

2'b01: begin

if (glitch_in == 1'b0) begin

state <= 2'b10;

end else begin

state <= 2'b01;

end

end

2'b10: begin

state <= 2'b00;

glitch_out <= 1'b0;

end

endcase

end

endmodule

以上代码实现了一个简单的消除glitch的电路。该电路的输入包括时钟信号clk和待消除glitch的信号glitch_in,输出为消除glitch后的信号glitch_out。该电路的原理是,当检测到一个高电平glitch_in时,将输出glitch_out置为高电平,并进入状态01;当检测到一个低电平glitch_in时,进入状态10,并将glitch_out置为低电平;当检测到一个正常的高电平信号时,进入状态00,并将glitch_out置为低电平。

该电路的工作原理如下:

1. 当glitch_in为高电平时,进入状态01,将glitch_out置为高电平。

2. 当glitch_in为低电平时,进入状态10,将glitch_out置为低电平。

3. 当glitch_in为正常的高电平信号时,进入状态00,将glitch_out置为低电平。

由于该电路只在检测到一个周期以上的glitch_in信号时才会输出高电平glitch_out信号,因此可以实现滤掉小于1个周期的glitch。

滤掉大于1个周期且小于2个周期glitch

module glitch_filter(input clk, input glitch_in, output reg glitch_out);

reg [2:0] state;

always @(posedge clk) begin

case (state)

3'b000: begin

if (glitch_in == 1'b1) begin

state <= 3'b001;

glitch_out <= 1'b1;

end else begin

state <= 3'b000;

glitch_out <= 1'b0;

end

end

3'b001: begin

if (glitch_in == 1'b0) begin

state <= 3'b010;

end else begin

state <= 3'b001;

end

end

3'b010: begin

if (glitch_in == 1'b1) begin

state <= 3'b011;

end else begin

state <= 3'b010;

end

end

3'b011: begin

state <= 3'b100;

end

3'b100: begin

state <= 3'b000;

glitch_out <= 1'b0;

end

endcase

end

endmodule

以上代码实现了一个消除glitch的电路,并且可以滤掉大于1个周期且小于2个周期的glitch。该电路的输入包括时钟信号clk和待消除glitch的信号glitch_in,输出为消除glitch后的信号glitch_out。该电路的原理是,当检测到一个高电平glitch_in时,将输出glitch_out置为高电平,并进入状态01;当检测到一个低电平glitch_in时,进入状态10,并等待一个周期;当检测到一个高电平glitch_in时,进入状态11,并等待一个周期;当等待两个周期后,进入状态100,并将glitch_out置为低电平。

该电路的工作原理如下:

1. 当glitch_in为高电平时,进入状态001,将glitch_out置为高电平。

2. 当glitch_in为低电平时,进入状态010,并等待一个周期。

3. 当等待一个周期后,如果glitch_in为高电平,则进入状态011,并等待一个周期;如果glitch_in为低电平,则重新进入状态010。

4. 当等待两个周期后,进入状态100,并将glitch_out置为低电平。

由于该电路需要等待两个周期才能消除大于1个周期且小于2个周期的glitch,因此可以实现滤掉这类glitch。

SteveRocket的博客_CSDN博客-Python进阶,Django进阶,C进阶领域博主SteveRocket擅长Python进阶,Django进阶,C进阶,等方面的知识https://blog.csdn.net/zhouruifu2015/

更多资料 · 微信公众号搜索【CTO Plus】关注后,获取更多,我们一起学习交流。

关于公众号的描述访问如下链接

关于Articulate“做一个知识和技术的搬运工。做一个终身学习的爱好者。做一个有深度和广度的技术圈。”一直以来都想把专业领域的技https://mp.weixin.qq.com/s/0yqGBPbOI6QxHqK17WxU8Q

推荐阅读:

-

FPGA在工业缺陷检测上的应用实践

-

FPGA设计Verilog基础之Verilog全局变量和局部变量定义

-

FPGA设计Verilog基础之Verilog中clk为什么要用posedge,而不用negedge

-

初学者必须弄懂的一些基本FPGA设计概念(1)

-

工作总结之全网最全的103个Verilog关键字总结(上)

-

工作总结之全网最全的103个Verilog关键字总结(下)

-

5G时代的FPGA发展趋势和应用分析

-

FPGA结合chatgpt的应用开发实践

-

FPGA | FPGA设计流程指南 v2.0

-

设计规范 | 总结开发过程中DDR3和FPGA部分的设计规范

-

术语一览 | 总结开发过程中关于FPGA的专业术语

-

用AI帮我写一篇关于FPGA的文章,并推荐最热门的FPGA开源项目