实验五 计数/定时器的设计【Verilog】

- 前言

- 推荐

- 实验五 计数/定时器的设计

- 一、实验目的

- 二、实验环境

- 三、实验任务

- 四、实验原理与实验步骤

- 五、实验思考

- 最后

前言

以下内容源自Verilog实验

仅供学习交流使用

推荐

Verilog

实验五 计数/定时器的设计

一、实验目的

- 掌握二进制计数器/定时器的工作原理和设计方法。

- 掌握用计数器进行分频的方法。

二、实验环境

- 装有ModelSim和VIVADO的计算机。

- Sword实验系统。

三、实验任务

- 用VerilogHDL语言设计实现32位加法/减法二进制计数器,在ModelSim上实现功能仿真。

- 生成FPGA设计文件,下载到Sword实验系统上验证电路功能。

四、实验原理与实验步骤

- 实验原理

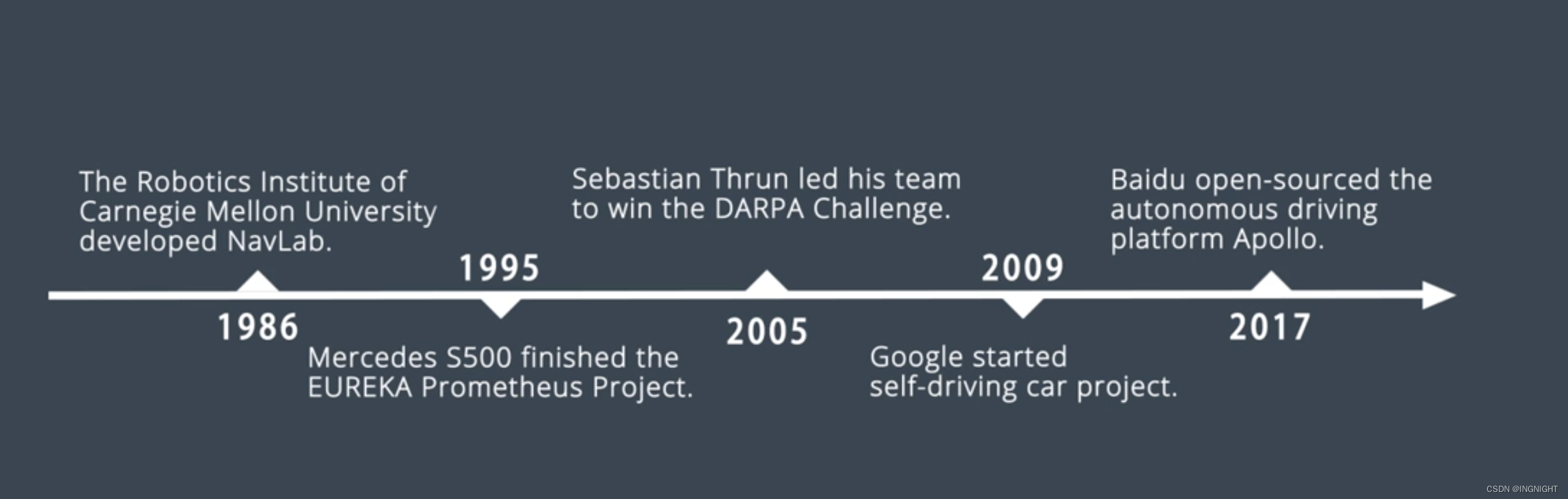

计数器是计算机硬件系统中的一个基本功能电路,是计数、分频、定时、同步等电路的核心,在计算机、网络、数字通信中经常使用到。

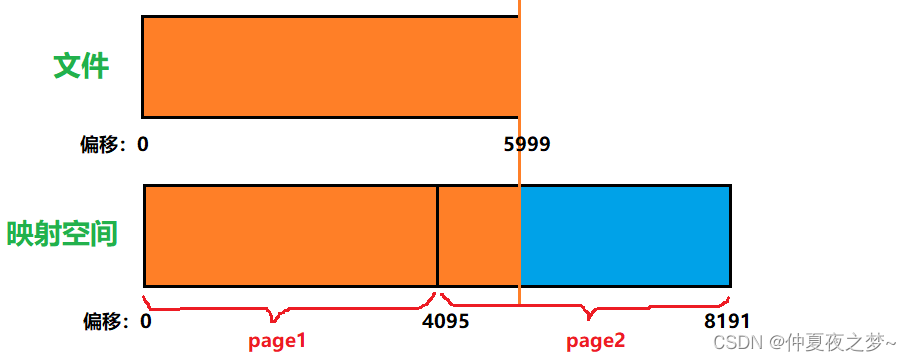

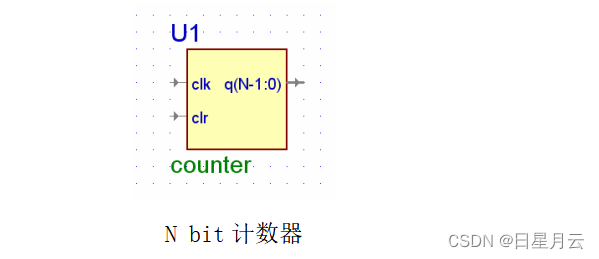

N bit计数器

- 实验步骤

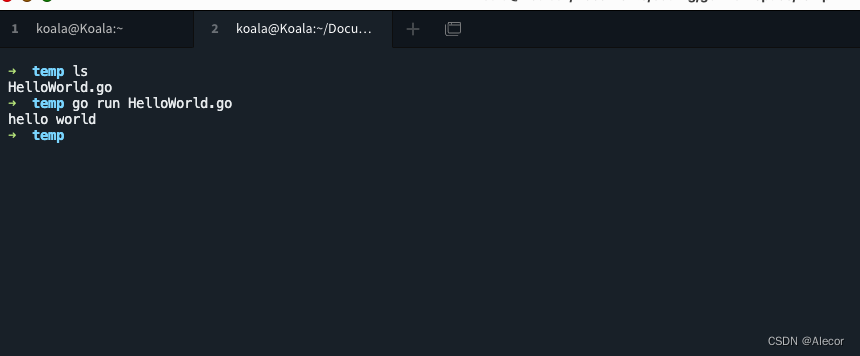

(1)用Verilog完成32bit加法计数器的行为描述设计。

(2)完成modelsim下电路的功能仿真,验证电路功能。

(3)设计完成I/O引脚分配。

系统时钟为100MHz,作为计数时钟。

采用sw[0]作为reset信号,将32bit的计数值在实验板的八个七段数码管上显示。

(4)生成FPGA文档,并下载到实验板上物理运行,检查设计结果。

(5)在上述基础上,完成32位加减法计数器。首先完成modelsim下的加减法计数器功能仿真,其次采用sw[1]作为方向选择信号,将加减法计数器的计数值在数码管上显示。

五、实验思考

1、如何设计实现模N计数器?

2、结合自己的设计,思考是否有别的方法实现本实验要求的电路设计,对自己的代码提出改进建议。

最后

这篇博客能写好的原因是:站在巨人的肩膀上

这篇博客要写好的目的是:做别人的肩膀

开源:为爱发电

学习:为我而行

![[yolov5] yolo的数据标签格式](https://img-blog.csdnimg.cn/9f9ed4ca2da248468309a9418c4c40a7.png)

![[附源码]计算机毕业设计springboot在线图书销售系统](https://img-blog.csdnimg.cn/15a8b9e10a88492ead22978adce42351.png)