数字电路与模拟电路的设计思想和应用方法有许多不同之处。

计算器是一个典型的由数字电路实现的电子设备,用户通过数字或符号摁键输入运算式,计算器经过运算之后把结果显示在屏幕上。现代数学电子学始于1946年,其标志是一台以电子管为核心器件的数字计算机(ENIAC)的诞生。虽然这台庞大的机器需要一整间屋子才能装的下,但它的计算能力还比不上现在的任何一台计算器。

比计算器更亲切的数字设备还有计算机、手机、MP3播放器、数码相机、U盘等一切数码产品。数码产品中的主要的器件都属于数字电路的范畴。今天,其实数字电路比模拟电路距离我们更近。

文章目录

数制与编码

逻辑门

与门、或门、非门

与非门和或非门

逻辑门集成电路

逻辑电路的分析

布尔代数及运算规则

用布尔代数分析逻辑电路

用布尔表达式描述真值表

组合逻辑的功能器件

与或门

加法器

比较器

译码器和编码器

翻转与计数

锁存器与触发器

计数器

数制与编码

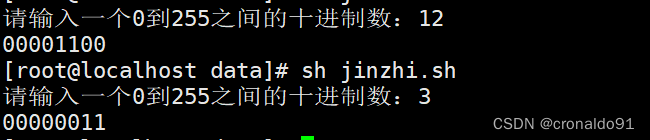

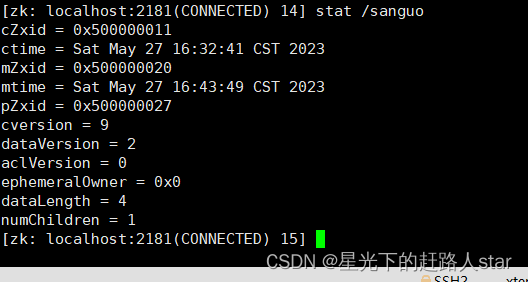

1和0代表了数字电路的两种状态。在数字电路中除了二进制外,还常常会涉及到十六进制。和十进制的进位原理一样,十六进制每逢16向高位进1。BCD(binary coded decimal)二进制编码的十进制数。下图是几种常用数制的比照表,从中可以看到它们是如何相互换算的。

公交汽车上或车站里的一些LED大屏幕以及手机等数码产品的液晶屏所显示的图形、文字都是通过点阵来实现的。如果把这些点阵放大,就会清楚地看到每一个点,如下图所示,MP3播放机液晶屏上的英文字母A为5*7点阵,即A由5列7行的点阵信息组成。用1表示点亮,用0表示熄灭。如下图所示,这个二进制编码代表了显示信息-字母A,其他文字或者图形也都可以用类似的方法进行编码。而这些二进制编码可以用代表高电平、低电平的1和0存储在MP3的存储器中,经转换后成为液晶屏上的显示信息。

逻辑门

逻辑门(logic gate)是数字电路的基本单元,一个逻辑门有一个输出端和一个或多个输入端。输出端只有1或0两种状态。或者说只有高电平或低电平两种状态,这取决于输入信号和逻辑门功能。逻辑门可进行与、或、非等逻辑运算,对应的也就有与门、或门、非门等基础逻辑门和组合逻辑电路。

与门、或门、非门

与门(AND gate,电路符号![]() )有两个或两个以上输入端和一个输出端,如下图所示,A、B为与门的输入端,Y为输出端。只有当所有输入端为1时,输出才为1。只要有任何一个输入端为0,输出就为0。这个关系可以用表达式Y=AB来表示---输出A、B相乘得到输出Y。

)有两个或两个以上输入端和一个输出端,如下图所示,A、B为与门的输入端,Y为输出端。只有当所有输入端为1时,输出才为1。只要有任何一个输入端为0,输出就为0。这个关系可以用表达式Y=AB来表示---输出A、B相乘得到输出Y。

非门(NOT gate、inverter电路符号![]() ) 有一个输入端A和输入端Y,如下图所示。其逻辑功能非常简单,把输入信号做非运算(取反)后输出:A=1时,Y=0;A=0时,Y=1。

) 有一个输入端A和输入端Y,如下图所示。其逻辑功能非常简单,把输入信号做非运算(取反)后输出:A=1时,Y=0;A=0时,Y=1。

或门(OR gate,电路符号![]() )有两个或三个输入端和一个输出端,如下图所示,只要输入端A或B有一个为1,输出Y就为1.或门做的是或运算,类似加法:Y=A+B。

)有两个或三个输入端和一个输出端,如下图所示,只要输入端A或B有一个为1,输出Y就为1.或门做的是或运算,类似加法:Y=A+B。

与非门和或非门

与非门(NAND gate,电路符号![]() )是在与门的基础上做一个非运算,在电路符号的输出端用一个泡泡来表示。下图展示了与非门的逻辑表达式以及真值表。

)是在与门的基础上做一个非运算,在电路符号的输出端用一个泡泡来表示。下图展示了与非门的逻辑表达式以及真值表。

或非门(NOR gate,电路符号![]() )是在或门的基础上做一个非运算,也在电路符号的输出端用一个泡泡来表示,下图是或非门的运算表达式、真值表。

)是在或门的基础上做一个非运算,也在电路符号的输出端用一个泡泡来表示,下图是或非门的运算表达式、真值表。

逻辑门集成电路

下图是一个或非门的集成电路器件结构和型号。他在一个芯片内集成了四个或非门。

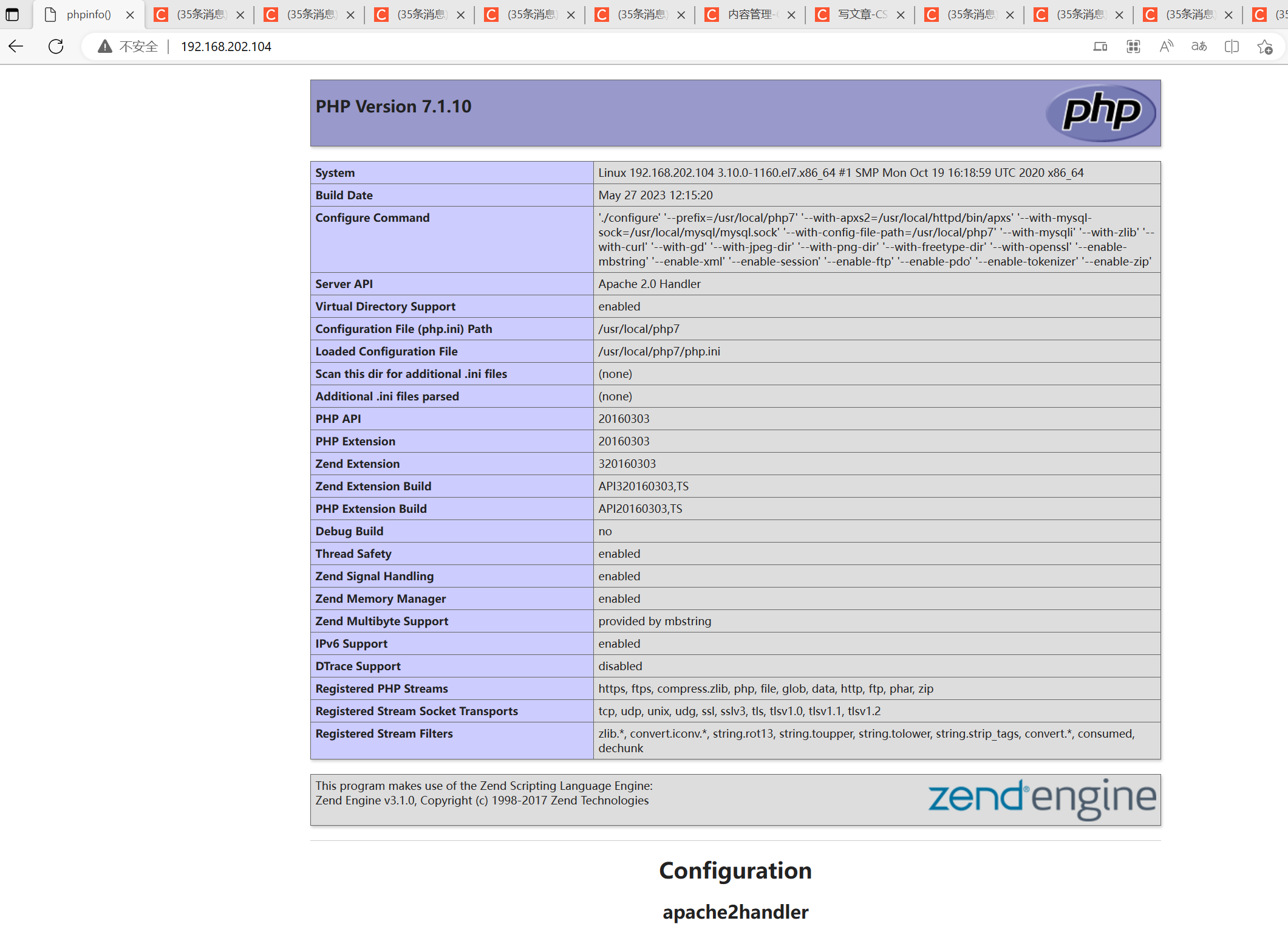

目前有3种数字集成电路技术可用于实现逻辑门器件的制造,分别是TTL、CMOS、ECL。刚才谈到的各种与门、或门等逻辑功能在用不同的集成电路技术制造出的器件中相同,比如说与门的逻辑功能是进行与运算,无论使用TTL或CMOS技术实现的与门集成电路,功能是完全相同的。由于ECL在特殊场合才会用到,所以后边我们只介绍一下TTL和CMOS这两种集成电路技术。

TTL—Transistor-Transistor Logic( 三极管-三极管逻辑),TTL电路以双极型晶体管(三极管)为开关元件,所以又称双极型集成电路。双极型数字集成电路是利用电子和空穴两种不同极性的载流子进行电传导的器件。它具有速度高(开关速度快)、驱动能力强等优点,但其功耗较大,集成度相对较低。根据应用领域的不同,它分为54系列和74系列,前者为军品,一般工业设备和消费类电子产品多用后者。

CMOS—Complementary Metal-Oxide Semiconductor(互补型金属氧化物半导体晶体管),CMOS电路是由绝缘场效应晶体管组成,由于只有一种载流子,因而是一种单极型晶体管集成电路。它的主要优点是输入阻抗高、功耗低、抗干扰能力强且适合大规模集成。特别是其主导产品CMOS集成电路有着特殊的优点,如静态功耗几乎为零,输出逻辑电平可为VDD或VSS,上升和下降时间处于同数量级等,因而CMOS集成电路产品已成为集成电路的主流之一。其品种包括4000系列的CMOS电路以及74系列的高速CMOS电路。

逻辑电路的分析

1854年,George Boole发表了题为《一个关于思想的研究,从中发现的逻辑和概率的数学理论》的研究报告,其中提出的逻辑代数便是今天为人熟知的布尔代数。在对逻辑电路进行表述和分析时,布尔代数是一个方便而系统的工具。

布尔代数及运算规则

布尔加法与或运算是相同的,下图表征了布尔加法的四种情况。

布尔乘法与上面提到的与运算时相同的,下面表征了布尔乘法的四种情况。

就像普通的数学运算有一些成熟的法则可用于简化过程一样,布尔代数也有类似的运算法则供计算时使用,如下图所示。

除了以上布尔代数运算法则外,常常还会用到下图所示的规则对布尔表达式进行操作和简化。

用布尔代数分析逻辑电路

布尔代数只用一个简明的表达式就可以表示逻辑门组合逻辑电路。所有的布尔表达式都可以化成两种标准的表达式,一种是积的和,另一种是和的积。将非标准形式的表达式化成标准形式更易于对系统进行分析。

积的和(SOP)标准形式就是形如:Y=AB+BCD+AC的布尔表达式,先让变量相乘,然后再求和。体现在逻辑电路上就是先完成与操作,再进行或操作。下图为一个积的和例子。

和的积(POS)标准形式是形如Y=(A+B)(B+C+D)(A+C)的布尔表达式,先让变量相加,然后求积。体现在逻辑电路上就是先完成或操作,再进行与操作。下图为一个和的积例子。

用布尔表达式描述真值表

任何逻辑电路都可以用布尔表达式进行描述,而表达式经过化简化还可以反过来生成一个没有冗余的逻辑电路。布尔表达式与逻辑电路有很好的对应关系。此外,从布尔表达式,特别是最简表达式可以轻易构造一张真值表,只要把每种输入状态和对应的输出状态列在同一个表里就可以直观地了解逻辑电路的功能。下图是一个逻辑电路与其对应的真值表。

组合逻辑的功能器件

组合逻辑电路指由简单逻辑门组合形成并具有较复杂功能的数字逻辑电路。

与或门

与或门(AND-OR logic)由多个与门和一个或门构成,实现积的和运算。如下图所示是两个与门和一个或门组成的与或门,可得该与或门的表达式为:Y=AB+CD。图中还给出了对应的真值表。

加法器

加法器(adder)是一个应用广泛的器件,比如74LS83是一款常用的4位并行加法器,其管脚排布如下图所示,其中、

、

、

是一个4位输入,

、

、

、

是另一个4位输入。

是进位输入端,可接收从上一级加法器送来的进位信号。

为本级加法器的进位信号输出端。

、

、

、

是加法器的输出,求和结果由这四位输出。

比较器

在数字系统中,常常需要比较两个二进制数的大小,这时可以使用一个型号为74LS85的4位比较器(comparator)。如下图为该器件的管脚排布,它有A和B两个4位二进制数输入端,另外还提供3个级联输入端、

、

(2、3、4管脚)。3个输出端

、

、

(5、6、7管脚)指示输入二进制的大小关系:如果A端二进制数>B端二进制数,

。

译码器和编码器

译码器(decoder)的功能是检测输入端的二进制数,并在输出端对应位上唯一输出1或0.拿译码器74HC138来说,如下图所示,、

、

是输入端,这3个位的状态(二进制数)决定了译码器输出端

中的某位输出为0。举例来说,假如输入为二进制101,即十进制的5,于是对应的

=0,其他输出端为1。74HC138的4、5、6管脚为使能端,只有当

=0,

=0,

=1时译码器工作,否则输出端全部为1。

翻转与计数

不管时简单的逻辑电路,还是具有组合逻辑功能的器件,它们的输入、输出与时间并没有太大关系。比如在任何时刻往加法器的两个输入端送入二进制数,输出端几乎同时得到运算结果。本章要介绍的时序电路时数字电路中的一个大类。这类电路某一时刻的输出状态,不仅与当前输入变量的状态有关,而且还与前一时刻的状态有关。一般来说,时序电路由组合逻辑电路和存储单元或反馈延迟电路组成。

锁存器与触发器

锁存器(latch)是一种双稳态器件,或者说是多谐振荡器(multivbrator)。下图为一个称为锁存器结构,由两个与非门交叉耦合组成,

和

是信号输入端,

和

为输出端,

锁存器中任意一个与非门的输出与另一个与非门的输入相连以形成负反馈,这是所有锁存器和触发器的特征所在。

锁存器的特点两个输入状态不同的时候会锁定输出的状态,也就是说在两者不同时确定的输出状态,不会因为两个输入状态变成一样而改变,利用这一特性,下图是锁存器作为开关过滤器的应用。

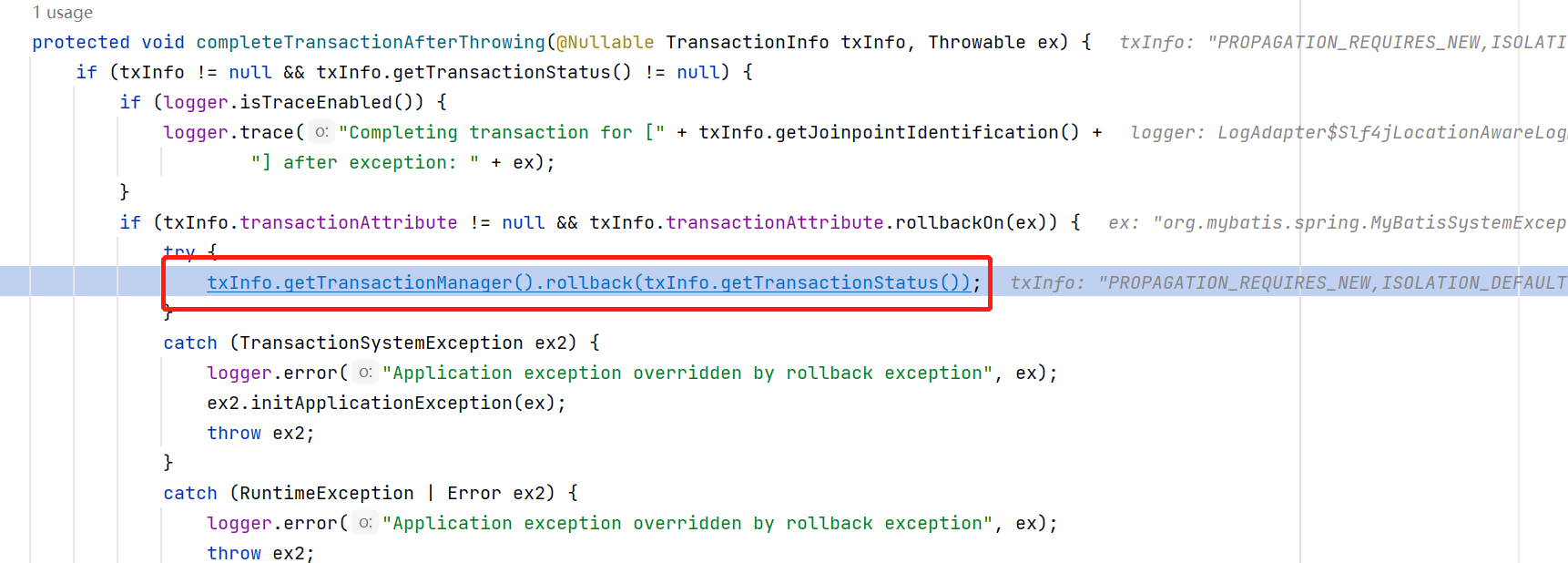

与锁存器不同,边沿触发器多了一个时钟脉冲输入端,并只会在时钟脉冲的上升延或下降延中翻转。拿下图的边沿D型触发器(74HC74)为例,当置位端和复位端

都等于1时为触发模式,此时输出Q将在时钟脉冲输入端CP出现上升沿时翻转置与输入端

相同状态。

触发器可以用于实现并行数据存储、分频器以及计数器。

计数器

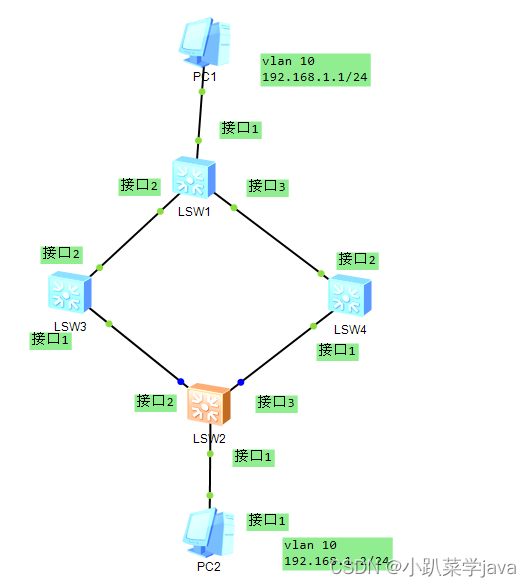

由若干个触发器组成形成具有计数功能的电路称为计数器(counter)。计数器的计数位数等于触发器的个数。根据时钟信号的不同,计数器可分为异步(asynchronous)计数器和同步(synchronous)计数器两大类。异步计数器除第一级触发器使用外部时钟外,后续每个触发器的时钟信号使用的都是前一级的输出;而同步计数器中所有触发器公用一个外部时钟信号。

下图为利用两个J-K触发器组成的2位异步二进制计数器,该计数器的输出为、

。两个触发器的输入端J、K全部接1,外部时钟信号CLK只输入第一个触发器FF0,而第二个触发器FF1的时钟信号来自FF0的反向输出端

。

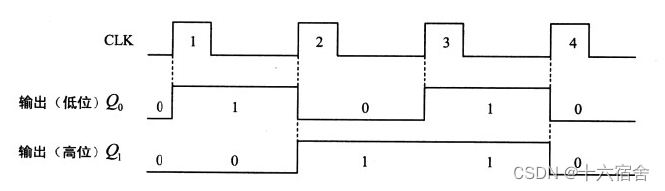

分析类似计数器这一类的时序电路,常称表示输入、输出的波形为时序图。如下图所示为2位异步二进制计数器的时序图,图中最上方为外部时钟脉冲CLK,其下为各个输出端的波形。

下图所示为2位同步二进制计数器,其与异步计数器最大的不同在于各级触发器在统一的外部时钟脉冲信号CLK提供的时序下进行工作。和

接高电平,于是

随着每个CLK脉冲进行高低电平的转换。

下图为2位同步二进制计数器的时序图。

十六宿舍 原创作品,转载必须标注原文链接。

©2023 Yang Li. All rights reserved.

欢迎关注 『十六宿舍』,大家喜欢的话,给个👍,更多关于嵌入式相关技术的内容持续更新中。