目录

1 最基本的方式

2 指定多个文件

3. 使用filelist文件

4 指定整个目录中的所有指定后缀的文件

5 指定include文件的搜索路径

6 追加宏的定义

7 Verdi相关的选项

8 Vivado中的处理方式

1 最基本的方式

最基本的方式就是直接在命令行指定单个源文件,比如说(这里以vcs为例,但是对于其它常见工具也基本都适用,下同):

vlogan -sverilog design1.sv

其中vlogan是vcs的编译命令。以上命令针对一个设计文件进行编译。-sverilog表示其后跟随的文件应该按照SystemVerilog语法进行编译。不指定文件类型的话缺省为verilog。不过,在细节方面处理各种工具有所不同。比如说,vcs是用-sverilog,而QuestaSim、irun等则是用"-sv"。又比如说,有些EDA工具也会根据文件名后缀来推断其类型。除非是文件名后缀为.v,但是希望按照SystemVerilog语法来解释才需要显式地指定“-sv”选项。而vcs则不看文件名后缀,要按systemverilog语法编译必须显式地指定"-sverilog"。

2 指定多个文件

指定多个文件自然就是,作为直感,在命令行跟多个文件就好了。

vlogan -sverilog design1.sv design2.sv design3.sv ...

但是想一下,如果很多个文件(比如说十几个),而调试阶段需要反复执行编译命令,每次输入这么多文件名就会成为一件令人崩溃的事情(虽然一般来说用up/down键可以查到命令历史避免重复输入的情况)。当文件数再多一些,哪怕在命令行只需要输入一次(其后都用up/down键可以查到命令历史来复用)也是一件可怕的事情。这时候,就需要考虑用一个文件来将所有文件列入其中,参见下一节。

3. 使用filelist文件

将所需要加入的源文件都列在一个文本文件中,然后命令行用“-f”选项引用该文件,这样就解决了上一节所提出来的问题。比如说:

file.lst (ASCII文件,即文本文件):

-sverilog design1.sv

-sverilog design2.sv

-sverilog design3.sv

....

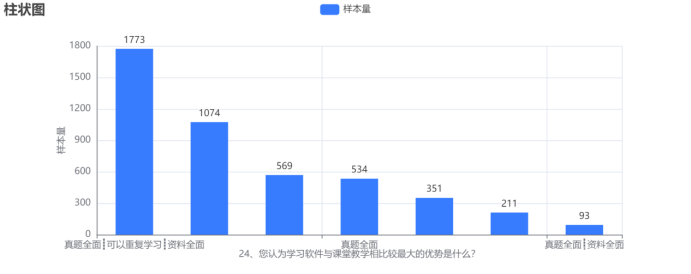

-sverilog design100.sv

然后在命令行只需要如下即可:

vlogan -f file.lst

当源文件有增删(注意,不是说源文件内容有修改,而是说要添加一个文件或删除一个文件)时只需要单独修改file.lst即可。注意,“file.lst”不是一个专用文件名,你可以自行选择任意合适的文件名。

但是,当一个大型项目有许多个源文件目录,有非常多的文件(比如说不同的模块、不同的子系统由不同的队伍分别开发,现在做系统集成),像这样一个问一个文件地列出来也是一件和费劲的事情。这时候就可以考虑以指定目录,并结合文件类型(文件后缀)指定的方式来将指定目录下的所有指定后缀类型的文件全部加入了,参见下一节。

4 指定整个目录中的所有指定后缀的文件

“-y”用于指定目录路径

“-libext+”用于指定文件后缀名

比如说要将目录src1底下的所有.v和.sv后缀的文件全部加入编译列表,可以在命令行,当然更常见的是在一个文件中指定如下:

/************************************************************************

* compile list specification

************************************************************************/

-y ../../../src/IP_LIB1

-y ../../../src/WAFE_RX

-y ../../../src/HIF

+libext+.v+libext+.sv

5 指定include文件的搜索路径

有些文件,通常是用于定义参数或者宏定义的头文件是以include的方式包含在其它源文件中,通常在“`include”语句不包含路径信息。编译器在看到“`include”语句时需要去搜索该文件在哪里。这个时候可以用“+incdir+”选项来告诉编译器应该到哪里去找被include的头文件,如下例所示:

+incdir+../../../src/header/

-y ../../../src/IP_LIB1

-y ../../../src/WAFE_RX

-y ../../../src/HIF

+libext+.v+libext+.sv

../../../src/TOP/design1.sv

../../../src/TOP/design2.sv

当然在以上这个file.lst文件中仍然可以另行指定单个的文件,如最后两行所示。

6 追加宏的定义

一个设计通常可能会可以通过预处理器宏开关来控制其中的配置情况或者设计选项的切换,本质上是切换编译范围。有时也通过宏来指定设计参数。

比如说一个DMA的设计,4个通道还是8个通道,在编译时指定宏的值来决定按几个通道进行设计配置,也同样可以在命令行或者file.lst指定宏的定义,这里有两种情况。如下所示(最后两行):

+incdir+../../../src/header/

-y ../../../src/IP_LIB1

-y ../../../src/WAFE_RX

-y ../../../src/HIF

+libext+.v

+libext+.sv

../../../src/TOP/design1.sv

../../../src/TOP/design2.sv

+define+NUM_CH=8

+define+DMA_ON

其中,

NUM_CH对应于设计中使用到的一个参数类的宏,比如说用于指定通道数为8个。

DMA_ON则对应于设计中使用的一个开关类的宏,比如说用于打开或关闭某一段代码。

7 Verdi相关的选项

上面通过-y 指定library目录, +libext+.v指定library后缀名。 有时候还用-v 来指定library文件。但是这样直接被verdi吃进去以后不能显示hierarchy和文件。比如说,用Verdi看电路的schematic图时,无法点进去看到下一层次。

verdi提供了解决的办法是(是否专属于verdi?待确认): -ssy (用来取消-y指定的library为library cell) -ssv (用来取消-v 指定的library为library cell)

-ssy

-ssv

+incdir+../../../src/header/

-y ../../../src/IP_LIB1

-y ../../../src/WAFE_RX

-y ../../../src/HIF

+libext+.v

+libext+.sv

../../../src/TOP/design1.sv

../../../src/TOP/design2.sv

+define+NUM_CH=8

+define+DMA_ON

8 Vivado中的处理方式

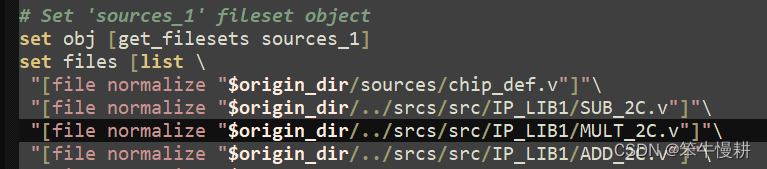

在Vivado的Tcl脚本中, 可以通过set_property命令来实现一部分以上选项相同的功能。

For Vivado in project mode:

For \+incdir\+:

set_property include_dirs <directory_name> [current_fileset]

For \+define\+:

set_property verilog_define a=b [current_fileset]

至于,-y and \+incdir\+, Vivado Tcl脚本应该是不支持的(?)。可以考虑在GUI模式中将文件(可以整个目录)加入进去,然后再export成为Tcl脚本,这样会得到如下图所示的样子:

更多的数字设计验证点点滴滴知识参见:常用数字设计仿真工具(Questa,VCS,IUS/Xcelium,Verdi等)使用入门