4.1

引言

本章基于第二章的分析结论,进行系统软件设计。软件设计包括逻辑设计、嵌入

式软件设计和上位机软件设计。在逻辑设计中,对

ADC

模块、

Aurora

模块、

DDR3

SDRAM

模块和

PCIE

模块进行分析和设计,在

Vivado

软件提供的

IP

核的基础上进

行各模块的逻辑代码的编写,并解决各个模块之间数据连接的问题;嵌入式设计是对

系统和内核的移植,并在

Zynq

的

PS

内核实现系统的启动;在上位机设计中,首先

介绍驱动开发工具,再介绍上位机的整体设计。

4.2

逻辑软件设计

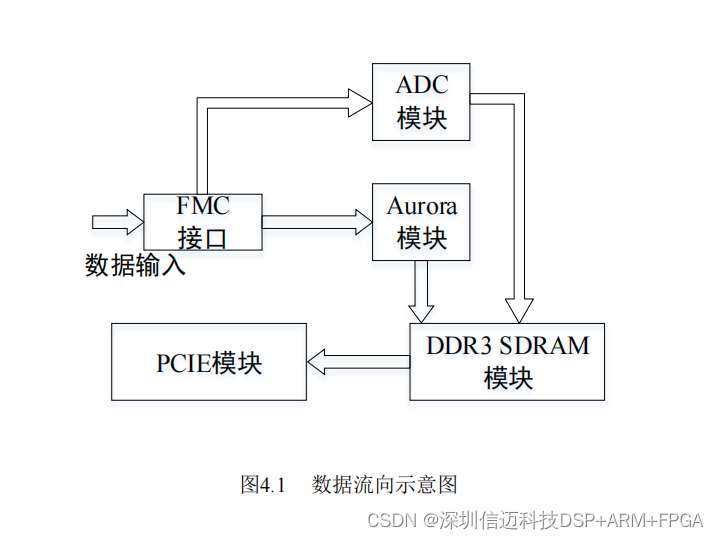

由于载卡的

FMC

接口数据与接入的子卡类型有关,根据接入的子卡类型选择

ADC

模块或

Aurora

模块,当选择

AD

子卡时,使能

ADC

模块,当选择光纤子卡时,

使能

Aurora

模块。对应的模块数据经

DDR3 SDRAM

缓存后,再由

PCIE

接口发送至

PC

机,数据流向如图

4.1

所示。

其中,

ADC

模块是

AD

子卡的驱动程序,可提供

1Gsa/s

的采样率,数据分辨率

为

12bit

;

Aurora

模块是光纤子卡的驱动程序,采用

Aurora

协议,

4

通道,单通道速

率为

10Gbps

,总速率为

40Gbps

;

PCIE

接口采用

PCIE2.0

协议,

x8 模式,单通道速

率为

5.0Gbps

,总速率为

40Gbps

;

DDR3 SDRAM

模块用来实现对

Aurora

数据或

ADC

数据进行缓存。

Vivado

软件内提供

Aurora

、

PCIE

和

MIG

的

IP

核,分别为

Aurora

协

议、

PCIE

协议和

DDR3 SDRAM

提供接口解决方案,下面对各个模块进行详细设计。

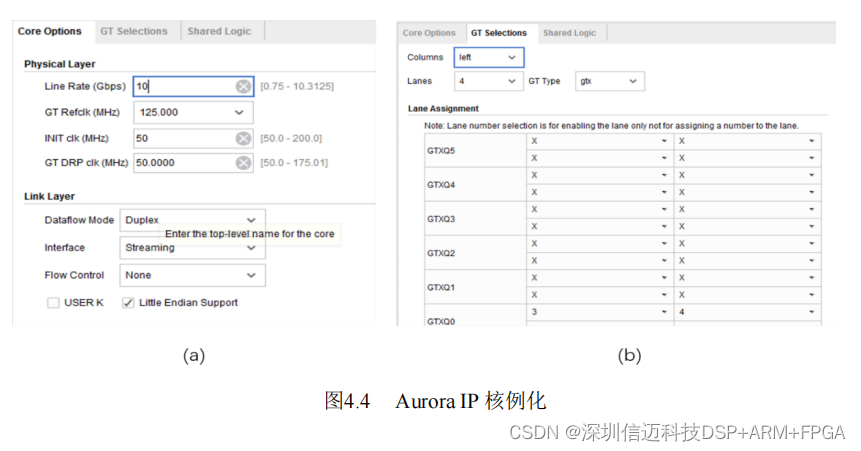

4.2.2

ADC

模块逻辑设计

AD

子卡的

ADC

芯片采样率最大为

1.6Gbps

。而在第二章指标分析中,

ADC

的

采样率不得低于

706.6Msa/s

,在本次设计中,设置

ADC

的采样率为

1Gsa/s

。

ADC

芯

片工作在双边沿采样的模式,这样采样率可以是采样时钟的两倍。需要产生

500MHz

的差分时钟信号,用

Zynq

芯片内部的

MMCM

资源可产生

500MHz

的单端时钟,再

利用

Xilinx

提供的

OBUFDS

原语把单端时钟转换成差分时钟输出。

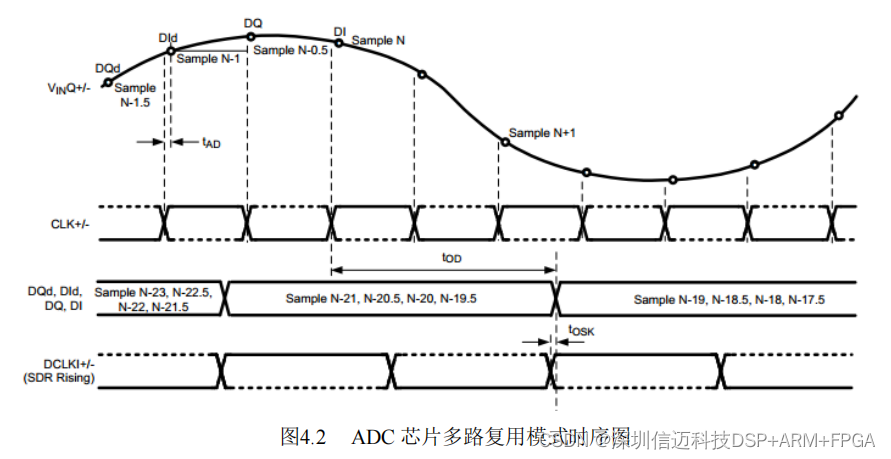

由于

ADC

工作在双边沿采样,需要拉高

ADC

芯片的

DES

引脚;信号耦合方式

是交流耦合,需要设置

VCMO

引脚为低电平。在双边沿工作模式下,

ADC

芯片可以

选择多路复用模式,多路复用模式可以实现数据线的复用,多路复用模式的时序图如

图

4.2

所示

[25]

。

图中,

CLK+/-

是采样时钟信号,

DQd

,

Did

,

DQ

,

DI

是

ADC

的数据线,

DCLKI+/-

是通道

I

的数据同步输出时钟。由图可知,

ADC

工作在双边沿采样模式,多路复用模

式时,完成

4

次转换后,数据依次轮流输出至

DQd

,

Did

,

DQ

,

DI

。同时在

DCLK+/-

上输出一个转换时钟二分频的信号,这里为

250MHz

。

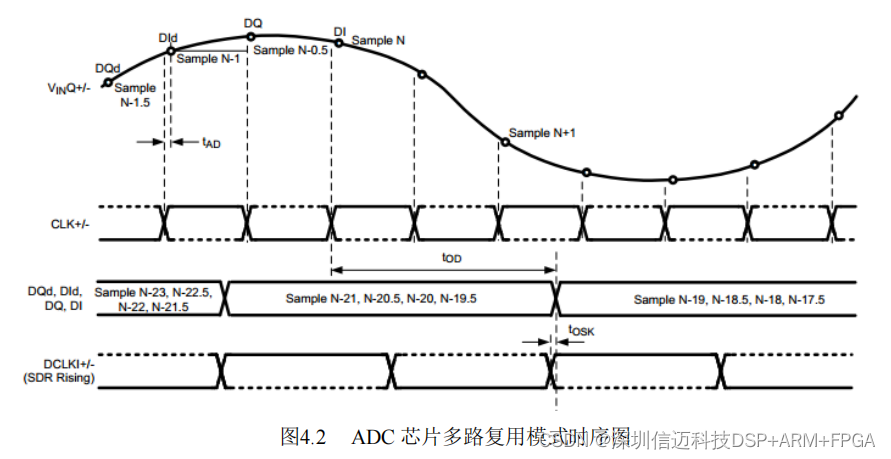

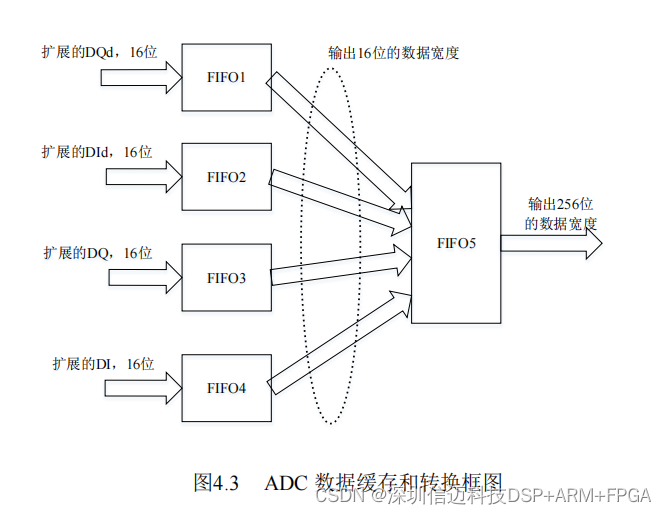

由于数据位宽是

12bit

,但是

DDR3 SDRAM

模块的

FIFO

宽度为

256bit

,两者不

成整数倍关系。这里解决办法是把各个数据通道的

12bit

扩展成

16bit

,然后分别保存

至小的

FIFO

里,再用一个

FIFO

输出

256bit

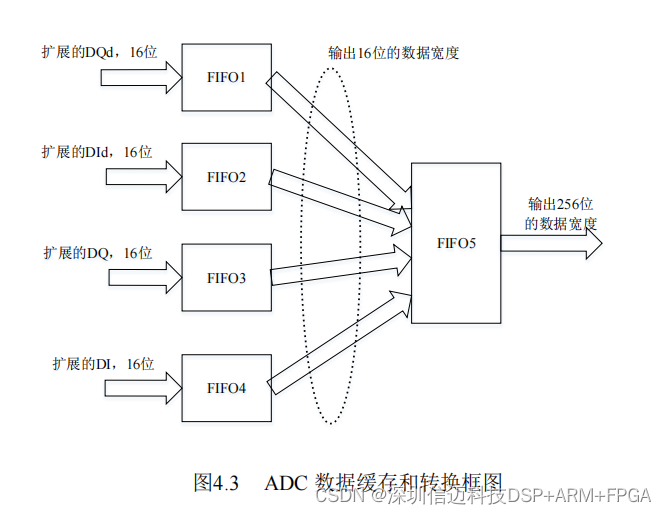

的数据宽度。数据流缓存框图如图

4.3

所

示。其中,

FIFO1~FIFO4

是读写位宽都为

16bit

的同步

FIFO

,

FIFO

时钟为

ADC 芯片

出来的

DCLK+/-

时钟,经差分转单端后的时钟,

4

个

FIFO

输出的数据写入至

FIFO5

里面,

FIFO5

是写数据位宽为

64bit

,读数据位宽为

256bit

的异步

FIFO

,可以直接与

DDR3 SDRAM

模块连接。

4.2.3

Aurora

协议逻辑设计

光纤接口采用

Aurora

协议,有

4

个通道,单通道速率为

10Gbps

,总速率为

40Gbps

。

光纤接口的数据传输时基于

Vivado

软件提供的

Aurora

协议的

IP

核实现,该

IP

核有

8B/10B

和

64B/66B

两种,分别对应相应的编码方式。本设计采用

64B/66B

编码,增

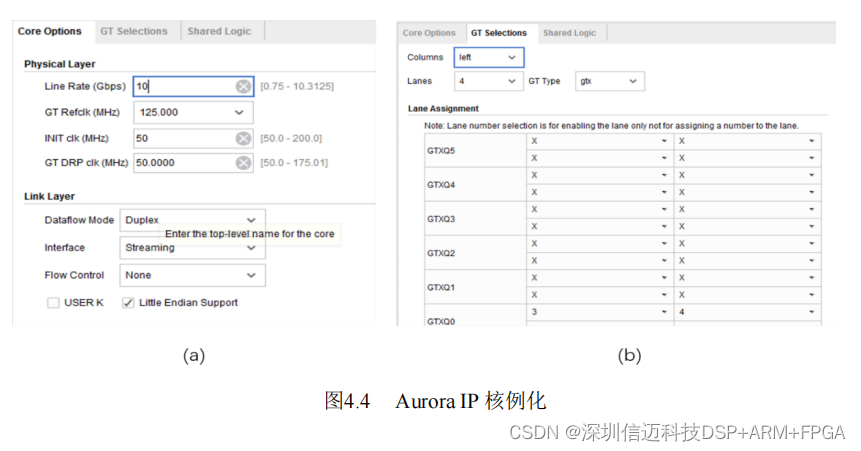

加了带宽利用率。核例化过程如图

4.4

所示。

例化核时,首先指定传输速率,这里设置为

10Gbps

。根据硬件电路设计,这里

的参考时钟设置为

125MHz

,传输采用全双工流模式,方便设计和使用。然后指定通

道在芯片上的映射关系。

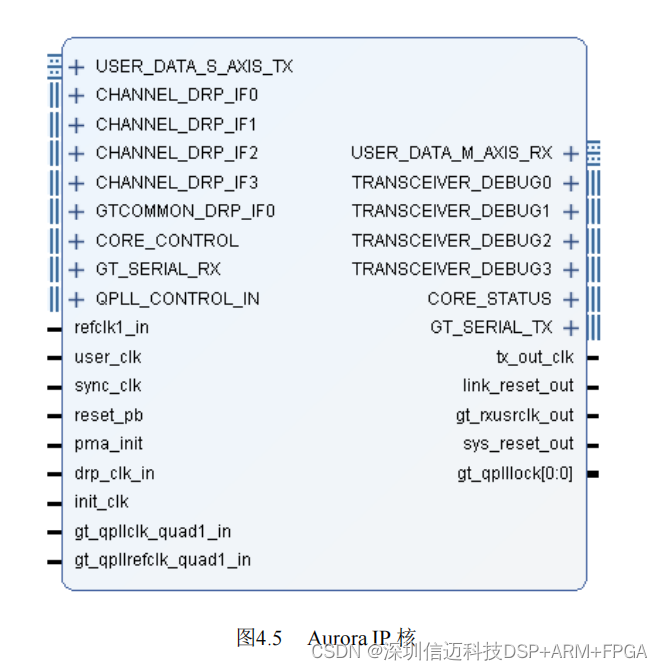

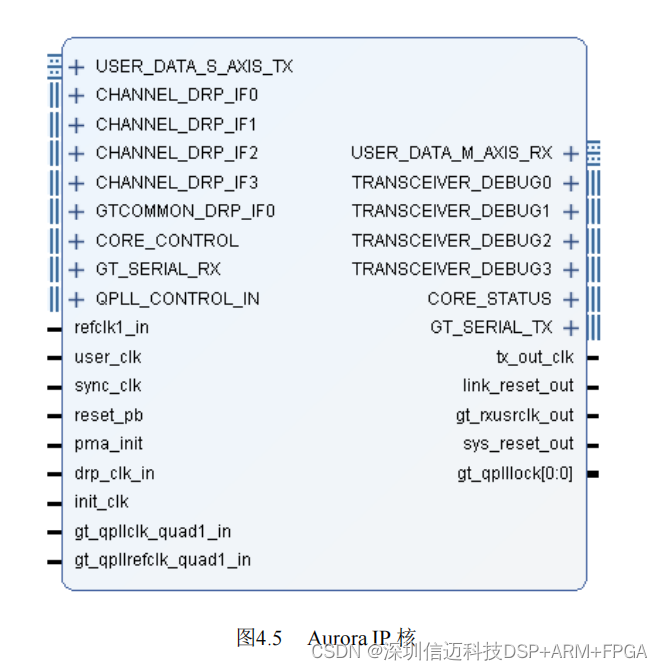

例化后的核如图

4.5

所示。

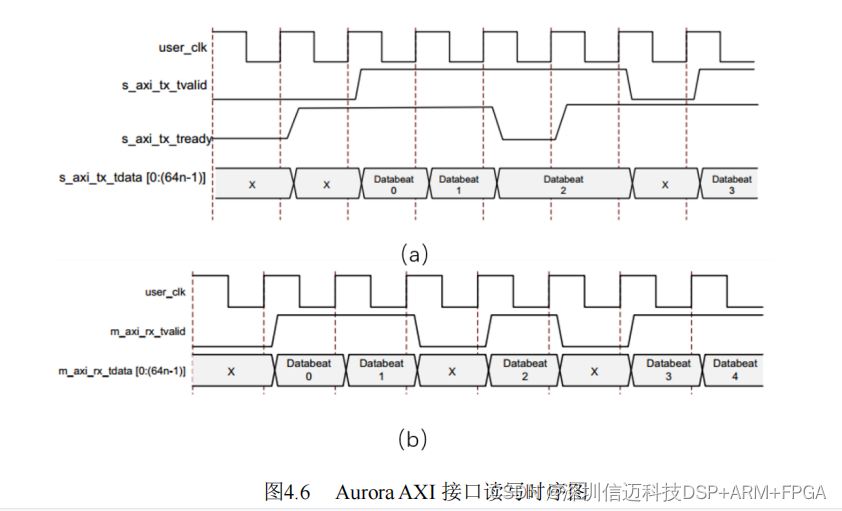

Aurora IP

核采用

AXI

总线协议接收和发送数据,读写时序符合

AXI

总线协议,

数据位宽为

256bit

。

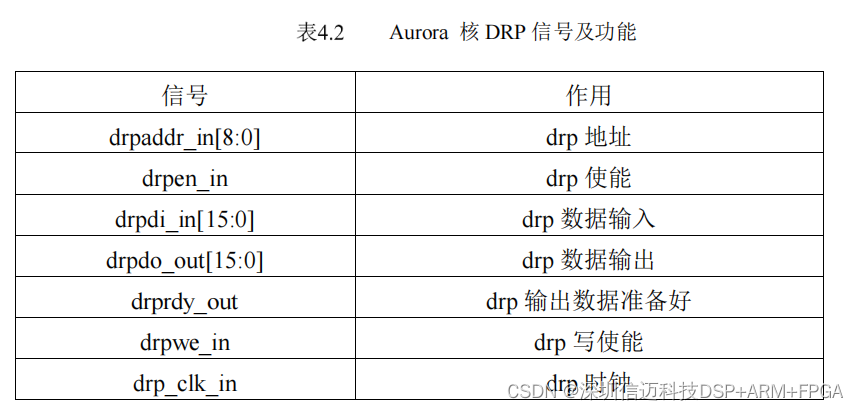

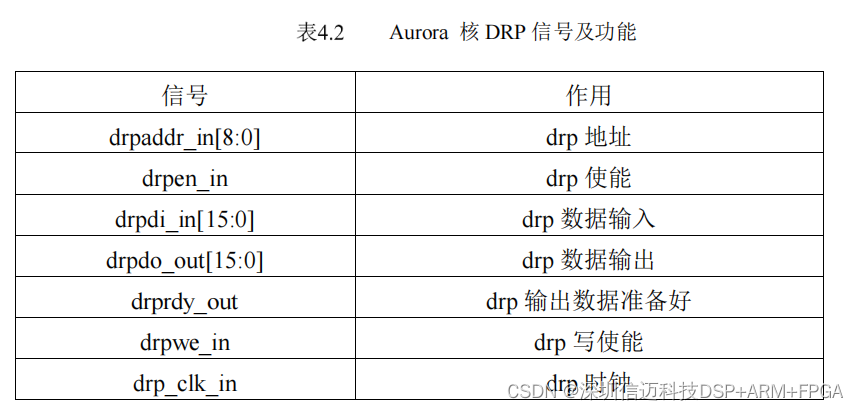

DRP

配置用来设置通道速率和配置参数,

DEBUG

信号包含通道

状态和眼图测试等,可作为调试观察使用。

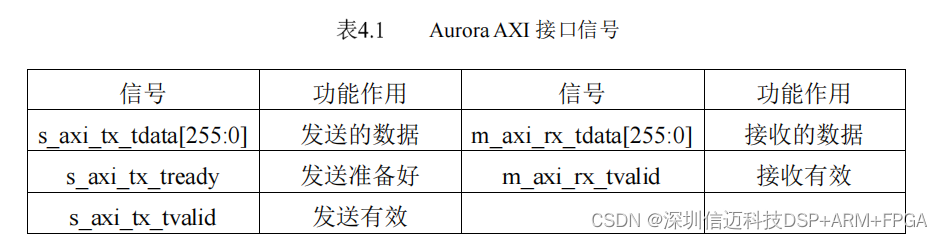

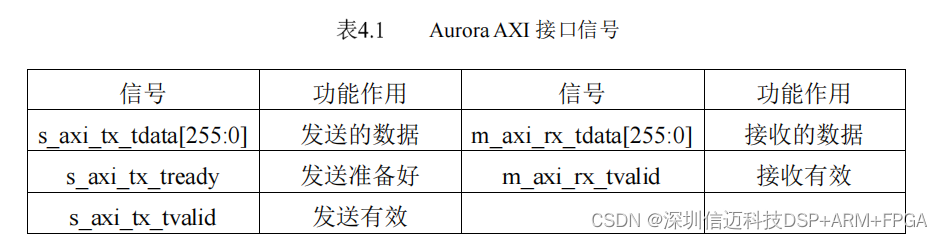

Aurora IP

核的

AXI

接口信号及功能如表

4.1

所示。

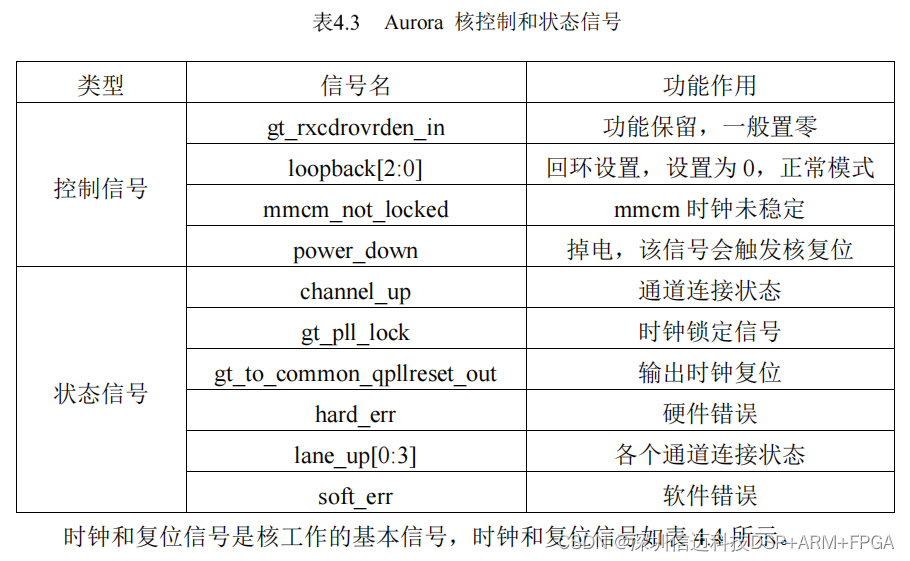

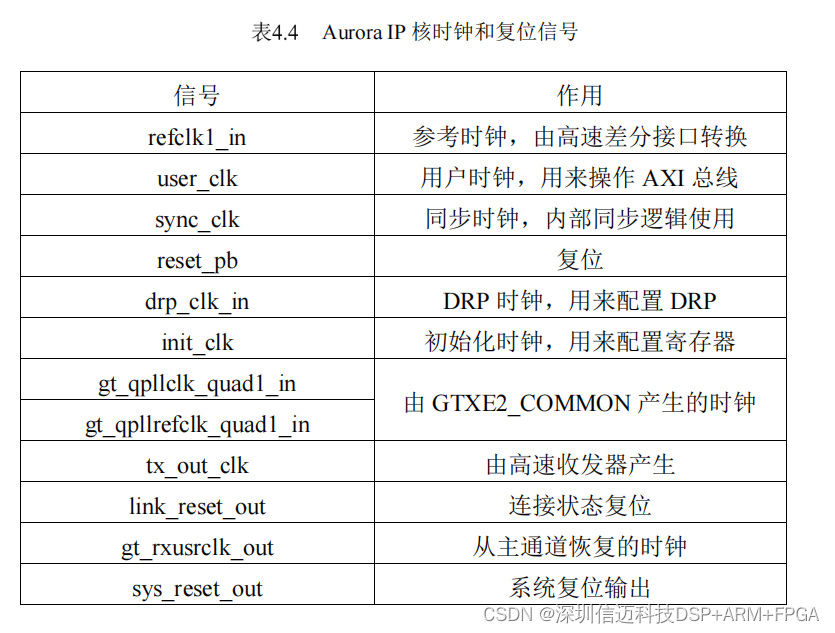

Aurora

的编码方式是

64b/66b

编码,单通道数据宽度为

64b

,因此

4

个通道数据

位宽为

256b

,传输方式是流模式,不需要帧结尾信号和有效字节信号,因此

AXI 接

口没有

_tkeep

和

_tlast

信号。

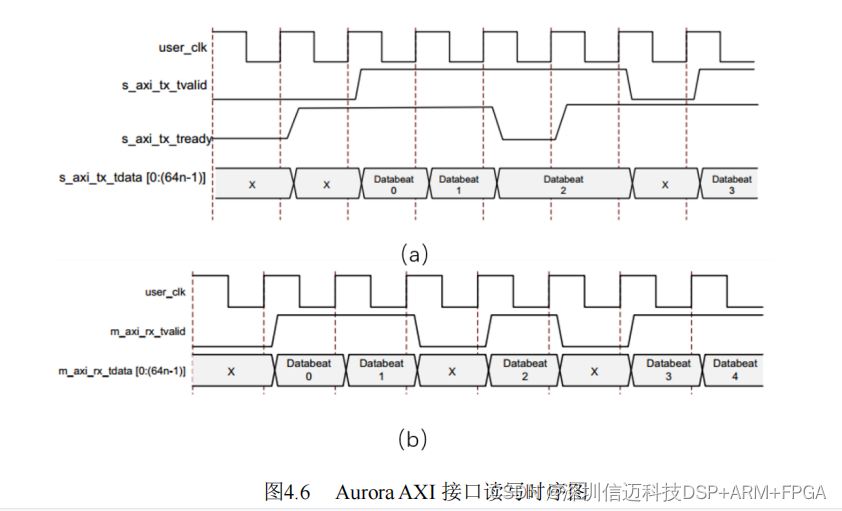

Aurora IP

核

AXI

接收和发送时序图如图

4.6

所示

[26]

,其中图(

a

)是发送时序,

图(

b

)是接收时序,

n

是通道数,这里

n=4

。

在实际使用中,

Aurora

的传输速率和参数一般固定不变,因此

DRP

不用配置,

在

IP

核里面有四组

DRP

端口,分别对应四个

Aurora

通道,以第一通道为例,

DRP

端口的信号作用和配置如表

4.2

所示

Aurora

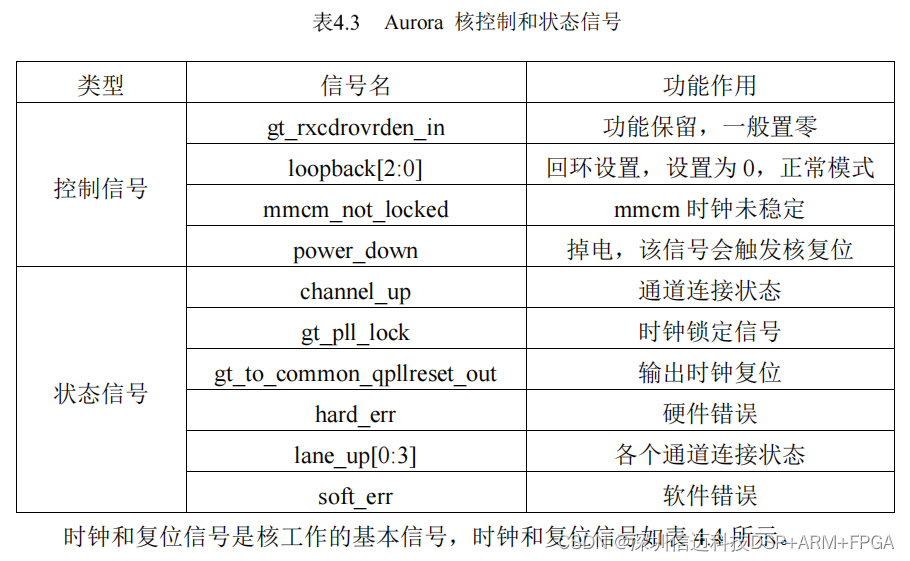

核包含控制和状态信号,控制信号用来设置回环、掉电等功能,状态信号

显示了通道连接状态、复位和软硬件错误等。控制信号和状态信号的作用如表

4.3

所

示。

Aurora

设计同样使用

FIFO

作为模块间的接口,由于

AXI

接口数据位宽为

256bit

,

FIFO

设计为

256bit

宽度,数据由上行

FIFO

进入至

Aurora

核,再经下行

FIFO

接入

至下游模块。

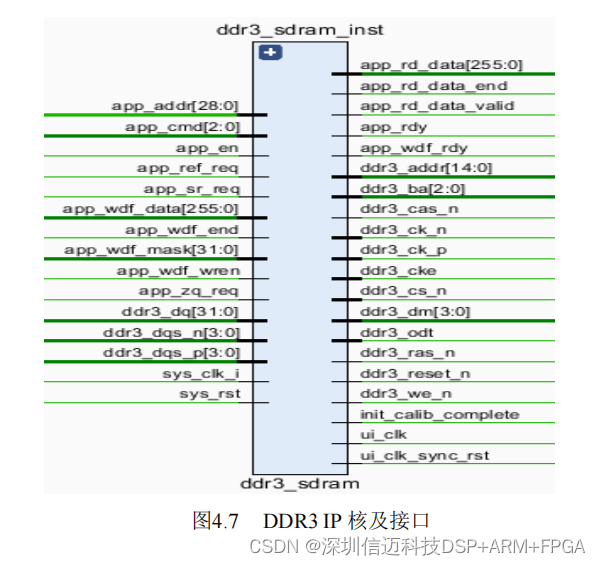

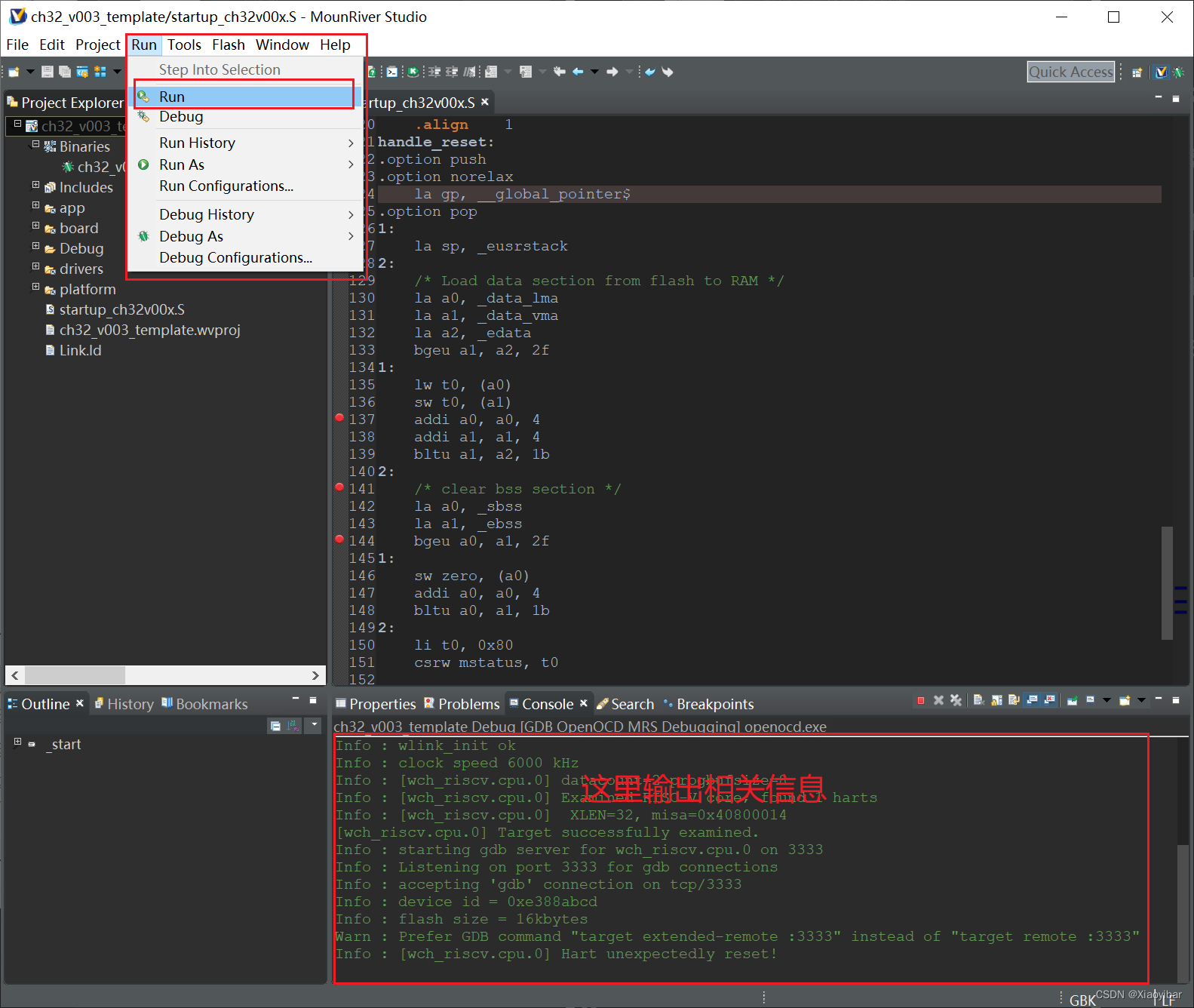

4.2.4

DDR3 SDRAM

逻辑设计

通常情况下

DDR3 SDRAM

用来作为数据缓存使用,基本原理是向

DDR3 SDRAM

里面的某一范围的地址里面进行数据读写,最常见的是在

PC

机中,每一个应用程序

都会占用内存条中的某一块地址范围,这时,

DDR3 SDRAM

的地址是分块管理的。

在本设计中,为了满足雷达辐射源信号识别平台的数据缓存功能,对

DDR3 SDRAM

的所有地址都用来存放数据,使用

DDR3 SDRAM

的全部空间用来实现数据缓存功

能,实现一个大容量

FIFO

。

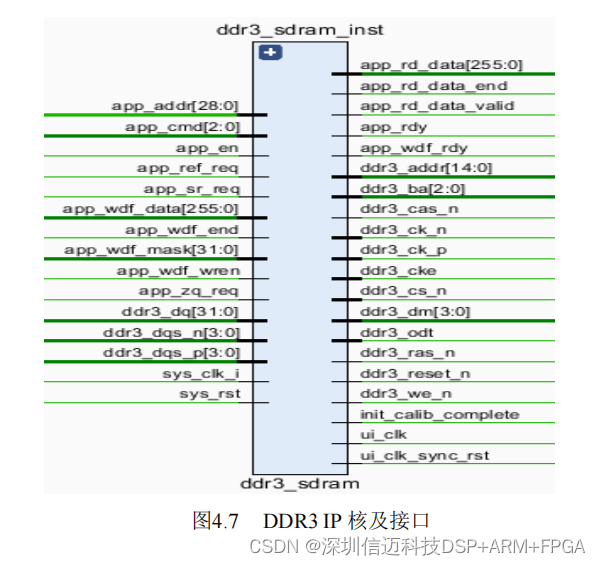

Vivado

软件提供了专为

DDR3 SDRAM

驱动的

MIG

核,

再加上外围驱动就可以对

DDR3 SDRAM

进行读写操作。采集卡使用两片

DDR3

SDRAM

,数据位宽为

32

位,地址位宽为

15

位。

例化

MIG

核时,首先设置

DDR3

的工作时钟和输出时钟比,这里设置工作为

600MHz

。

DDR3 SDRAM

数据位宽为

32

,理论读写速率为

38.4

。实际工作

中

DDR3 SDRAM

会刷新,使得速率低于理论值。接着是阻抗设置和地址设置。阻抗

设 置 是 为 了 匹 配 阻 抗 , 使 传 输 可 靠 稳 定 ; 地 址 设 置 有 两 种 , 一 种 是

ROW+BANK+COLUMN

,另外一种是

BANK+ROW+COLUMN

。其中

BANK

是由

DDR3

芯片的

bank

引脚给出,

ROW

和

COLUMN

是存储矩阵的行列,这由芯片特性

决定。然后给

DDR3

分配引脚,完成核的例化。

例化过程例化出来的

ip

核及接口如图

4.7

所示: