随着电网中非线性负荷用户的不断增加

,

电能质量问题日益严重

。

高精度数据采集系统能够为电能质

量分析提供准确的数据支持

,

是解决电能质量问题的关键依据

。

通过对比现有高速采集系统的设计方案

,

主

控电路多以

ARM

微控制器搭配

AD

转换芯片

、

ARM+DSP

搭配转换芯片以及

FPGA+DSP

搭配

AD

转换芯片

的架构方式

[1-5]

。

ARM

有着良好的决策控制特性

,

在工业控制领域被广泛应用

,

但其数据处理速度慢

,

不能满

足系统的实时性

。

由于

DSP

的串行指令流特性

,

复杂数据处理只能在低速系统中进行

。

FPGA

的全可编程

和并行数据处理特性使其在数字信号处理领域越来越受到青睐

,

但是对系统的决策能力较弱

[6-10]

。

同时

,

ARM

和

DSP

,

FPGA

与

DSP

之间通过低速工业通信接口

(SPI

、

Mcbsp

等

)

或者采用处理器外部总线接口连接

多芯片的结构

,

复杂化了板级电路设计

,

芯片间频繁通信难以保证系统的稳定性

[11-12]

。

对此

,

设计一种基于

ZYNQ

的数据采集系统

,

ZYNQ SOC

整合了

ARM

双核

cortext-A9

处理器和

Xilinx7

系列

FPGA

架构

。

片内集成高度定制的

AXI

互联和接口形成两个部分之间桥梁

,

加速了各模块间的通信且

加强了系统的稳定性

。

利用

FPGA

的硬件可编程特性设计出与高速

AD

连接的接口控制器

,

调用

AXI_DMA

官方硬核

IP

可直接将采集数据搬运至

ARM

的

DDR

中进行存储

。

ARM

驱动串口或者

HDIM

口完成数据显

示

,

执行系统的整体决策

。

经过对某变电所电能质量分析

,

发现稳态下电网高次谐波为

60

次左右

,

系统选用

的

AD7606

采集卡采样频率为

200 kHz

,

8

通道同步采集

,

分辨率为

16

位

,

采集精度和速度都能满足数据采

集系统设计要求

,

实现信号的模数转换

。

相对

ZYNQ

自带

XADC

的

12

位位宽

、

1 MHz

采样率

AD7606

有着

更高的转换精度

。

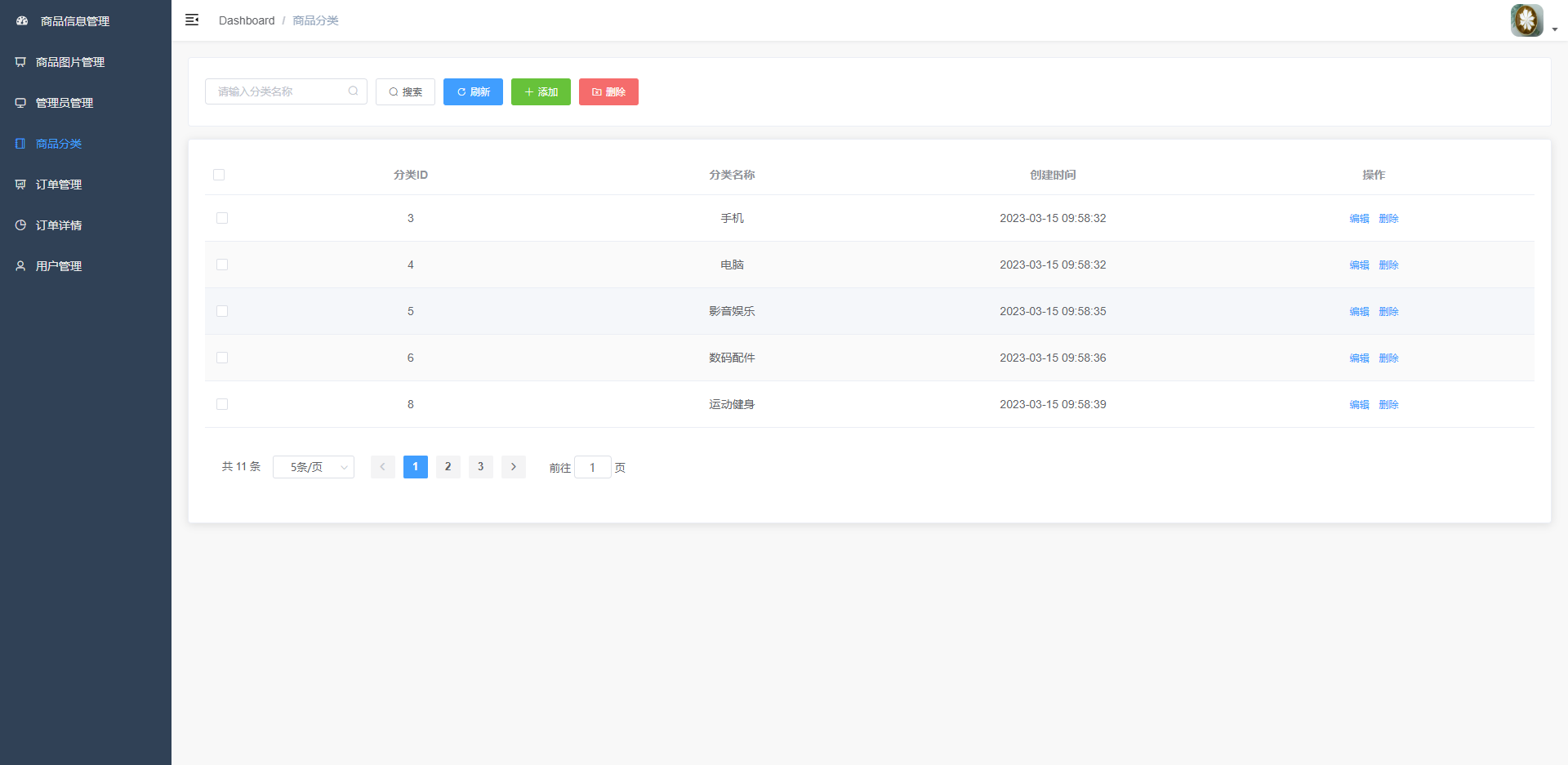

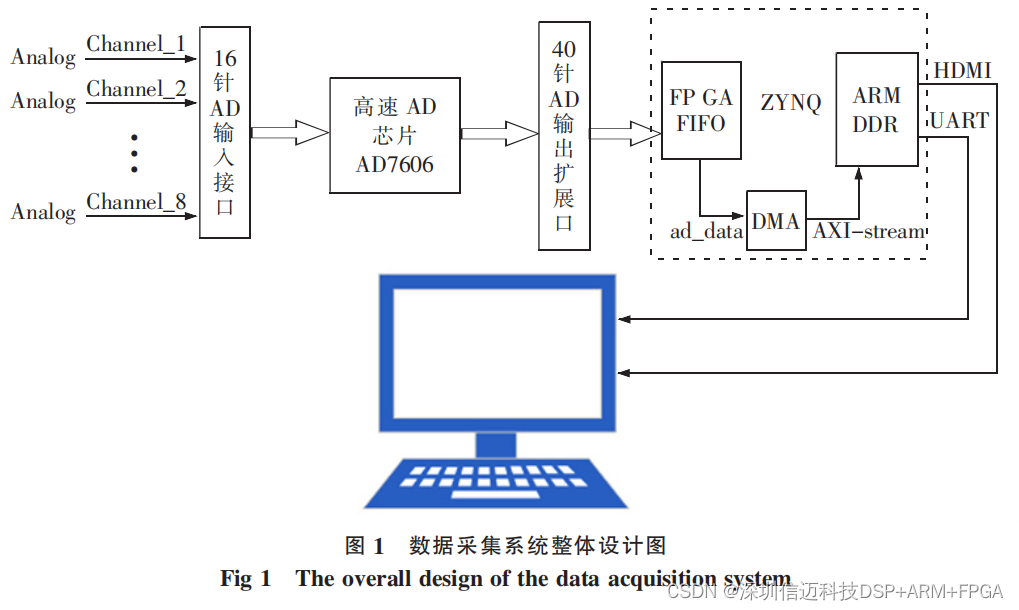

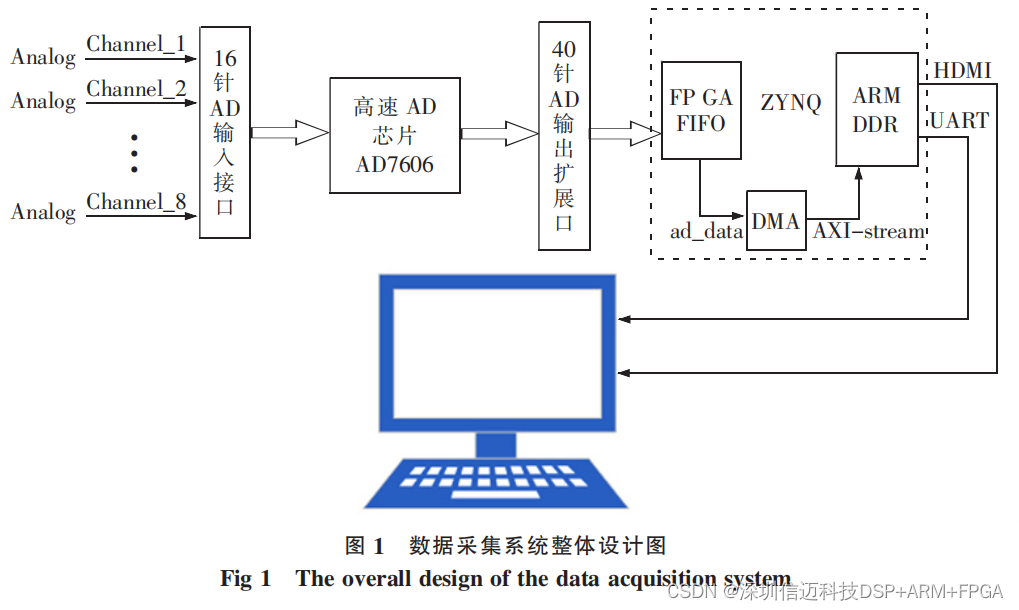

1

数据采集系统的整体设计

图

1

为系统的整体设计简图

,

AD7606

采集卡输入端引出了

16

针接口

,

分别用于

8

通道连接外部模拟

信号线路的

VP

和

VN

。

模拟信号进入

AD

采集芯片内

,经过模拟多路复器输入转换电路完成模拟信号到数

字信号的转换

。

系统通过

40

针扩展口实现

AD7606

与

ZYNQ

的高速通信

。

接口位于

ZYNQ

的

PL

部分

,

采用

Verilog

代码编写接口控制器程序实现

AD

采集控制功能后封装为

IP

核

,

主要设计包括

AD

的复位

、

时钟

、

采

样率

、

片选

、

FIFO

数据缓存器以及

AXI

协议例化

。

调用

Xilinx

官方

IP

核

AXI-DMA

将

PL

数据传输至

PS

的

DDR

存储器中

。

ARM

驱动

URAT

或者

HDMI

端口将数据传输给终端显示出来

。

AD

控制器先将采集数据缓

存到

FIFO

中

,

从

FIFO

中读出数据后转换为

AXI-stream

流数据格式

,

如此可以加快数据处理速度

,

降低数

据对时序的影响

,

系统采用

AXI-stream register slice

模块提升接口时序

。

系统采用异步时序设计

,

ADC

配置

时钟频率为

50 MHz

,

AXI

总线时钟为

100 MHz

,

数据显示时钟为

150 MHz

,

按照输入到输出倍增的方式设

置时钟

,

可有效防止缓存模块的数据溢出

。

2

数据采集系统的硬件设计

2.1 ZYNQ

简介

ZYNG

是

Xilinx

推出的新一代

(

all-programmable system-on-chip

,

SoC

)

全面可编程片上系统

。

本质特征

是组合了一个双核

ARM Cortex-A9

处理器

,

简称

PS

和一个传统的现场可编程门阵列

(

field programmable

gate array

,

FPGA

)

逻辑部件简称

PL

[13]

。

芯片集成了

AMBA AXI4

互联

,

内部存储器

,

外部存储器和外设

。

外设

主要包括

USB

总线

、

以太网

、

SD

接口

、

UART

接口

、

HDMI

口

、

GPIO

口等

[14-15]

。

具有高达

6.25 MHz

的逻辑单元

以及

766 MHz

的内部时钟

,

能够实现硬件加速和可扩展性

,

充分满足了系统设计的实时性和高精度

。

2.2 AD7606

控制器设计

AD7606

采用

+5 V

单电源供电

,

片内集成输入放大器

、

过电压保护

、

二阶模拟抗混叠滤波器

、

模拟多

路复用器

、

16

位

200 kbps SAR ADC

和一个数字滤波器

,

2.5 V

基准电压缓存以及高速串行口和并行口

,

可

实现

8

通道同步采样

,

所有通道均以高达

200 kbps

的吞吐率采样

[16]

。

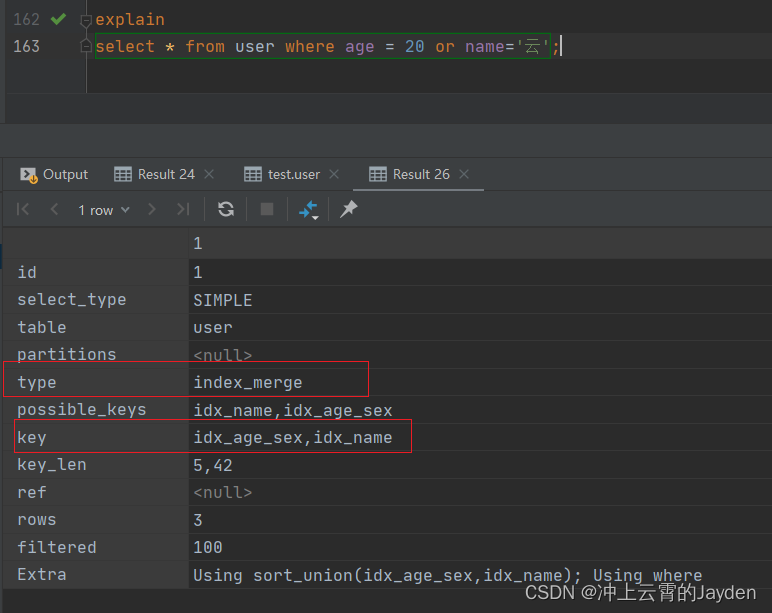

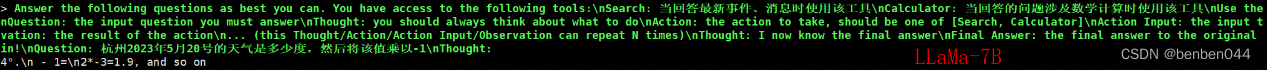

AD

控制器如图

2

所示

,

外部信号通过

ad_data[15

∶

0]

端口进入

AD

控制器

。

未连接的端口采用

Verilog

代码编程控制

,

根据时序特性设计转换过程

,

ad_convstad

端口信号上升沿启动时

8

通道同步采样

,

端口

ad_busy

为高电平时表示信号正在转换

,

当端口

ad_busy

信号为下降沿时表示

ad_rdd

读信号端口可以启动

,

控制器可读取数据总线中

8

个通道的采集数据

。

ad_cs

端口控制数据读片选

。

ad_os

为

AD

内部数字滤波器采样倍率选择端口

,

共有

8

种倍率选择

,

控制器可

以通过此端口选择是否使用滤波器

,

以达到更高的测量精度

。

系统通过

DMA

将

ADC

采集数据传输到

DDR

中

,

端口

M00_AXIS[15:0]

为数据输出通道接口

,

传输数据为流式数据

,

在设计时需要将

ADC

数据转换为

AX

IS

流数据

。

由于

ADC

时钟与

AXIS

的时钟频率不同

,

需要在

ADC

中添加

FIFO

进行跨时钟域处理

,起到缓冲

的作用

,

AXIS

时钟频率是

ADC

时钟的两倍

,

所以不会发生数据溢出的情况

。

ARM

配置

adc_clk

时钟端口

,

adc_rst

和复位端完成采集的时序及复位控制

。

2.3

采集系统通信

系统分为内部通信和外部通信

。

内部通过

AX4

总线进行通信

,

包含

5

个独立的传输通道读地址

、

读数

据

、

写地址

、

写数据

、

写回复

,

这些通道都支持单向传输

,

包括

AXI4

、

AXI-Stream

、

AXI-lite 3

种接口

,

系统数

据从

AD

到

ZYNQ

单向传输

;

因此只开启了写通道

。

DMA

采用的

AXI-Stream

接口

,

主从设备间能够直接进

行数据的读取

,

数据传输不需要地址

,

提高了系统的实时性

。

AXI

协议中主设备和从设备通过握手信号建立

连接

。

如图

3

所示

,

使用

UART

接口与外部通信系统采用

Silicon Labs CP20102GM

芯片实现

USB

接口转

UART

接口的功能

,

并采用

micro USB

线与终端进行串行通信

。

UART

接口的

TX/RX

信号与

ZYNQ PS

的

BANK501

信号相连

,

BANK501

的

VCCMIO

电平为

1.8 V

,

而

CP2102GM

的数据电平为

3.3 V

,

系统中间接入

TXSOQ02DCUR

电平转换芯片实现电平匹配

。

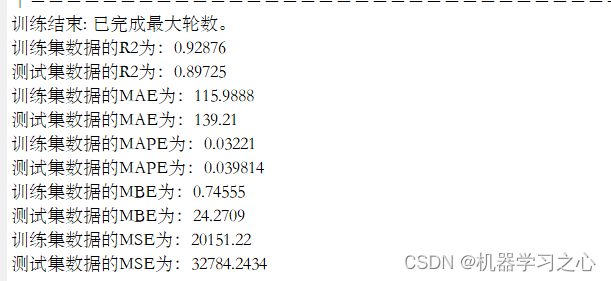

2.4 DDR

高速存储

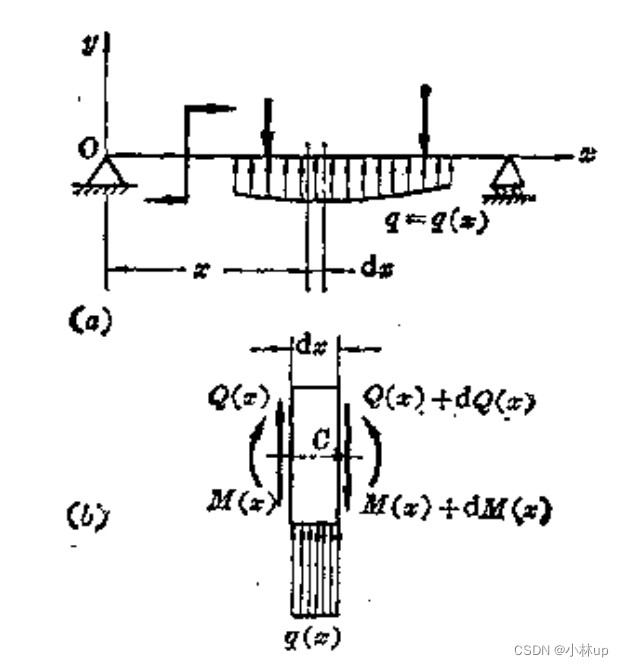

图

4

为

DDR3 DRAM

硬件连接示意图

,

DDR

是双倍速率同步动态随机存储器

,

数据在工作时钟的

上升沿和下降沿都会进行采样

,

有效提升了存储速率

。

系统配有两颗

4 Gbit

的

DDR3

芯片

,

型号为

H5TQ4G63ARFR-PBC

。

DDR

总线位宽为

32 bit

,

最高运行速度可以达到

533 MHz

。

DDR3

存储器直接与

ZYNQ

处理器的

BANK502

存储接口相连

。

ZYNQ-Processing System

核配置存储器时

,

必须确保

DDR

接口型

号一致或者兼容

。

3

数据采集系统的软件设计

Xilinx IDE

套件中

,

在

vivado

完成硬件工程设

计的基础上

,

SDK

会自动配置一些重要的参数

,

分

为

3

个模块

:

硬件定义

(

hardware definition

)

包含定

义的寄存器类型

、

地址映射以及当前设计包含的

IP

块信心

;

板级支持包

(

board support package

)

包含支

持

IP

块的驱动程序和变量参数头文件

;

应用程序

(

application

)

用于测试不同的功能

。

据此完成系统

软件部分设计

。

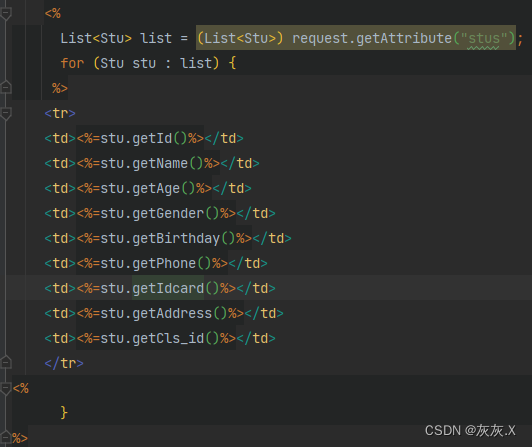

3.1 ADC-DMA

控制

ADC-DMA

控制是系统软件核心模块

,

程序运

行前对

ADC

和

DMA

相关参数进行初始化设置

,

如

ADC

的括基地址

、

偏移地址

、

采集长度

、

系数

、

字节

数

、

位数和通道数

。

DMA

最大传输字节数

、

设备

ID

、

中断

ID

和中断触发源

。

ADC

数据写入

FIFO

中是

按照

1

至

8

通道顺序存储

,

程序定义了二维数组

,

将每个通道的数据独立出来

,

并调整了通道顺序

。

为了在屏幕上显示所有通道数据

,

系统将每个通道

的系数进行了微调

,

使各通道波形形成错位

。

DMA

的中断触发类型为完成触发

,

此中断属于

ZYNQ

的

共享中断

,

触发机制为当任务执行完成后触发

,

硬

件设计中

DMA

只开起了写通道接口

,

中断函数只

打开

Streams

到

Memery Map

中断

。

SDK Terminal

的接口

、

波特率和数据位配置后

,

应用

printf

函数驱

动串口通信完成终端数据显示

。

同时可以通过

HDMI

接口与显示器相连

,

实现波形的实时显示

。

ADC

控制流程图如图

5

。

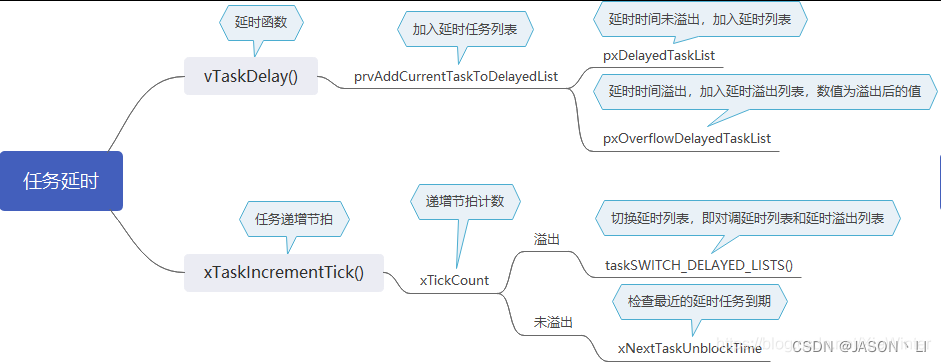

3.2 DMA-SG

模式应用设计

DMA-SG

模式相对简单模式有着更高效的数据传输特性

,

允许一次单一

DMA

传输访问多个内存空间

,

所有任务结束后才触发中断

。

硬件工程开启

SG

模式后引出

M_AXI_SG

接口

,

用于读写链表

。

链表以

13

个寄

存器组成的描述符为基本单元

。

描述符中包含下一个描述符指针地址

、

数据缓存地址

、

控制存储信息等

。

写

通道

SG

模式驱动设计流程如图

6

所示

,

需要在内存中开辟缓存空间和链表制作

。

将第一个描述符写入当前

地址寄存器

。

启动

DMA

并建立中断系统

,

传输结束后会触发中断

。

将最后一个描述符写入结尾结存器

,

触发

DMA

通过总线抓取链表描述符

,

BD

包传输完成后读取下一个描述符

。

将最后一个描述符指针只指向第一

个描述符的地址

,

匹配回环模式

。

数据处理完成后

,

清除链表状态

。

3.3

显示控制模块

该模块提供了易于使用的

API

,

控制显示器通过

VGA

或

HDMI

连接到系统开发板上

。

根据显示器分辨

率大小设置画布大小

、

背景和颜色

。

在画布中取长方形区间作显示波形的幅值和传播时间

。

区间内设计

32

×

32

像素点的小方格作为量化单位

,

水平和垂直方向每隔

4

像素点显示一次

,

网格显示为灰色

,

背景显示为

黑色

。

设计网格叠加函数和波形叠加函数对画布缓存区的数据进行实时读取

,

实现波形的不间断显示

。

Catch

中读取的数据在图像上显示为离散点

,

将数据与前一个数据进行比较

,

得出差值并在同一列描点

,

使

波形显示更为平滑

。

可以通过修改波形起始位置参数改变波形区域的大小

,

但列起始位置加上波形高度必

须小于显示器分辨率

,

否则无法正常显示

。

系统屏幕以彩条作为显示背景

,

设计了无缝帧缓冲器区

,

可实现

无痕动画

。

图像驱动流程如图

7

所示

。

首先要创建一个显示对象

,

并对其初始化设置

。

调用

DisplaySetMode

函数设

置传输模式

。

调用

DisplayStart

函数将数据传输到显示器上

。

要实现无缝动画

,

需要先将一张图像绘制到当

前未显示的帧缓存区

,

后调用

DisplayChangFrame

函数显示此帧

,

重复操作显示图像

。

若更改分辨

,

需调用显

示模式函数设置模式

,

然后

,

从新开始传输数据

。

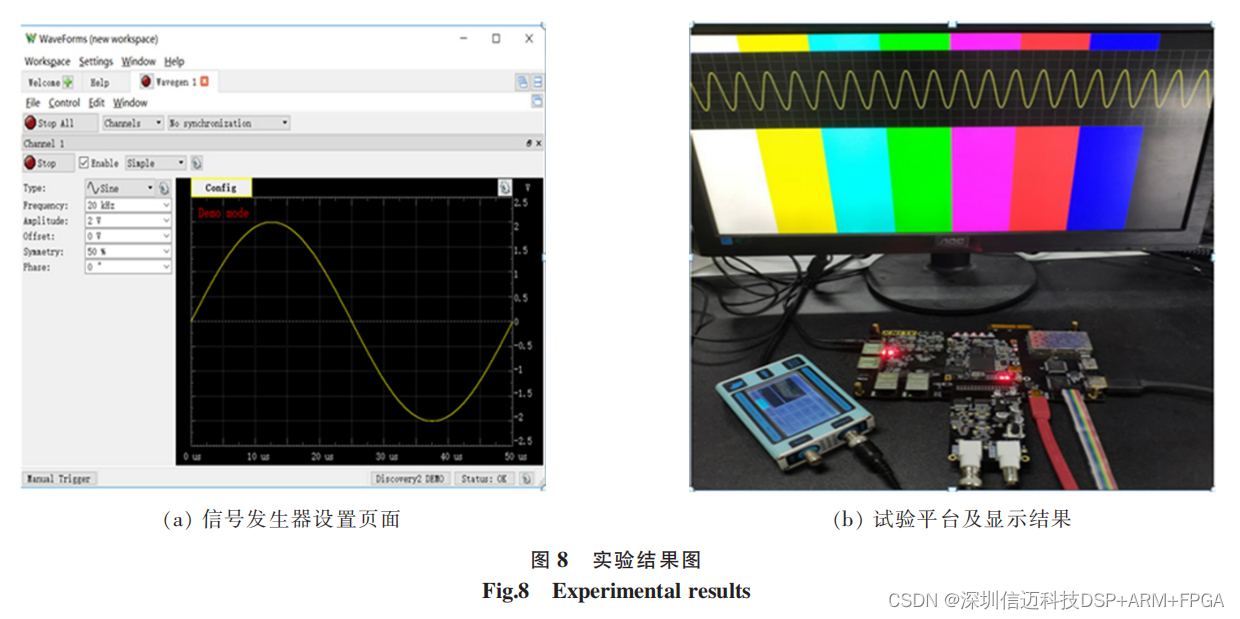

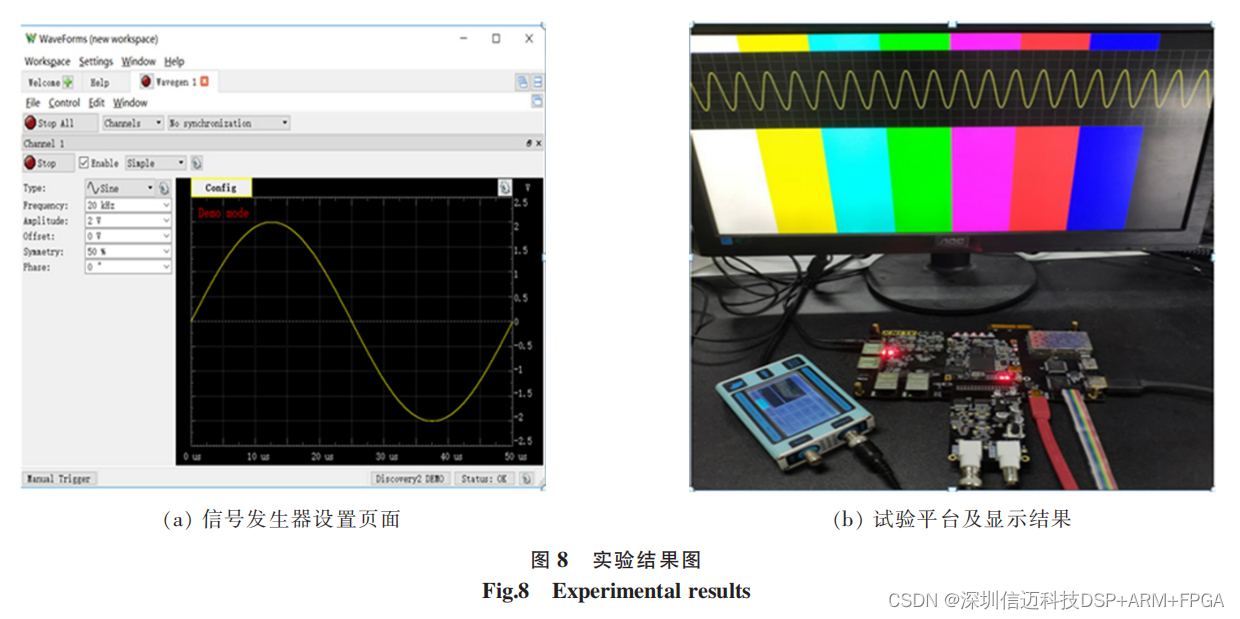

4

实验结果分析

采用

digilent

的

Analog Discovery 2

任意函数发生器提供所需的信号进行实验

。

图

8

(

a

)

为信号发生器设

置页面

,

实验对正弦信号

、

20 kHz

、

2 V

信号进行采集显示

,

AD

采样频率为

200 kHz

,

8

个采集通道全部开启

,

由于硬件条件限制

,

只进行了单通道实验

。

HDMI

显示结果以及试验平台如图

8

(

b

)

所示

,

图形界面显示的正

弦波即为系统采集信号

,

纵向分析

,

相邻虚线间距表示一个度量单位

,

波峰到波谷共经过

4 个单位表示

从

+2 V

到

-2 V

信号

,

分析得出实验结果和原始信号波形相同

。

为了进一步验证采集精度

,

实验进行了

8

通

道

4

个模拟电压值的测试

,

测试结果通过串口打印出来

,

如表

1

所示

,

第一列基准电压为信号发生器发出

值

,

后面

8

列为系统测量结果

。

根据式

(

1

),

计算出采集误差为

0.02%

。

针对电能质量检测领域的高速数据采集要求

,

利用

Xilinx

提供的

Vivado

开发套件在

ZYNQ SoC

上完成

高速数据采集系统的设计

。

该设计在硬件方面

,

借助

ZYNQ

的

FPGA

部分实现系统的采集控制

,

ARM

部分

完成数据传输

、

存储和结果显示

,

其中基于自定义

ad7606_sample IP

实现了

AD7606

的采集控制

,

利用

AXI

HP

高速接口

、

AXI-DMA

硬核

IP

、

DMA-SG

模式加快了系统的数据传输和处理速度

。

在软件方面

,

完成了

SG

模式下的

BD

包建立

、

波形显示设计及

DMA

数据传输控制

。

通过测试的实验结果表明

,

ARM

端驱动

HDMI

接口实现了采集信号的实时在线显示

。

通过对串口终端打印出来的数据进行分析

,

确定系统的采集误差可

达到

0.02%

。

系统具备体积小

、

功耗低

、

精度高

、

实时性强

、

稳定性强等特点

。