目录

1、EMIF调试

2、GPIO调试

前言不用多说,详见DSP篇--C6678功能调试系列之DDR3调试_nanke_yh的博客-CSDN博客

1、EMIF调试

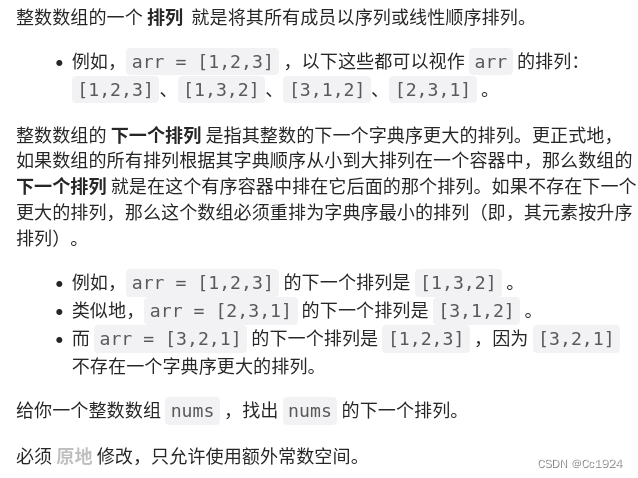

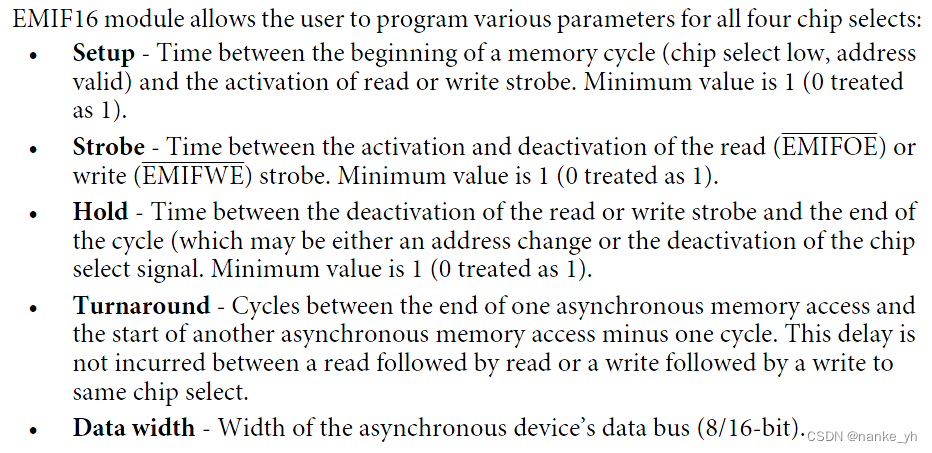

EMIF主要是提供挂载的NOR FLASH/NAND FLASH/**RAM上的时序。

EMIF16 can operate in the following modes:

• WE Strobe Mode

• Select Strobe Mode

EMIF16 is clocked at CPU/6 frequency. So, for a device running at 1GHz, EMIF16 is clocked at 166.67 MHz. All references to clock/clock cycles are in terms of EMIF16 clock cycles.

故,EMIF的初始化就是对以上几个参数进行配置。根据时序配置的参数表示对应时间长短。

例: /*configuraiton for the CE of NOR FLASH*/

gNorCeCfg.busWidth= EMIF_BUS_16BIT; //emif选择16bit

gNorCeCfg.opMode = NOR_ASRAM_MODE;

gNorCeCfg.strobeMode = SS_STROBE;// WE_STROBE\SS_STROBE

gNorCeCfg.waitMode = EMIF_WAIT_NONE;

gNorCeCfg.wrSetup = 0x0000000Fu;

gNorCeCfg.wrStrobe = 0x00000003Fu;

gNorCeCfg.wrHold= 0x00000007u

gNorCeCfg.rdSetup= 0x0000000Fu;

gNorCeCfg.rdStrobe= 0x00000003Fu;

gNorCeCfg.rdHold= 0x00000007u;

gNorCeCfg.turnAroundCycles= 0x00000003u;

gNorCeCfg.nor_pg_Cfg= NULL;

gEmif16Cfg.ceCfg[0] = &gNorCeCfg; //配置CE0(total 4)其测试成功标志是挂载的外部flash等能正常读写!!!

2、GPIO调试

In addition, the GPIO peripheral can produce CPU interrupts and EDMA synchronization events in different interrupt/event generation modes.

To use the GPIO pins as sources for CPU interrupts and EDMA events, bit 0 in the bank interrupt enable register (BINTEN) must be set to 1.

DIR:0-15个管脚,0为输出,1为输入

CLR_DATA:0 = No effect,1 = Clears the corresponding bit in Output Data register.

SET_RIS_TRIG:0 = No effect,1 = Sets the corresponding bit in RIS_TRIG.

SET_FAL_TRIG:0 = No effect,1 = Sets the corresponding bit in FAL_TRIG.

gpGPIO_regs->BANK_REGISTERS[0].DIR= 0xFFFF03FF;

//GPIO 0~9 输入; GPIO10~15: 输出;

gpGPIO_regs->BANK_REGISTERS[0].CLR_DATA= 0xFFFFFFFF; /*clear output data*/

//gpGPIO_regs->BANK_REGISTERS[0].SET_DATA= 0xFFFFFFFF;

gpGPIO_regs->BANK_REGISTERS[0].SET_RIS_TRIG = 0x0000FFFF;

gpGPIO_regs->BANK_REGISTERS[0].SET_FAL_TRIG = 0x00000000;

gpGPIO_regs->BINTEN= 1; //使能中断输入由FPGA更改输入相应管脚的高低信号,CPU通过查看寄存器来确认输入是否正确。输出则由CPU向相应管脚输出高低,通过示波器量出高低,确认CPU输出是否正常。