现今电子产品复杂度越趋增加,信号速度越来越快,在信号传输的过程中,如果信号不断反射便会对电子产品的运作造成影响,而这又与阻抗连续性以及阻抗匹配息息相关;而如何避免信号反射,除了在硬件设计时的规划外,在 PCB 设计时间针对信号传输路径进行分析和走线优化,并使传输信号的发送与接收端阻抗匹配,亦是确保产品性能良好的不二法门。

本文将介绍如何使用 Allegro IDA(In-Design Analysis,设计同步分析)的Reflection 分析功能,在PCB布线过程中同步进行信号反射分析,只要加载零件模型,EE 或 Layout 人员可以不需要依赖SI工程师,便能在设计中同步进行SI等级的信号反射分析,实时确认并修正PCB设计,以提升设计效率,并减少不良发生机率。

什么是Reflection?

PCB「信号传输线」上的意外回音

先前我们提到如何简单的利用Impedance分析来确认PCB上传输线的特性阻抗,现在是时候挑战巨人歌利亚,更深入地对信号做进一步分析了。

而什么是Reflection (信号反射)?

我们之前说到,将PCB上的信号线想象成自来水管,水在水管中流动。当水从比较宽的水管往下流动时,突然尾段水管变窄了,部分的水流无法继续前进,那就会往回冲了。同样的情况拿到PCB上来说,发送端与接收端阻抗不匹配就会造成信号的反射,此时接收端会将一部分电压反射回发送端,造成传输线中正在发送出去的信号与反射回来的信号彼此你侬我侬,互相干扰。此外,传输线经过过孔或是连接器,以及参考地平面不连续,也会造成信号反射。信号不稳定,系统工作就会不正常。

想象你对着空无一人的空屋叫喊,竟然听到不应该得到的响应,岂不吓死人。

为什么需要Reflection分析?

信号走线-失之毫厘、差之千里

一般在设计PCB时,Reflection(信号反射)常于以下几种情况发生:

1. 发送端与接收端阻抗不匹配。

2. 信号线宽改变导致阻抗不连续。

3. 传输线过孔或连接器导致阻抗不连续。

4. 信号线参考的地平面(GND)有壕沟(Moat)导致阻抗不连续。

以往EE/PCB Layout工程师在设计产品时,多半会沿用经验法则,或是使用其他分析工具做基本确认。但最多时候会需要专业SI人员帮忙对PCB Layout做实际模拟,得到精确的结果之后,再针对异常处做修正。而这一来一往的讨论与数据往返会耗费许多时间;尤其在交期赶的时候,SI人员火大,EE/PCB Layout人员苦不堪言,交期延迟,客户发飙。

PCB Layout 上的走线千百条,需要注意的地方太多,尤其信号频率越来越高,速度越来越快,有时候失之毫厘,差之千里,差那么一点点就会造成严重的影响;当客户不断要求修改设计的时候,有些细节更不能不注意,尤其是在会造成信号反射的部分。

在很多时候,Layout 上的走线已做调整,贯孔的部分也做了初步确认,该加上的电阻/电容也加上了;但对于更高速敏感的信号,我们必须看得更深入。这时候便会需要进一步为零件挂上Models,进行分析时才能有零件的行为,并得到更为精确的结果,最后做细部的修正。

如果这些细部分析在 PCB 设计端便能够执行,利用直观的辅助分析工具帮助工程师实时分析、实时检查、实时修正,将可大大减少错误发生的机会并减少各方讨论的时间。交期不延迟,大家都开心。

接下来我们将通过设计实例详解设计同步进行 Reflection 分析以避免信号反射:

如何执行 Reflection 实时分析信号反射

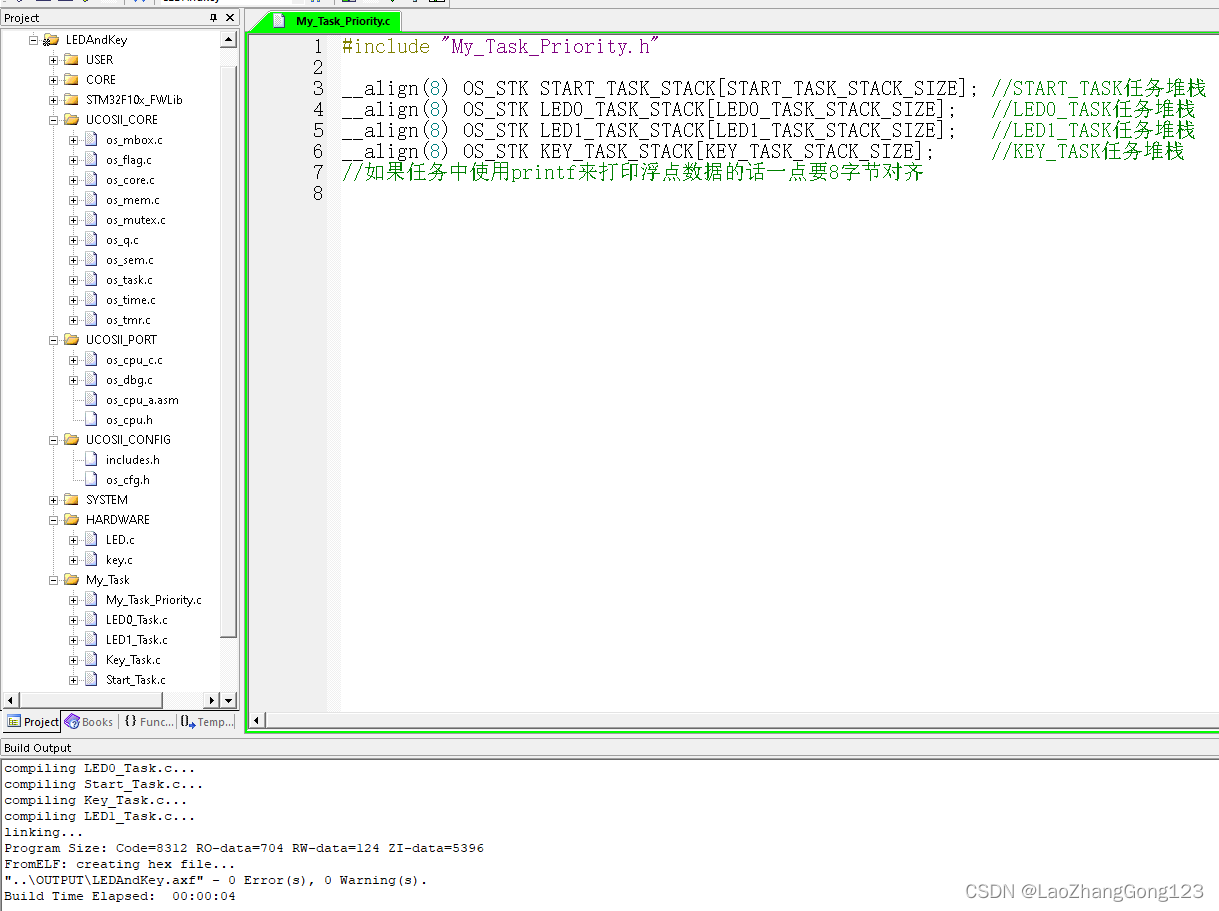

在开始执行分析之前,建议先把叠层设置(Cross section)中的叠层、层厚、介电常数、介质损耗等相关数据定义好,因为所有的分析结果都是基于叠构设置为基础做计算。接着我们就可以利用 Allegro中Analyze菜单里面的 Workflow Manager 来启动 Reflection 分析功能 (图 1)。

图 1. Workflow Manager

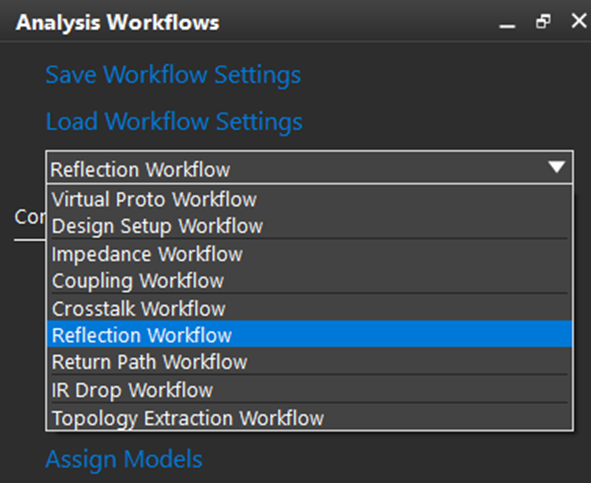

在 Workflow Manager 的下拉选单中选择 Reflection Workflow 分析功能。(图 2)

图 2. 选择Reflection分析流程

接着进行 Model 模型设置。

如同先前的 Crosstalk 分析,Reflection 信号反射和 Crosstalk 串扰分析流程一样需要设置Model 模型,才能得到更精准的 SI 分析结果。

[温馨提醒: 若同一个PCB文件在Crosstalk 分析中已经先完成 Model 模型设置,则可忽略下述步骤直接进行分析 Net 相关设置]

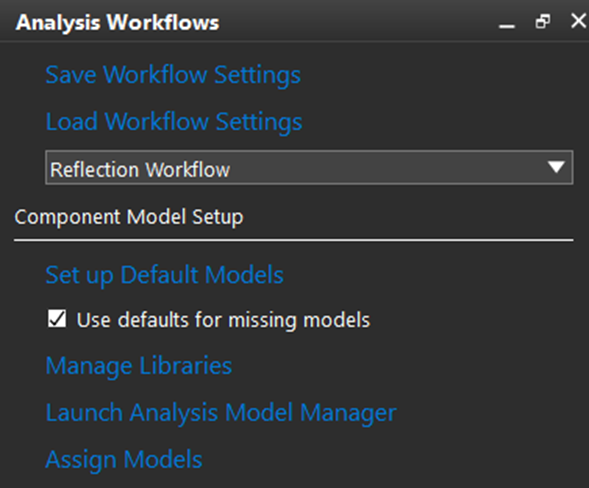

因此,我们一样先点选Workflow中的 Setup Default Model 来确认所指定的默认模型 (图 3)。

图 3. Default Model Setup 默认模型设置

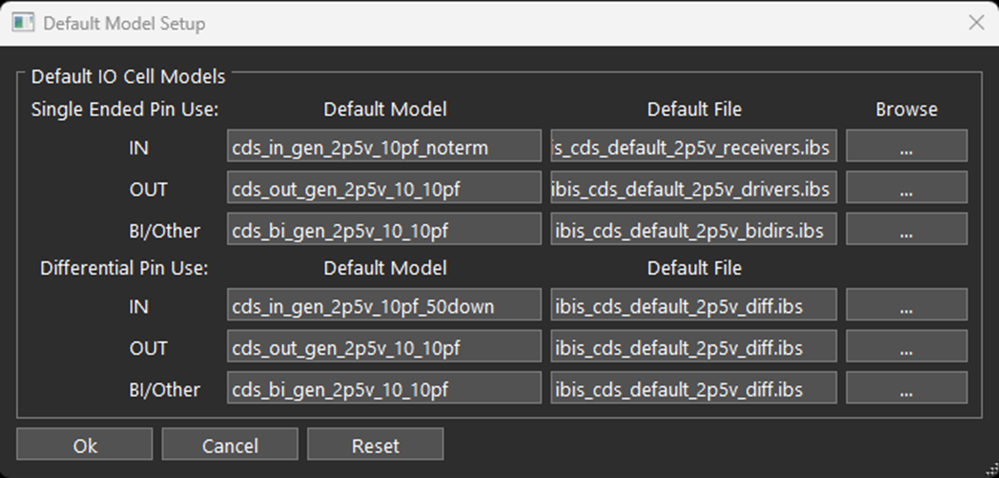

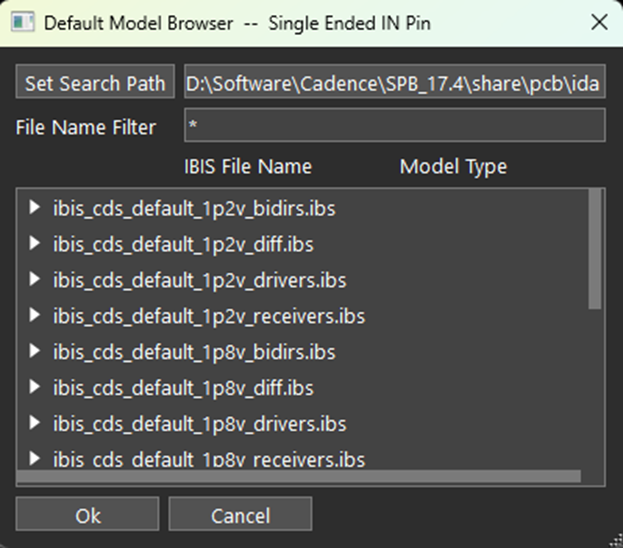

点选后会出现如下图(4)所示的对话框,此是在指定当没指定模型套用时所使用的内定 IO 模型(这项套用是在有勾选“Use defaults for missing models”项目时才有效)

图 4. 指定默认 IO 模型

【温馨提醒】

- 这些全部都是 IBIS 格式的模型,不会用到以前的 DML 模型

- 现在也支持差分信号的 BUFFER 模型

- 会根据 Pin Uses 的定义使判定更快速简化

- Pins会先判定成 In/Out或最后为 BI/Other类别

- 当 IC pins 不正确或未定义时会判定成 BI/Other类型

接着可点选 Browse 下方的 … 按钮,选择或调整所要的默认模型,如下图(5)所示,而其上方 Set Search Path 栏为安装好后所提供的相关默认 .IBS 文件来源路径,可视需求再依其名称选择 IBIS 档内的特定buffer模型(如不同电压或特性等) 。

图 5. 浏览默认模型和来源路径

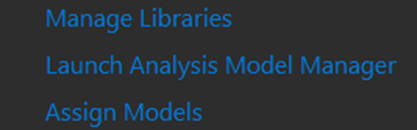

在 Workflow 选单还有三项零件模型设置功能(图 6) ,分别为 Manage Libraries 零件库路径管理、 Launch Analysis Model Manager 分析模型管理,以及 Model Assignment 模型指定,其重点说明如下:

图 6. 三种零件模型设置功能

► Manage Libraries 零件库路径管理

这跟 Sigrity 相关程序的零件库管理是相同的接口,可在不开启 AMM 的操作环境之下设置零件库。

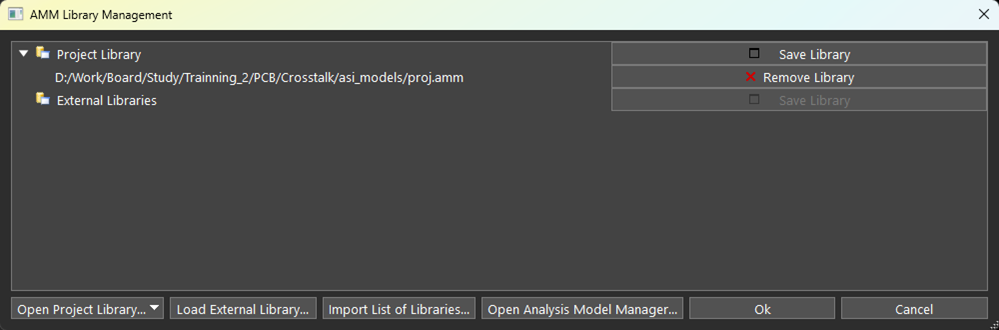

请注意! proj.amm 的 project library 文件是执行后自动建立的内库 (图 7),会建立在目前的工作路径下所建的“asi_models”子目录中,以便将所有相关的 MODEL 零件做统一管理,而不用列在 AMM 中做管理。

图 7. project library-执行后自动建立的默认库

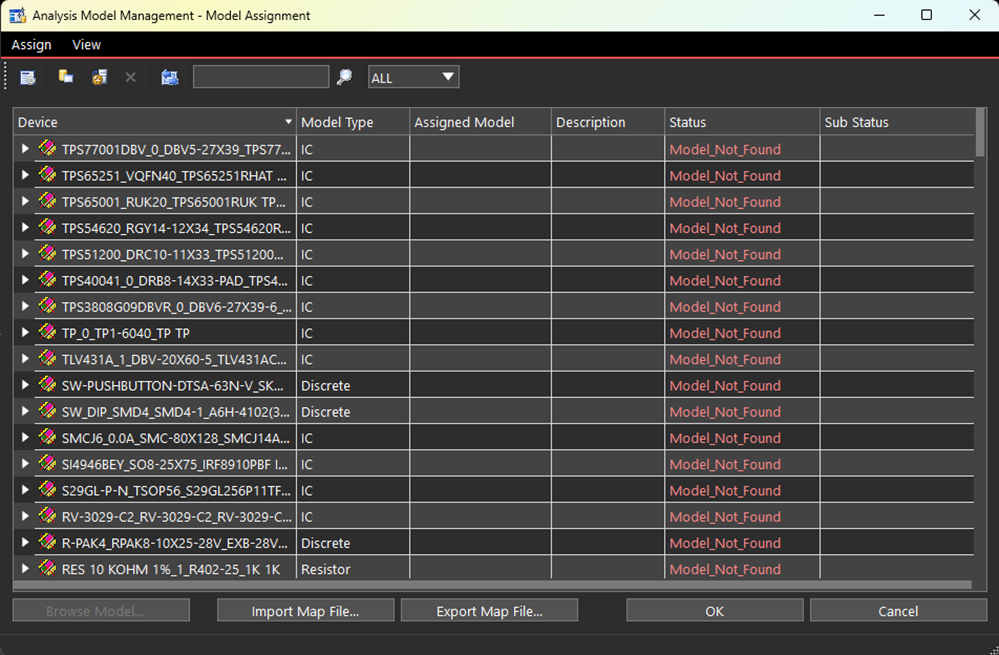

► Assign Model模型指定

如要指定模型,请点击 Assign Model进行指定。

在下图(8)这个表格的 Assigned Model 字段中会列出 Allegro 里有用 ASI_MODEL 属性所指定的模型对应名称,显示…的表示有多个不同的模型对应。

图 8.多重指定显示范例

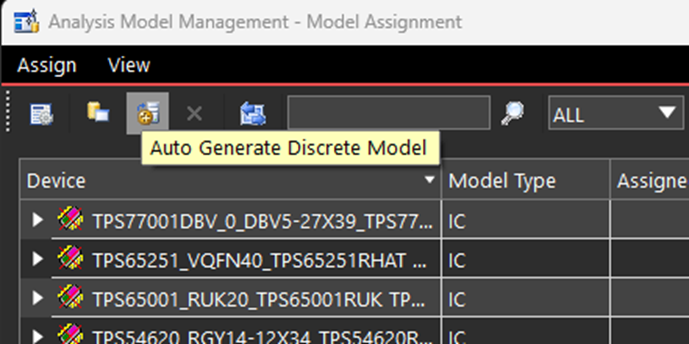

若是 Discrete分立器件,则可以点击下图(9)中的图标自动建立对应模型

图 9.自动建立 Discrete 被动组件对应模型

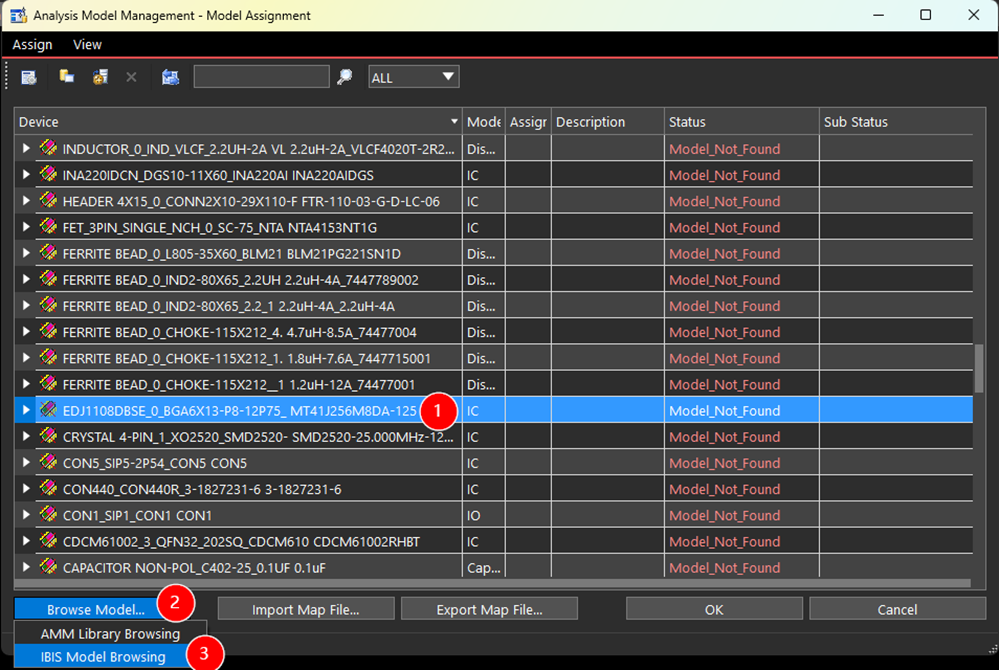

若要手动指定模型,如以下图(10) EDJ1108DBSE_0_BGA6X13-P8-12P75_MT41J256M8DA-125为例,先点选该零件,再点左下角的 Browse Model选择模型类型,再选择底下的 IBIS Model Browsing

图 10.手动指定模型步骤示意

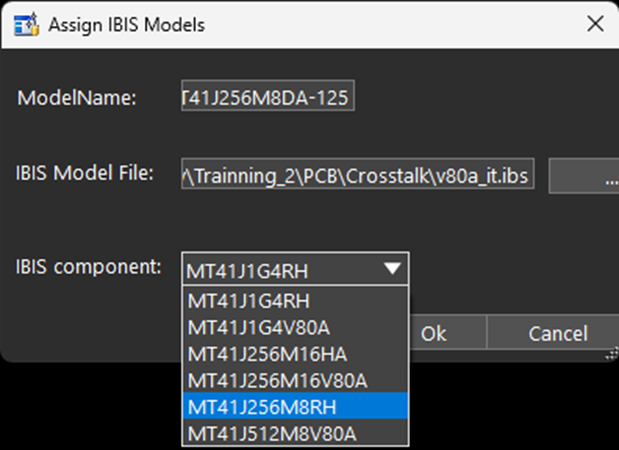

接着,请在 IBIS Model File 字段中选择与此零件所对应的 .IBS 模型文件,若.IBS 模型文件中有不同[Component]类型,可再于 IBIS Component 项目中进行选取零件,如 MT41J256M8RH (图 11)

图 11.指定 IBIS Models

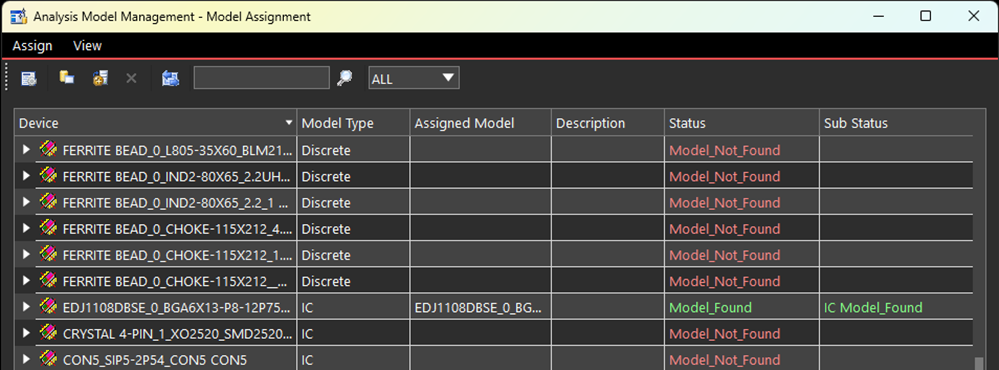

选取套用后,会显示如下方 Status 栏中的 Model_Found 表示: 此类零件 Model 套用完成。要是 IC的模型中有多种的模型描述才会显示在 Sub Status 字段里 (图 12)

图 12.Model_Found-零件 Model 套用完成示意

► Launch Analysis Model Manager 分析模型管理

若是仍习惯用 AMM(Analysis Model Manager)来管理 Models,请点选 Launch Analysis Model Manager。

如下图(13)中所示,可在此做 Project 的零件设置,还可以看到先前所设置的 Models 及各 PIN 数据,在此可重新设置或新增对应模型。

图 13. AMM-Project 零件设置

【温馨提醒】

- 先对 discrete 分立器件做 Auto Generate

- 对重要的 IC 零件设置其对应的 IBIS 模型文件

- 只对有关零件设置 Model

- 若有其他零件的就让它采用默认的 default models

PS. 此前三步骤,会将所建的模型存放在先前的 project library 项目零件库中。

完成 Model 模型设置之后,在开始执行分析之前,我们需要先选择要分析的 Net (图 14)。

图 14. 选择要分析的 Net

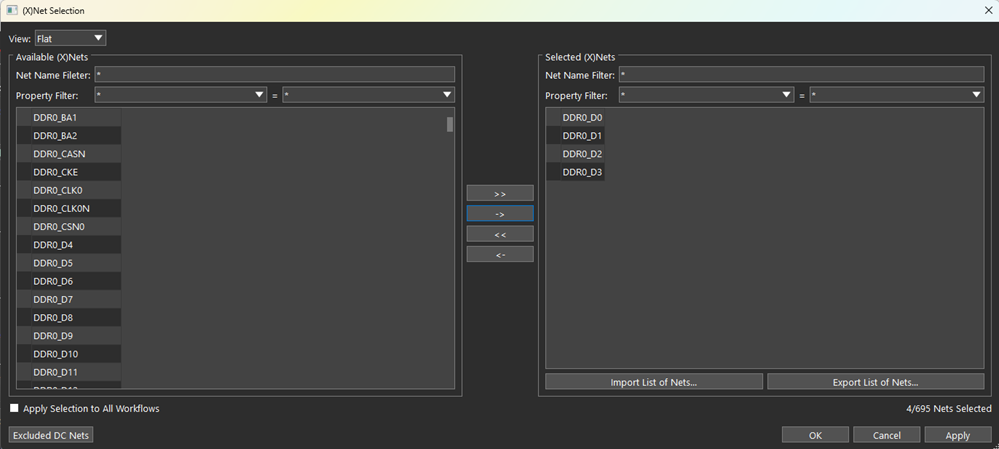

在(X)Net Selection 窗口中选择要执行分析的信号,默认为 Flat 模式,可显示所有信号名 (图15)。

图 15. 选择要分析的 Net

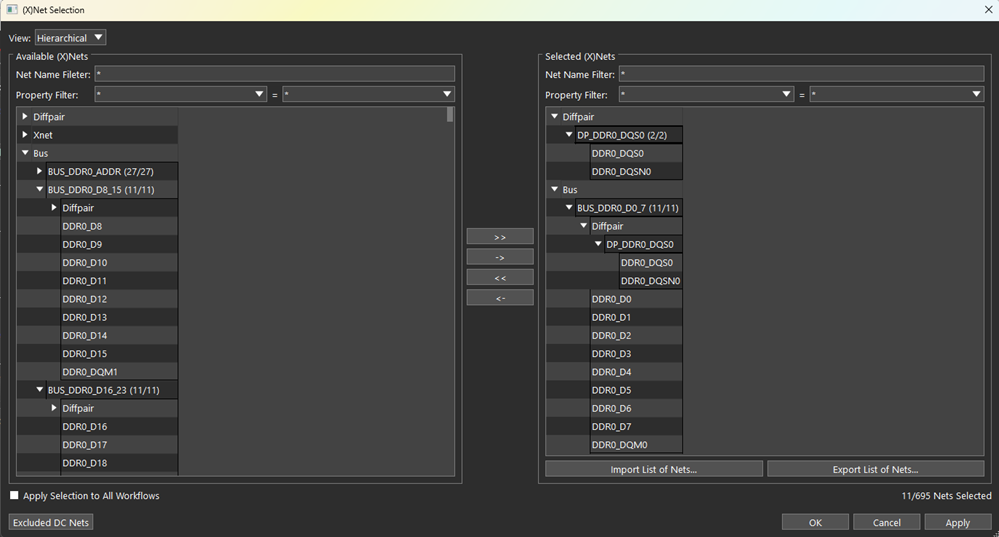

而左上角的 Views 检视模式可切换至阶层(Hierarchical)模式,只要有设置BUS/Net Group/Xnet/Diffpair,便可以阶层方式(Hierarchical)整组选取。同时也可搭配Shift按键进行区间选取,或Ctrl按键进行多个信号选取,当确认后点选中间的->键,将所选信号添加到右侧列表中。(图 16)

图 16. 阶层模式-选取要分析的 Net

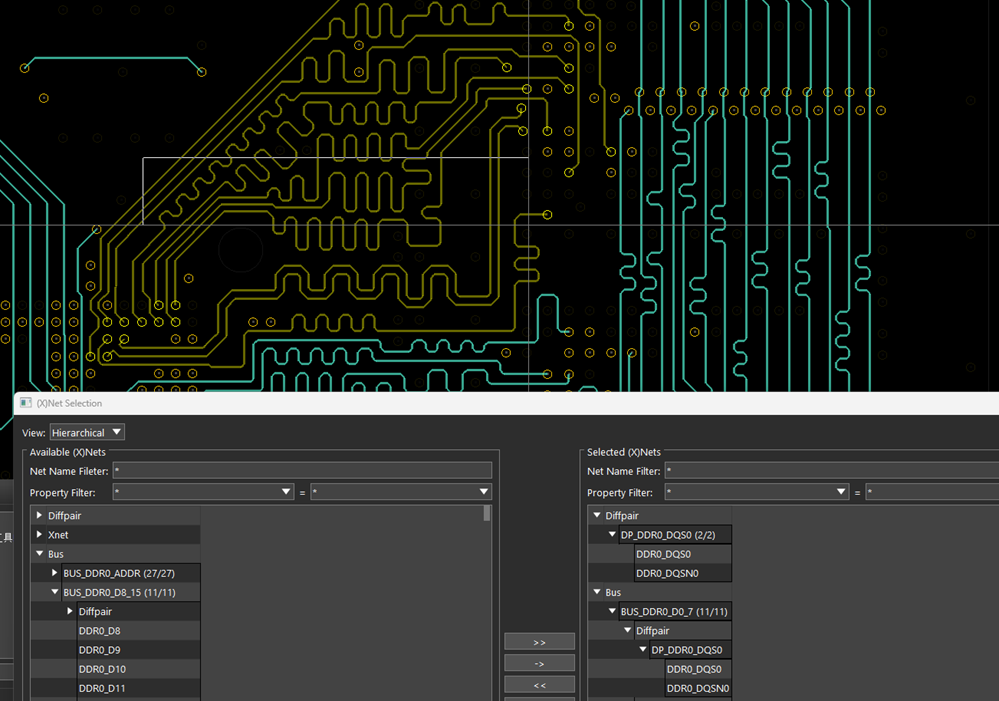

如同其他分析项目,在Allegro 17.4以上版本除了可在列表中选取要分析的 Net 之外,现在也可使用鼠标直接在 Layout 画面中框选要分析的 Net (图 17)。

图 17. 使用鼠标直接框选 Net

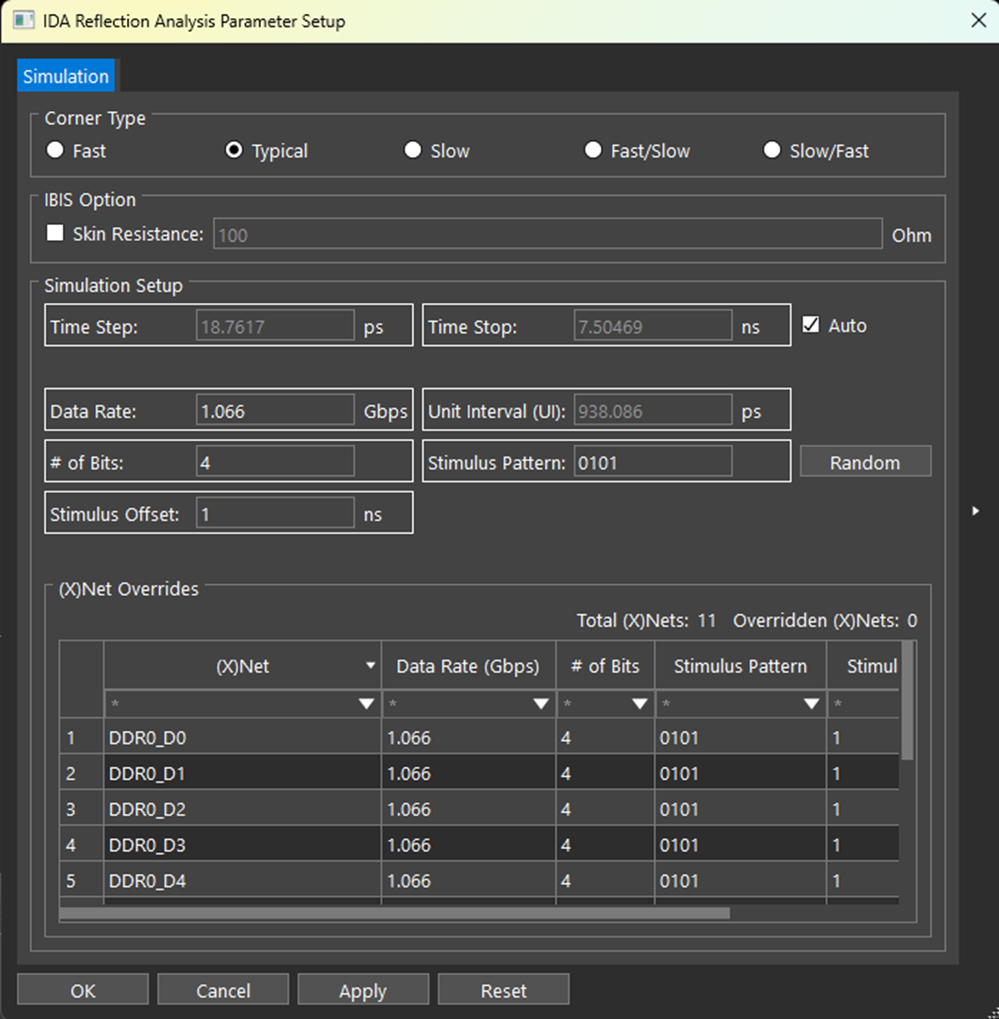

接着在 Workflow 中点选 Analysis Options 开启设置选项,Corner 一般为 Typical,Data Rate按照数据信号实际工作速率填写,例如:1.066Gbps,再将Stimulus Offset设置为1ns,取信号相对稳定时的波形,(图 18)。

图 18. 分析参数设置

设置完毕便可点选 Start Analysis ,开始进行分析(图19-1、图19-2)。

图 19-1. Start Analysis 开始进行分析

图 19-2. 分析计算中

一般来说针对高速信号我们会需要进一步做 Reflection 反射分析检查,以确保信号传输质量。

Reflection 分析结果解析

待分析完成便可选择要检视的结果。

这里我们直接来确认分析结果。下图中我们可以看到结果的呈现方式有两种选择,分别是

Reflection Table 以及 Reflection Vision (图 20)。

图 20. 结果检视模式示意

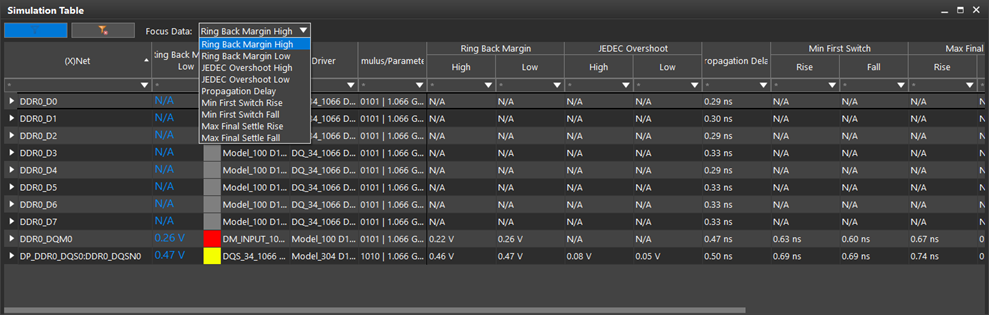

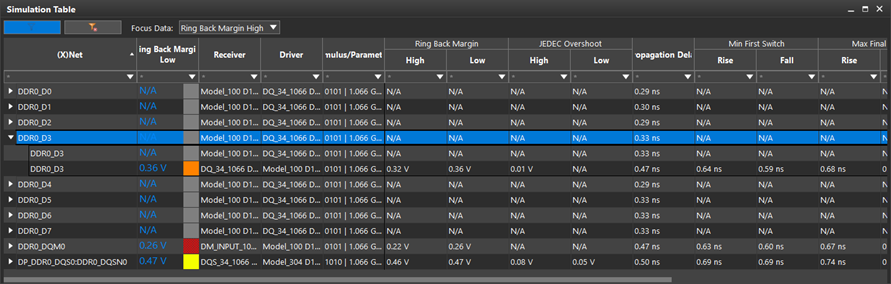

选择 Table 以表格方式呈现分析结果如下图,可检视的分析项目分别为:

- Ring Back Margin High (高电平时的回铃裕度)

- Ring Back Margin Low (低电平时的回铃裕度)

- JEDEC Overshoot High (JEDEC规范下,高电平时的过冲)

- JEDEC Overshoot Low (JEDEC规范下,低电平时的过冲)

- Propagation Delay (传播延迟)

- Min First Switch Rise (最小第一切换上升时间)

- Min First Switch Fall (最小第一切换下降时间)

- Max Final Settle Rise (最大稳定切换上升时间)

- Max Final Settle Fall (最大稳定切换下降时间)

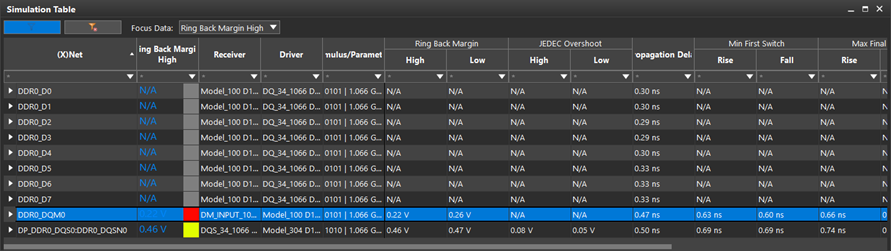

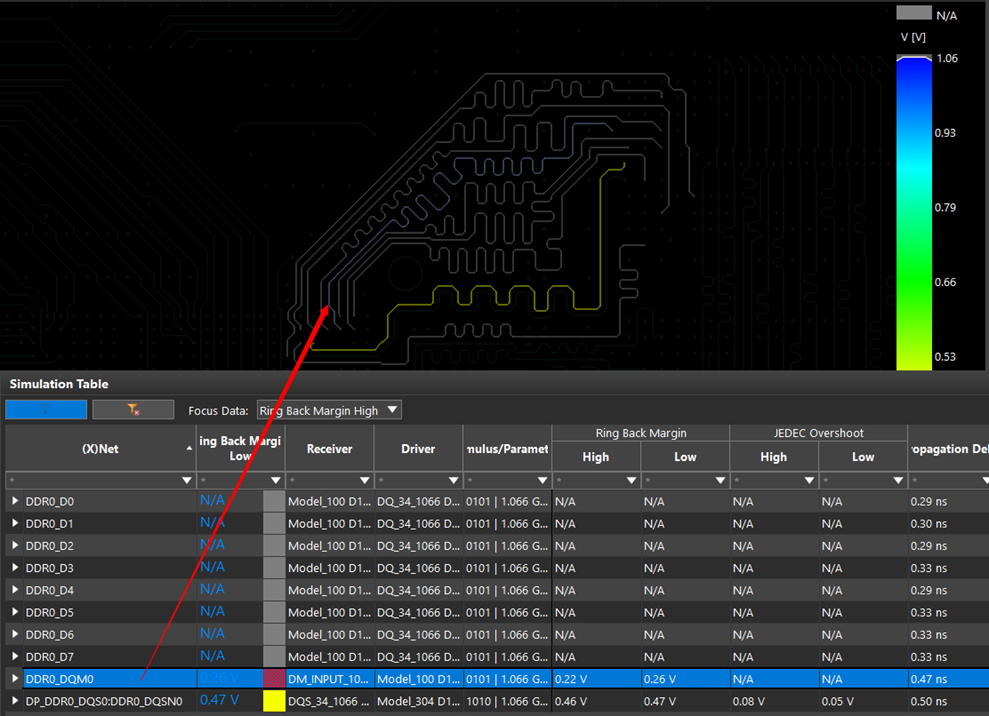

而 Table 左上方有 Focus Data 的下拉选项,点选后可将要检视的数据项数值显示于最左侧 (图21)。

图 21. 以 Table-Focus Data 下拉选单示意

我们可以针对有异常的项目进行确认,并且可使用光标点击异常项目来连动 Layout 画面,直接切换到有问题的位置 (图 22)。

图 22-1. 分析结果检视

使用鼠标点击异常(红色处)来连动 Layout 画面,直接切换到异常的位置做确认。

图 22-2. 分析结果检视

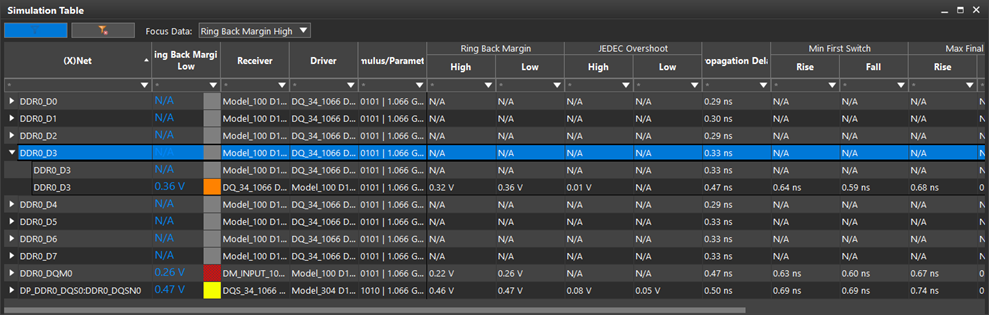

点击 > 可展开项目,显示不同区段的状态 (图 23)。

图 23. 项目展开

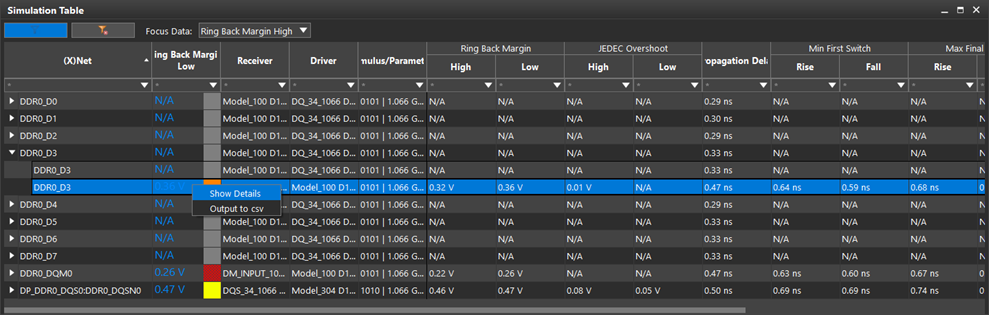

使用右键点选 Show Details 可查看信号详细状态,亦可将结果输出为 CSV 档案 (图 24)。

图 24. 显示详细信息图

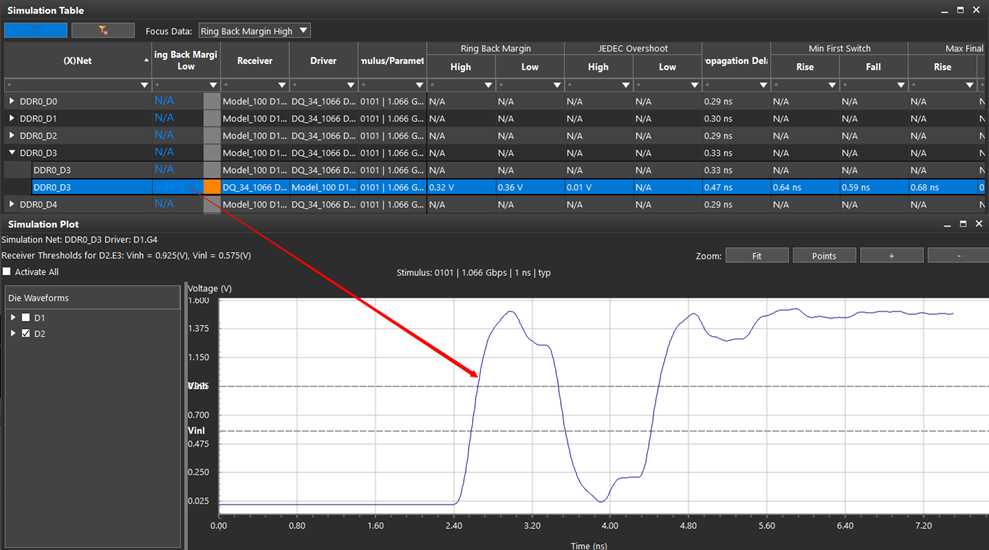

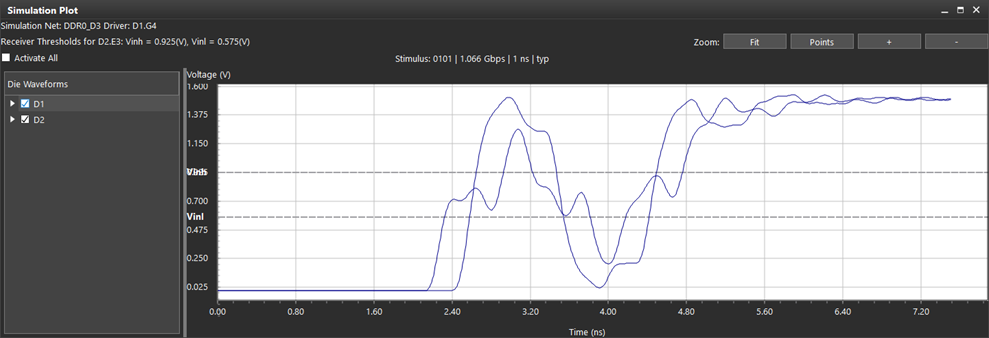

当我们使用鼠标点击 Focus Data 的数值时,可显示该信号的分析结果/波形画面 (图 25)。

图 25-1. 显示分析波形

可选择要检视的结果波形。

图 25-2. 显示分析波形

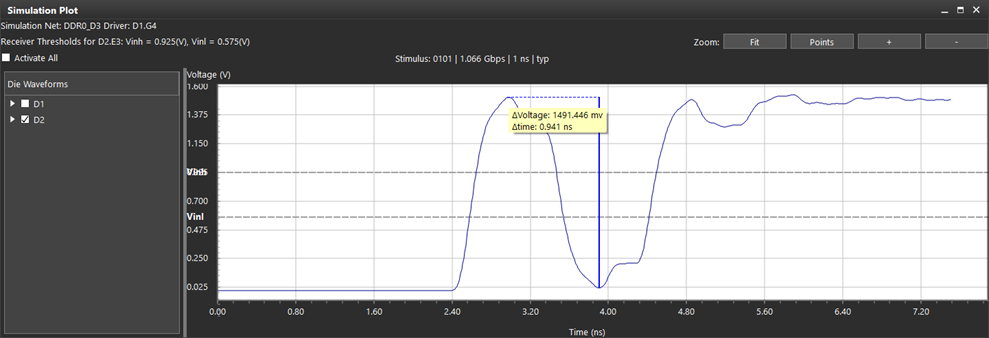

按住鼠标左键拖动可量测信号反射电压及时间。

图 25-3. 波形量测

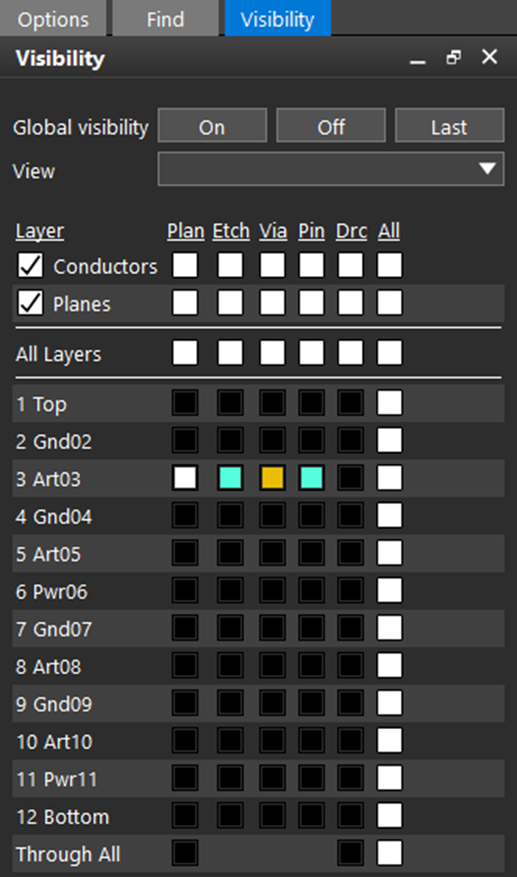

而对 Layout 人员来说最有直观感的便是以 Table 搭配 Vision 方式做检视,可直观的确认信号状态。我们可在 Visibility 面板选择要检视的层面,确认该层走线的分析结果 (图 26)。

图 26. Visibility 面板: 选择要检查的层面走线

选完层面便可以直接在Layout 中看到走线以色阶显示状态,画面的右边可以看到色阶分布显示,以颜色代表数值分布,并可自行调整要显示的范围,显示出目前 Layout 中所分析出来的状态。

如下图 27 为例,Focus Data 项目为 Ring Back Margin High,其中DDR0_D3信号以红色显示,其 Ring Back Margin High 电压值为 0.36V (图 27)。

图 27. 确认分析结果

这些分析信息除了帮助PCB Layout 人员检查确认外,还可以在需要时帮助 SI 人员进一步确认信号的状态。

总结

深入分析信号反射,快速优化 PCB 设计

如同前言所述,现今电子产品复杂度越来越高,信号速度越来越快,在信号传输的过程中,如果信号不断反射便会对电子产品的运作造成影响。以往 EE / PCB 设计工程师在处理信号反射问题时,可能需要花费许多时间与心思做检查,并且需要与 SI 人员反复沟通确认问题点,不断修正设计才能够得到正确的成果。如果有一个实时又直觉的帮手来帮助 EE / PCB 设计工程师做初步确认,就能够降低失败的机率,并且减少返工的时间。

现在Allegro中导入了Sigrity专业的仿真分析技术,将 IDA (In Design Analysis,设计同步分析)集成到PCB设计流程中,帮助EE/PCB设计工程师实时的分析Layout设计,并修正不理想的部分。而在执行Reflection分析功能时,只需再多搭配模型的设置,便能快速执行细部分析,分析结果涵盖零件特性,使工程师能够进一步检视信号反射,修正异常,使设计效率提升,不良机率减少,客户满意,大家开心。

【高速高密PCB高级验证技巧】系列专题主要解锁Impedance阻抗、Coupling耦合、Crosstalk串扰、Reflection反射、Return Path回流路径、 IR Drop压降等六种分析技巧,帮助 EE、Layout 人员在设计前期阶段不需依靠SI/PI专家就能做初步的模拟分析,快速找出并排除常见信号/电源问题,提升设计质量和效率。