实验2 指令调度和延迟分支【计算机系统结构】

- 前言

- 推荐

- 代理服务器拒绝访问解决

- 实验2 指令调度和延迟分支

- 1 实验目的

- 2 实验平台

- 3 实验内容和步骤

- (1)启动MIPSsim。

- (2)进一步理解流水段的构成和各个流水寄存器的功能。

- (3)选择“配置”下的“流水方式”,让模拟器工作于流水方式下。

- (4)采用指令调度技术解决流水线中的数据冲突。步骤如下:

- (5)采用延迟分支减少分支指令对性能的影响。步骤如下:

- 4 实验结论

- 5 实验心得

- 6 实验思考:

- 最后

前言

2023-5-19 16:29:55

以下内容源自《创作模板三》

仅供学习交流使用

推荐

实验1 流水线及流水线中的冲突【计算机系统结构】

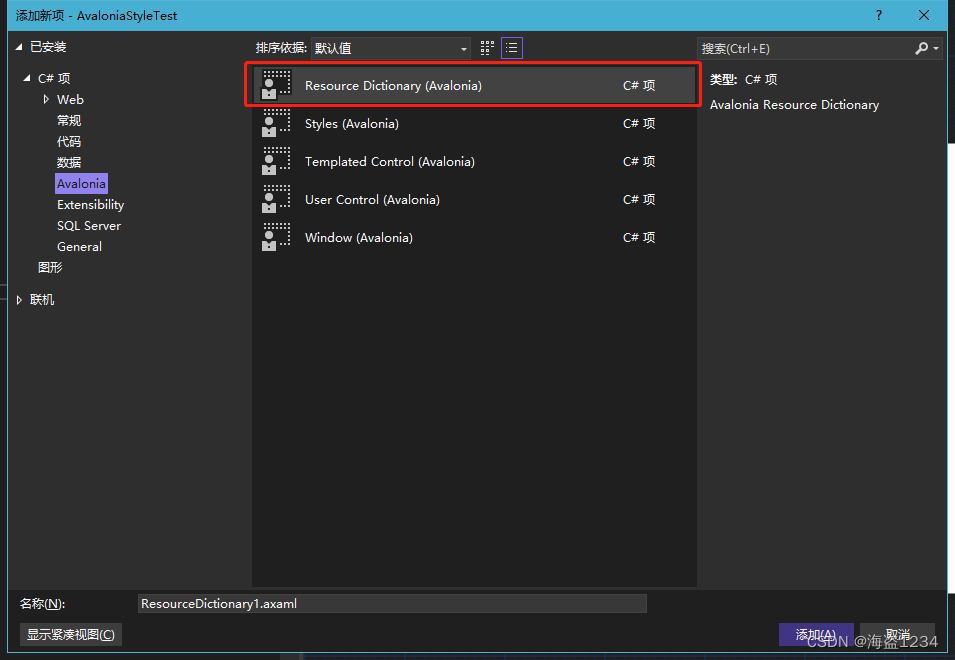

代理服务器拒绝访问解决

实验室机房

电脑上网

显示代理服务器拒绝访问

解决办法:

实验2 指令调度和延迟分支

1 实验目的

(1)加深对指令调度技术的理解。

(2)加深对延迟分支技术的理解。

(3)熟练掌握用指令调度技术解决指令流水线中的数据冲突的方法。

(4)进一步理解指令调度技术对CPU性能的改进。

(5)进一步理解延迟分支技术对CPU性能的改进。

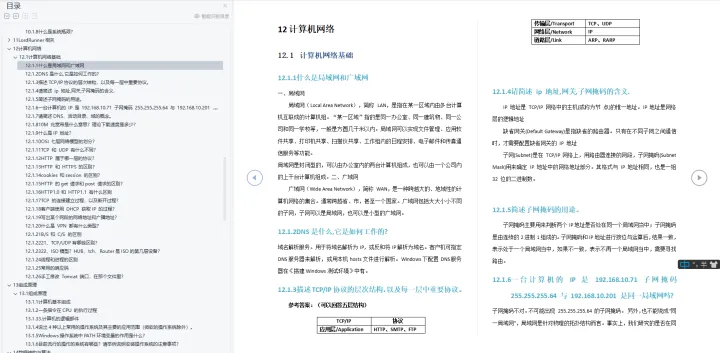

2 实验平台

指令级和流水线操作级模拟器MIPSsim。

3 实验内容和步骤

(1)启动MIPSsim。

(2)进一步理解流水段的构成和各个流水寄存器的功能。

(3)选择“配置”下的“流水方式”,让模拟器工作于流水方式下。

(4)采用指令调度技术解决流水线中的数据冲突。步骤如下:

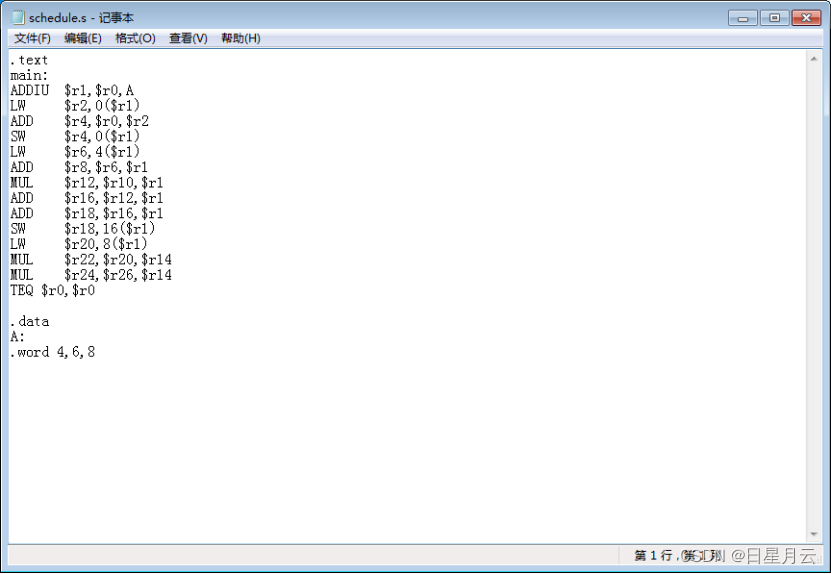

1)载入程序schedule.s。

2)关闭定向功能。

点击配置,取消勾选定向

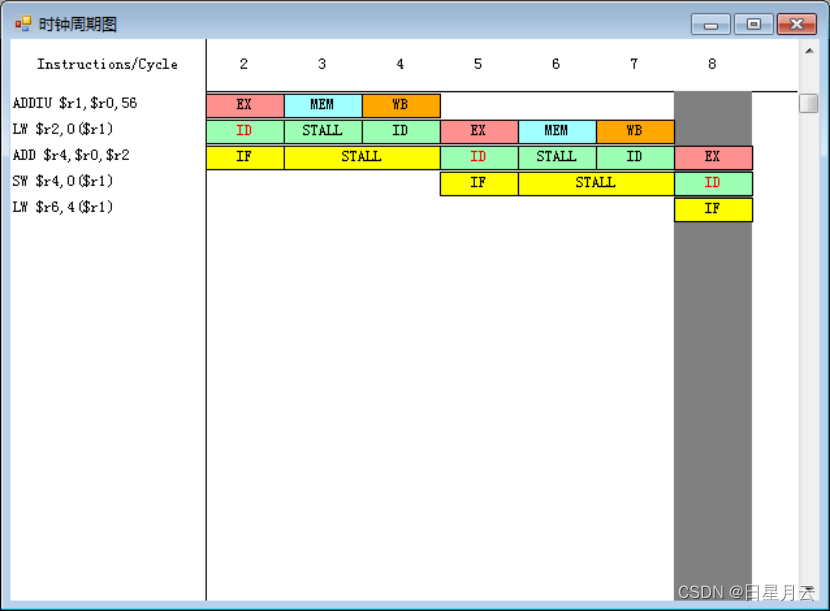

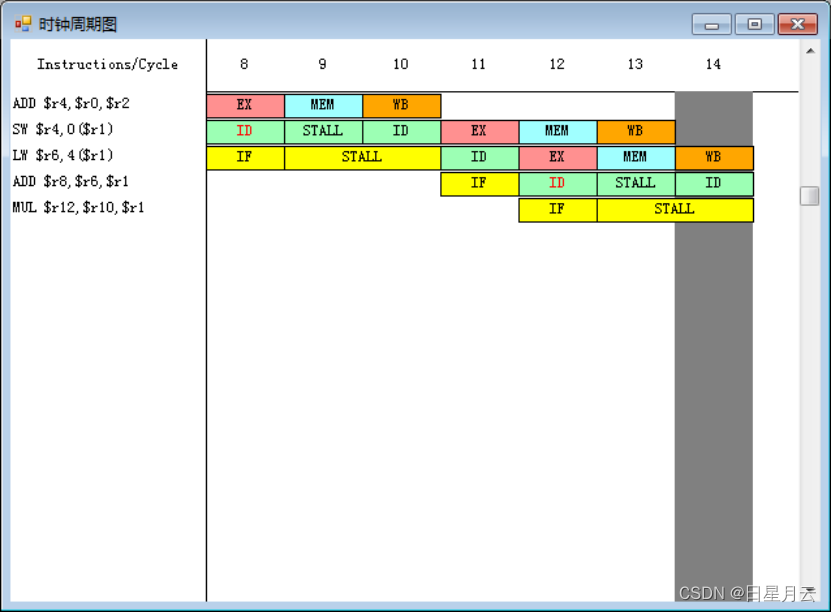

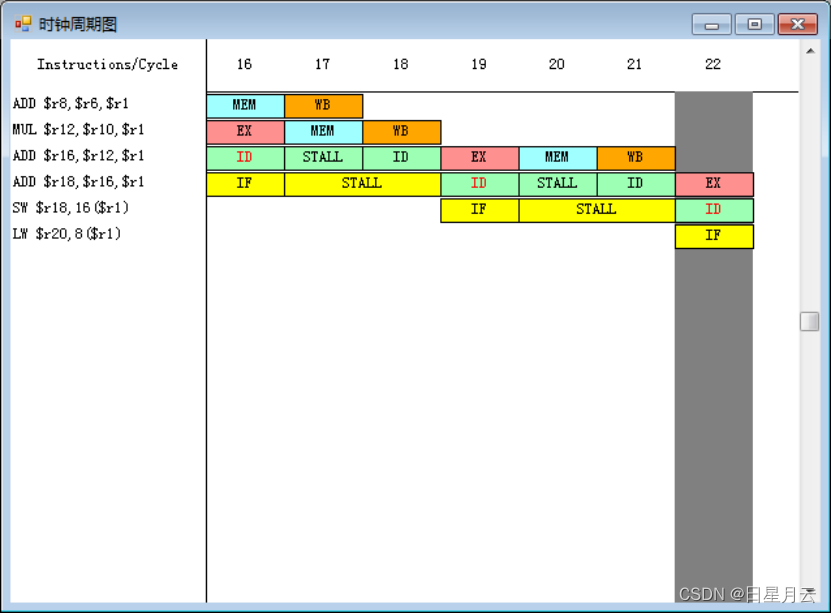

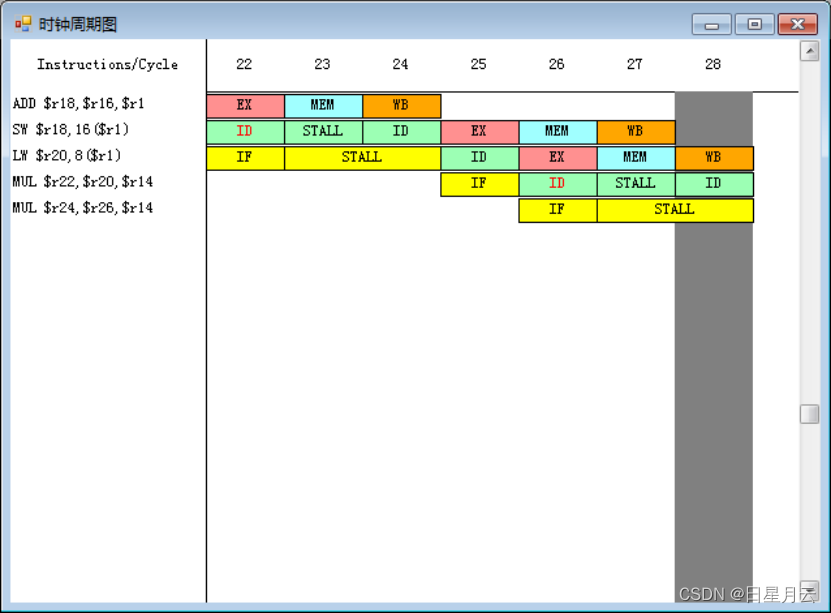

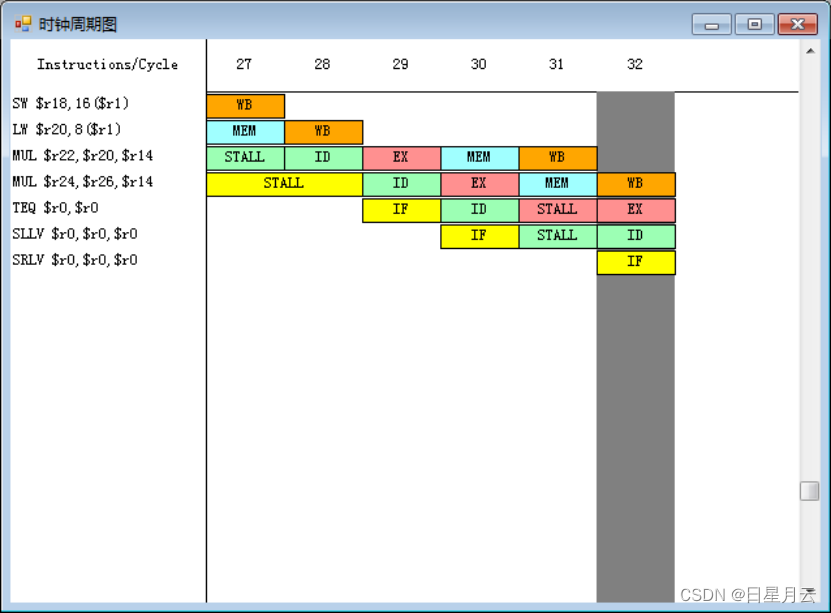

3)执行载入的程序。观察时钟周期图,找出程序执行中各种冲突发生的次数,发生冲突的指令组合以及程序执行的总时钟周期数。

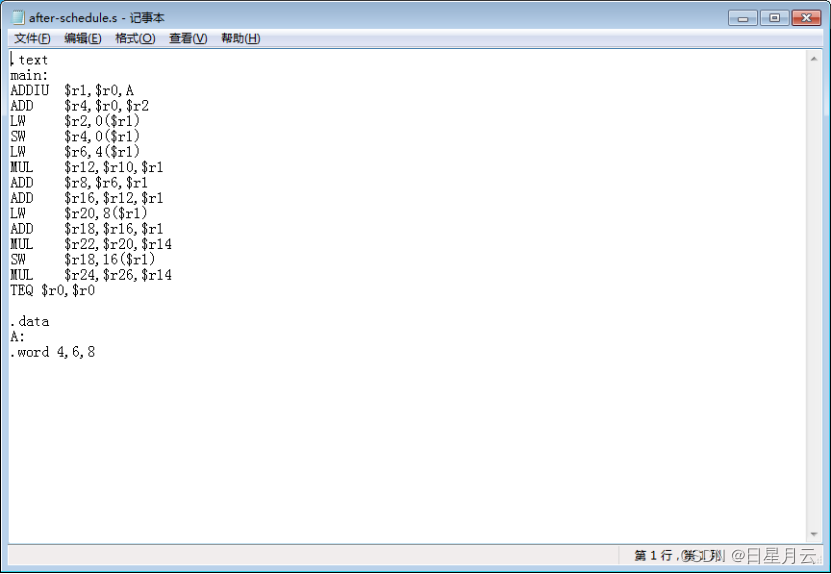

4)采用指令调度技术对程序进行指令调度,消除冲突,将源程序在下面列出。并将调度后的指令存到after-schedule.s中。

源程序

冲突都是RAW冲突

修改后的程序

所以指令调度把读后写分开几个周期即可

5)载入after-schedule.s。

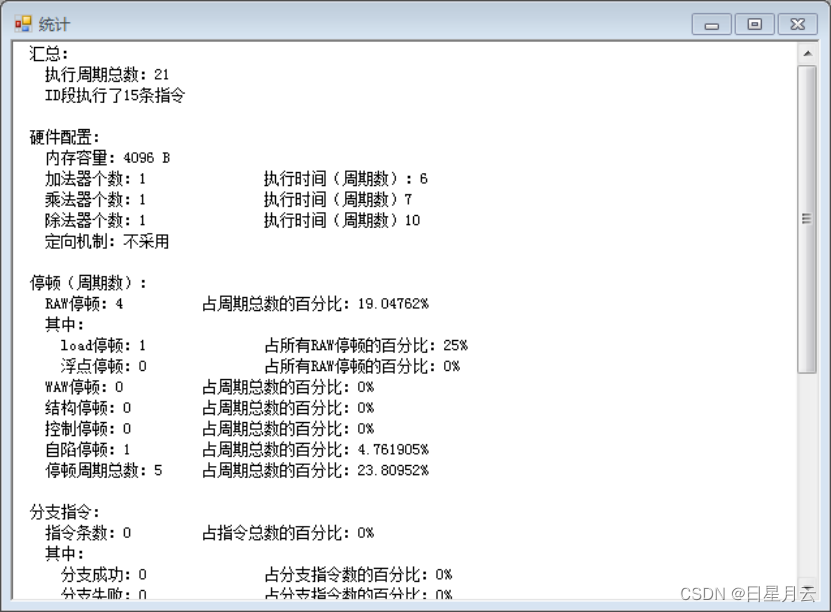

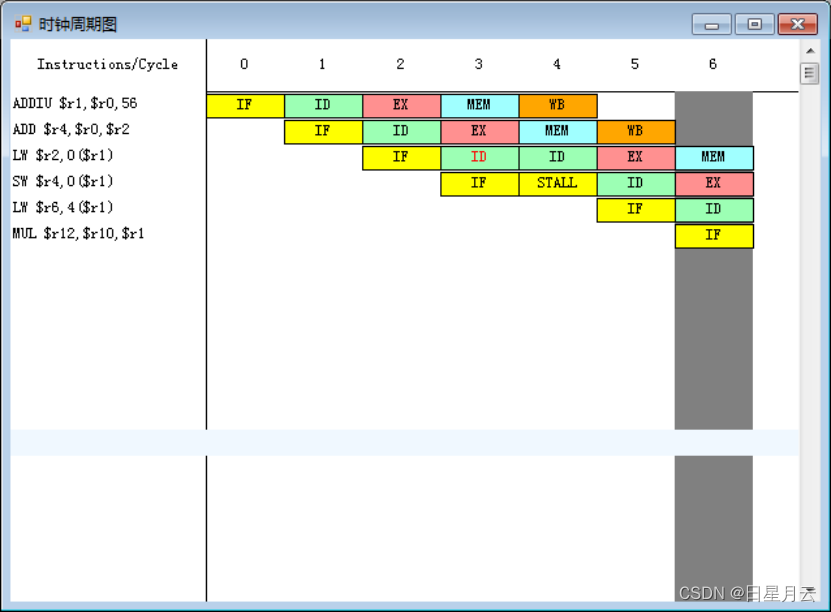

6)执行程序,观察程序在流水线中的执行情况,记录程序执行的总时钟周期数。

7)根据记录结果,比较调度前和调度后的性能。论述指令调度对提高CPU性能的作用。

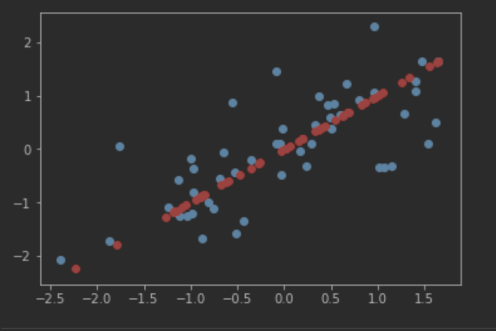

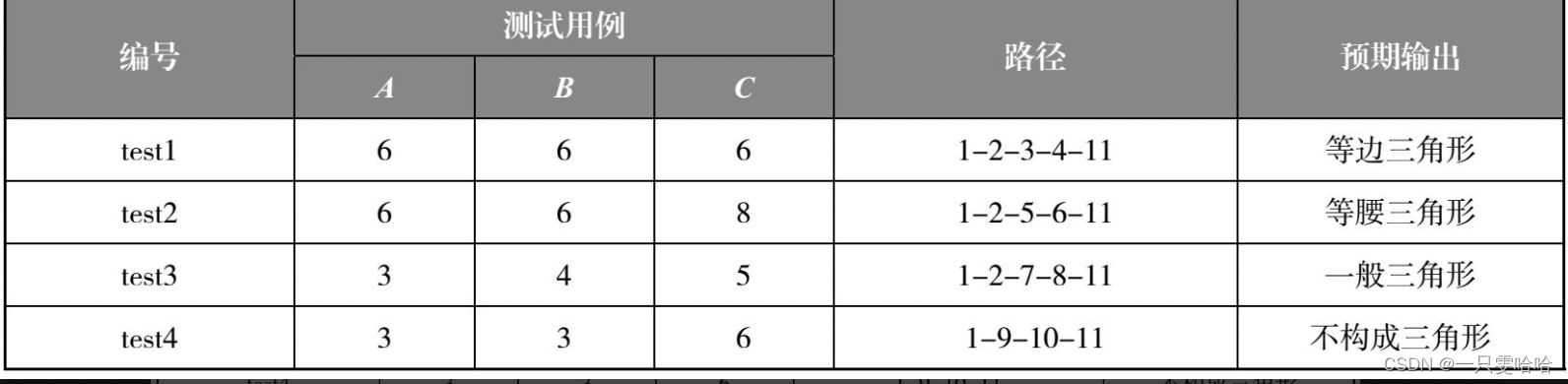

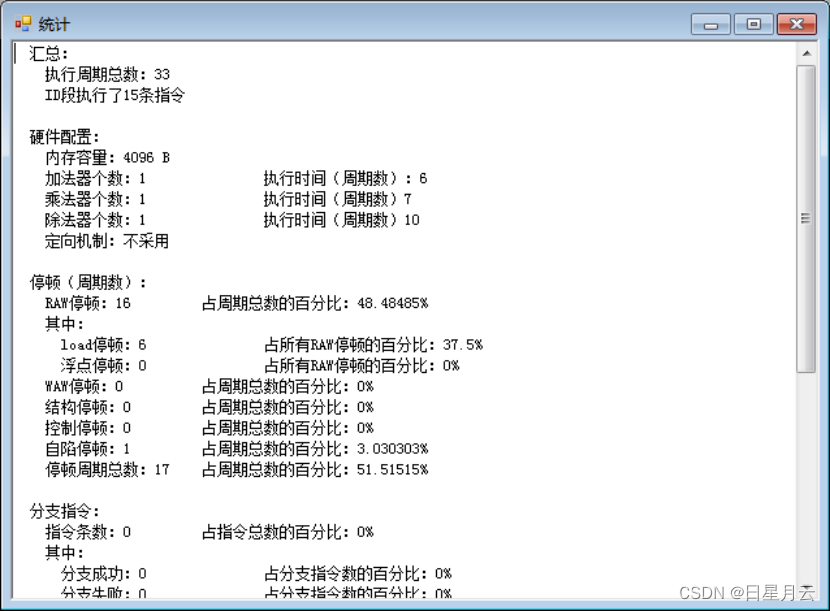

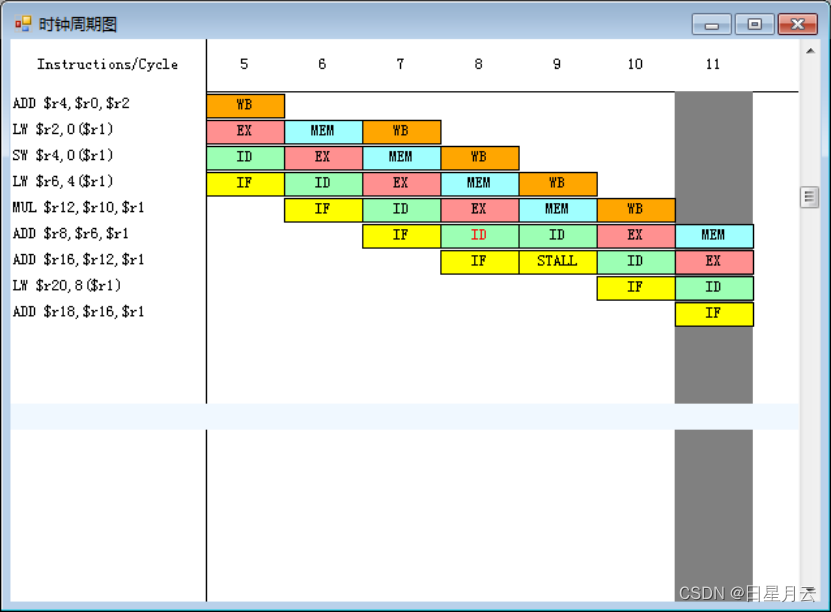

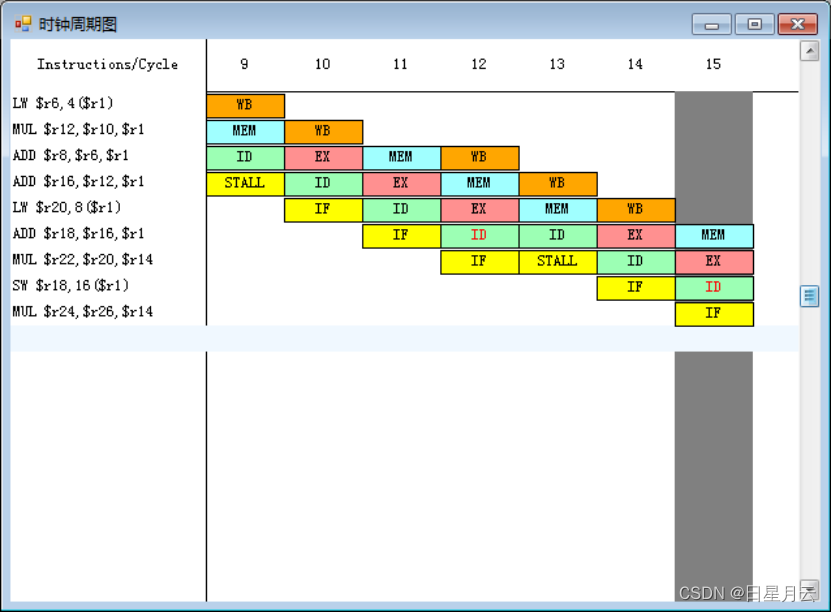

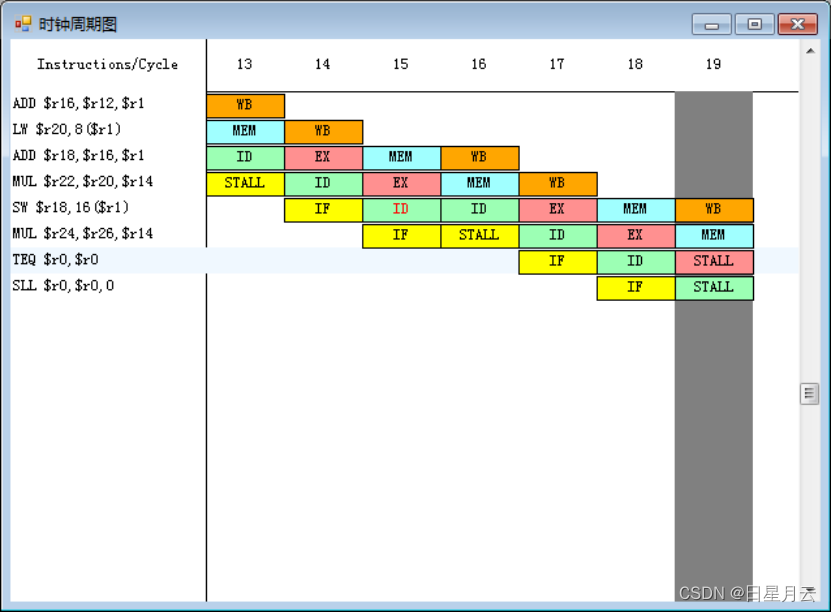

调度前

调度后

可以发现

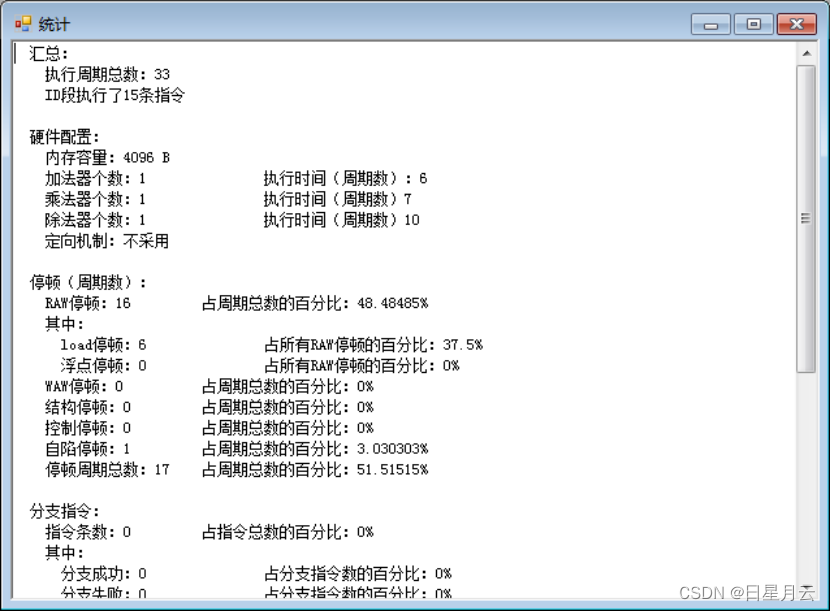

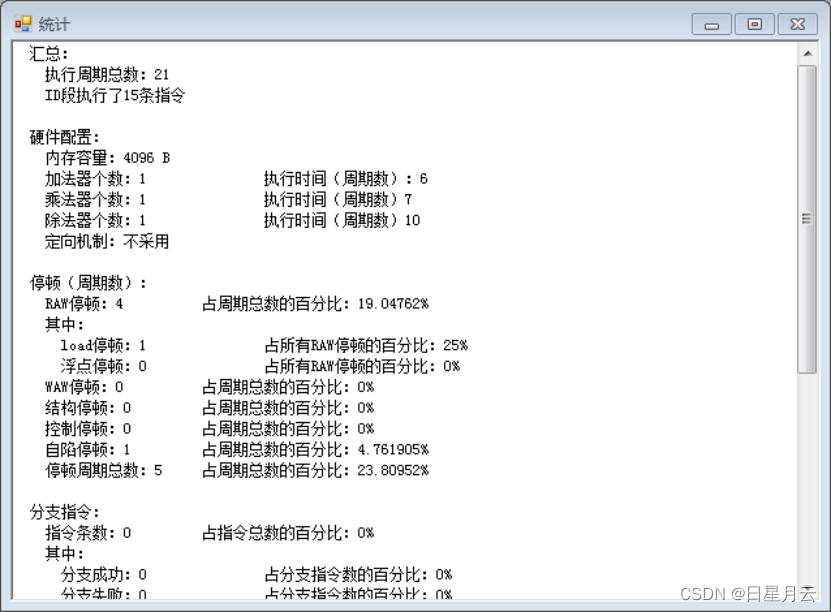

调度前:执行周期总数:33;ID段执行15条指令;RAW停顿:16

调度后:执行周期总数:21;ID段执行15条指令;RAW停顿:4

可以看出,指令调度对于CPU执行效率的明显提高。

(5)采用延迟分支减少分支指令对性能的影响。步骤如下:

1)启动MIPSsim。

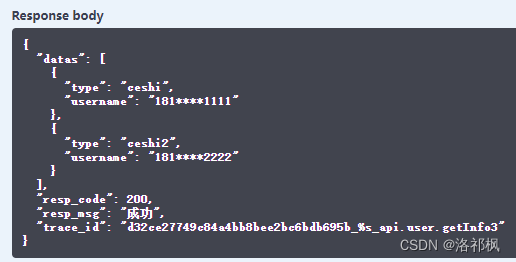

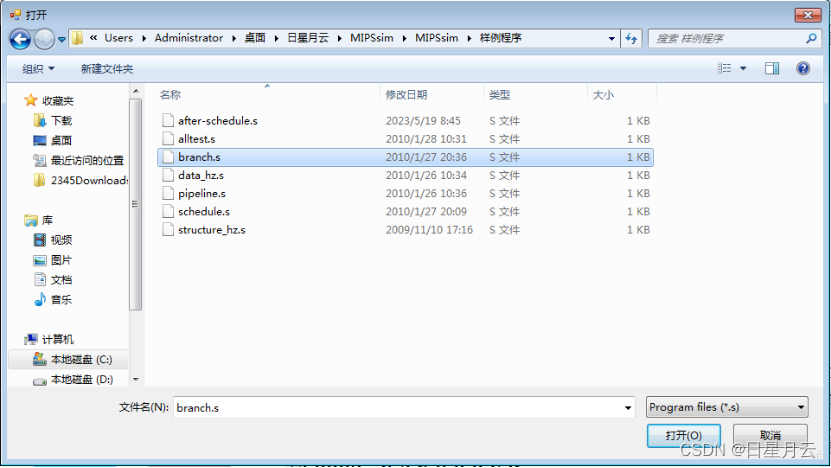

2)载入branch.s。

3)关闭延迟分支功能。通过“配置”下取消“延迟槽”选项。

4)执行该程序,观察并记录发生分支延迟的时刻。

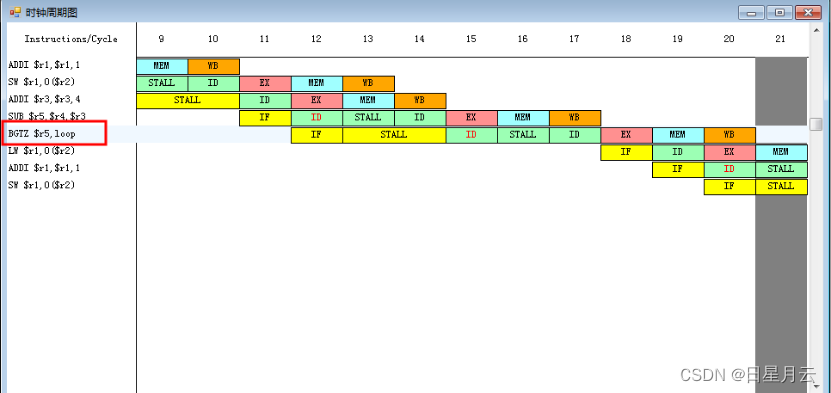

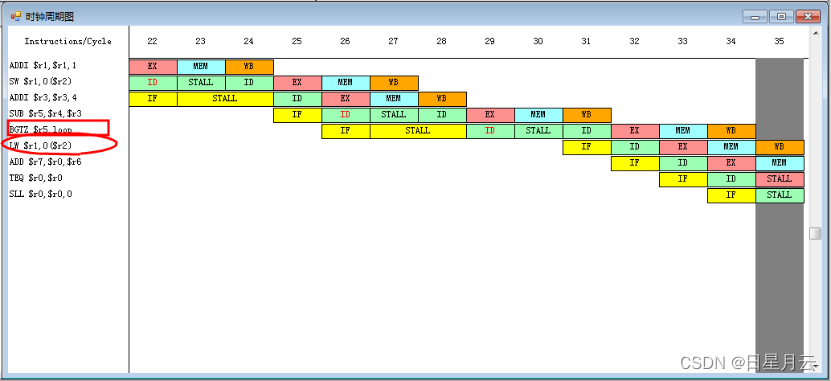

第一次分支:到loop

第二次分支:到npc

5)记录该程序执行的总时钟周期数。

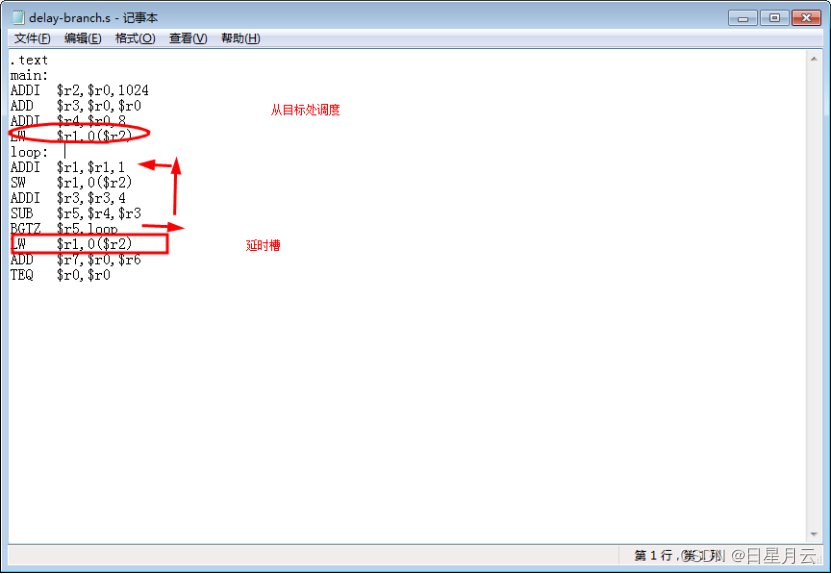

6)假设延迟槽为一个,对程序进行指令调度,然后保存到delay-branch.s中。

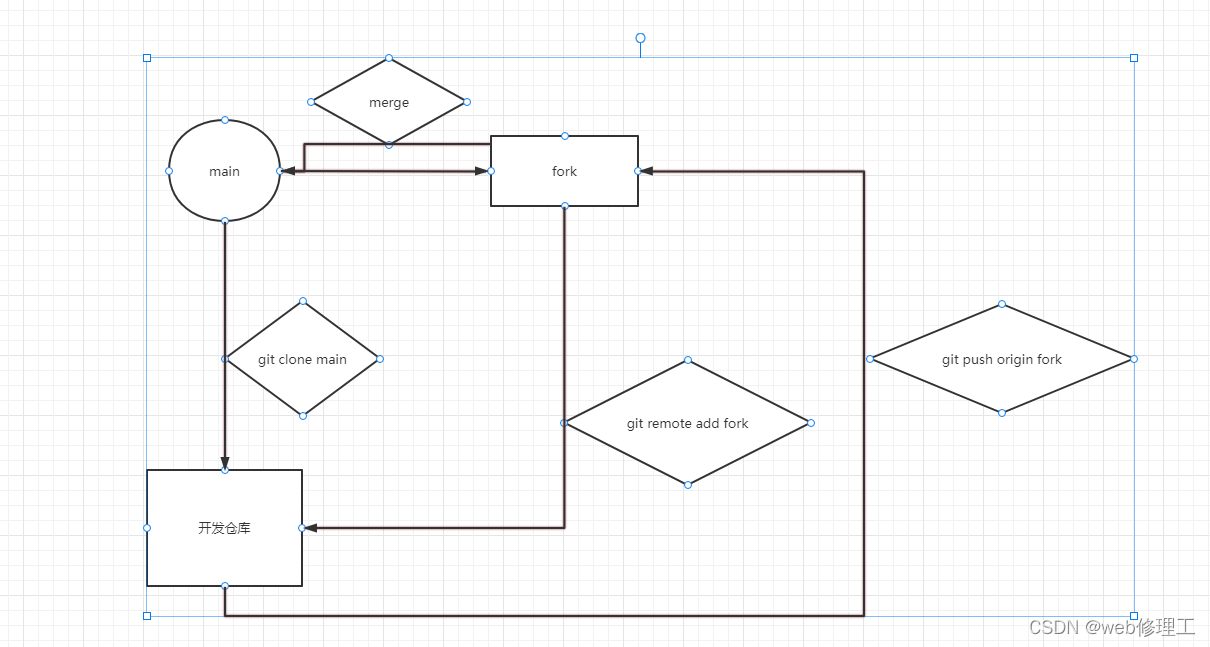

下面只针对分支指令进行指令调度

采用从目标处调度

7)载入delay-branch.s。

8)打开延迟分支功能。

点击配置,勾选延时槽

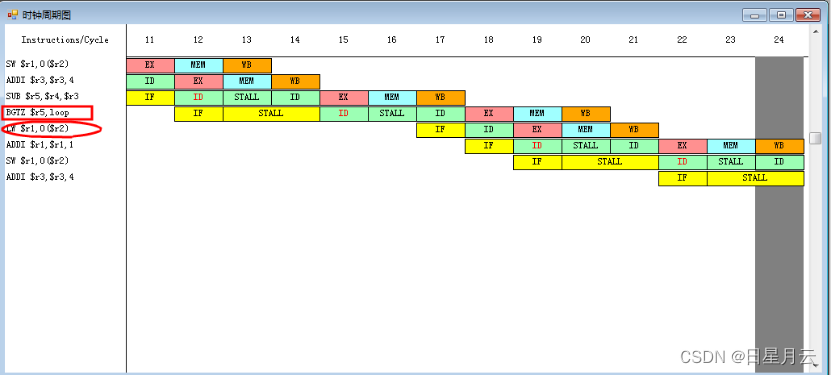

9)执行该程序,观察时钟周期图。

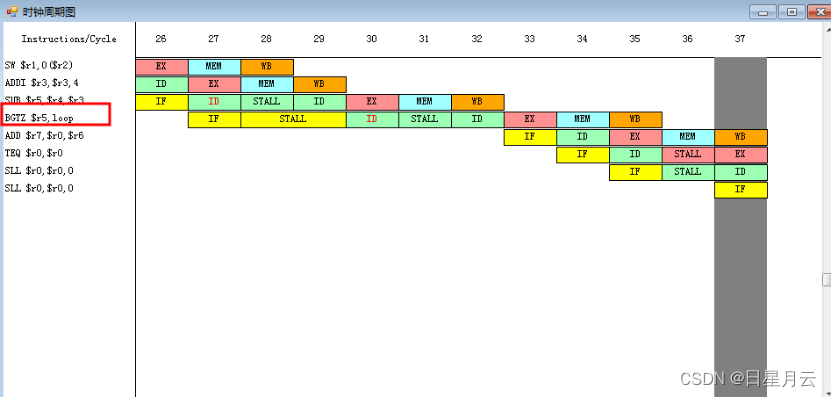

第一次分支,到loop,(延时槽)

第二次分支,到npc,(延时槽)

10)记录执行该程序的总的时钟周期数。

11)对比上述两种情况下的时钟周期图。

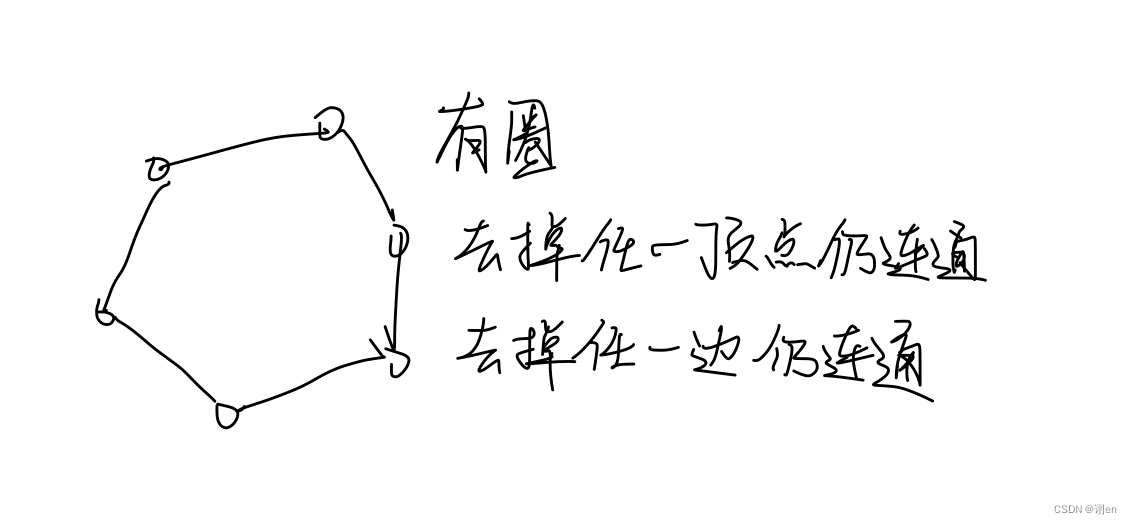

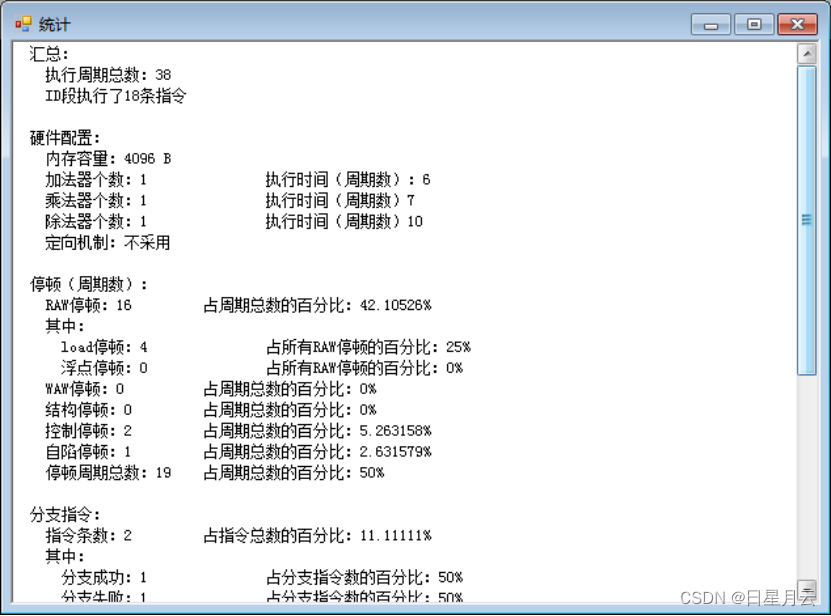

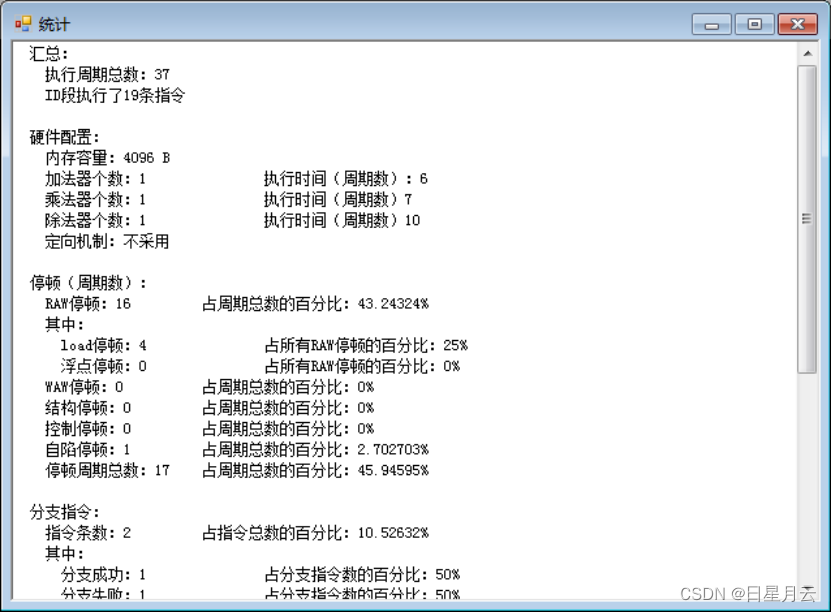

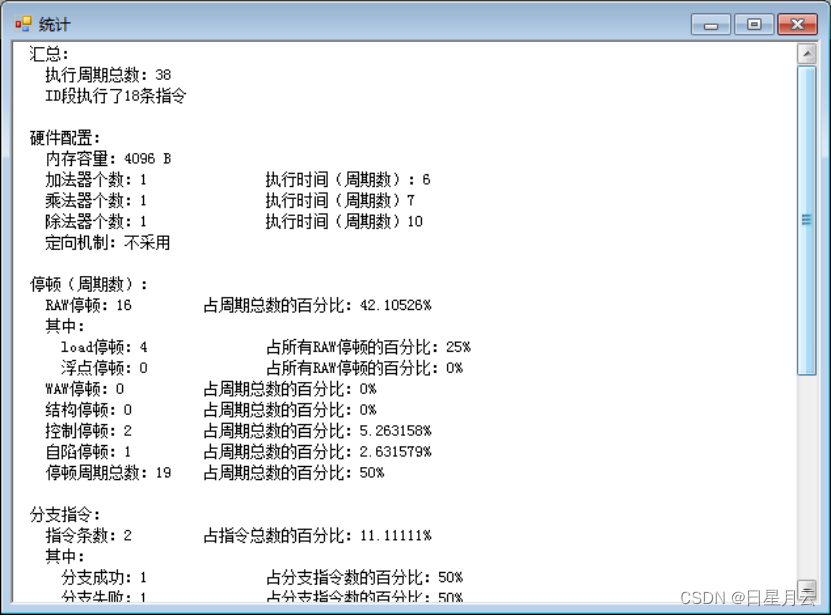

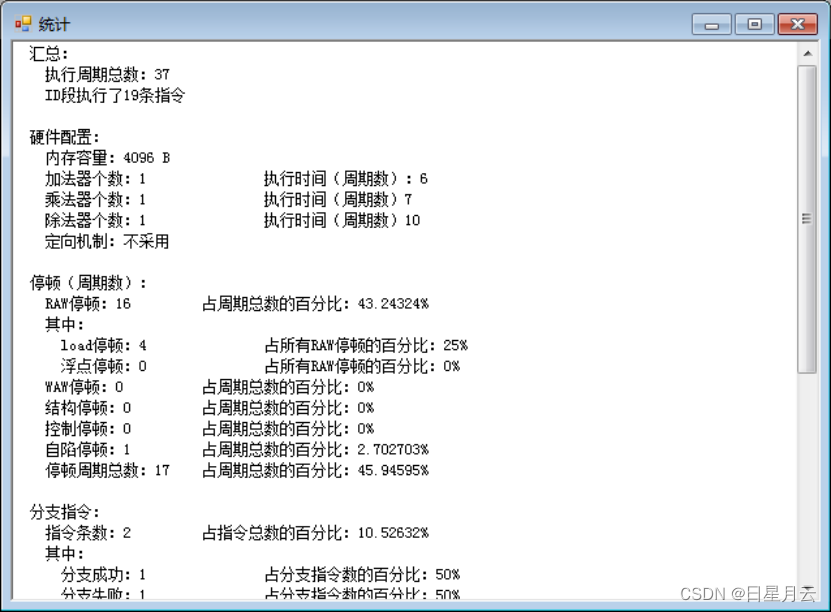

没有采用延迟分支之前

采用了延迟分支之后

可以发现:

没有采用延迟分支之前:执行周期总数:38;ID段执行了18条指令;分支指令占比11%

采用了延迟分支之后:执行周期总数:37;ID段执行了19条指令;分支指令占比10%

12)根据记录,比较没有采用延迟分支和采用了延迟分支的性能之间的不同。论述延迟分支对CPU性能的作用。

延时分支:可以使CPU在分支的时候,只要分支延迟槽中的指令是有用的,流水线就没有出现停顿,这时延迟分支的方法能很好地消除分支延迟。

4 实验结论

指令调度:可以减少数据冲突造成的停顿

延时分支:可以使CPU在分支的时候,只要分支延迟槽中的指令是有用的,流水线就没有出现停顿,这时延迟分支的方法能很好地消除分支延迟。

5 实验心得

通过本次实验:

(1)加深了对指令调度技术的理解。

(2)加深了对延迟分支技术的理解。

(3)熟练掌握了用指令调度技术解决指令流水线中的数据冲突的方法。

(4)进一步理解了指令调度技术对CPU性能的改进。

(5)进一步理解了延迟分支技术对CPU性能的改进。

6 实验思考:

以下是一段MIPS指令序列,

I 1 loop: add $t1, $s3, $s3

I 2 add $t1, $t1, $t1

I 3 add $t1, $t1, $s6

I 4 lw $t0, 0($t1)

I 5 bne $t0, $s5, exit

I 6 add $s3, $s3, $s4

I 7 j loop

I 8 exit

假如在实验的五段流水线中执行上述指令序列,在数据通路中,寄存器写口和寄存器读口分别安排一个时钟周期的前、后半个周期内独立工作,请思考:

(1)哪些指令之间发生数据相关?哪些指令之间发生控制相关?

数据相关:

I1和I2和I3、I4和I5

控制相关:

I5和I6和I8

(2)如果不采用“直通”技术进行数据冲突处理,那么应该在何处、加入几条nop指令才能避免数据冲突?假定采用“直通”技术处理,是否可以完全解决数据冲突?不行的话,需要在发生数据冲突的指令前加入几条nop指令,才能使这段指令序列的执行避免数据冲突?

(3)对于第5条分支指令引起的控制冲突,假定将检测结果是否为“零”并更新PC的操作放在“访存(Mem)”执行,则分支延迟损失时间片为多少?在何处、加入几条nop指令可以消除控制冲突?若检测结果是否为“零”并更新PC的操作在“执行(EX)”执行,则分支延迟损失时间片为多少?

(4)对于第7条指令“j loop”,假定更新PC的操作在“执行(EX)”阶段执行,则流水线会被阻塞几个时钟周期?需要在何处、加入几条nop指令可以消除该控制冲突?假定更新PC的操作在“译码(ID)”阶段执行,则流水线又将被阻塞几个时钟周期?

最后

2023-5-19 18:39:27

你对我百般注视,

并不能构成万分之一的我,

却是一览无余的你。

祝大家逢考必过

点赞收藏关注哦