全部学习汇总: GreyZhang/g_TC275: happy hacking for TC275! (github.com)

章节的标题不是我写的标题,但是从功能分类看的话基本是,暂且如此总结。

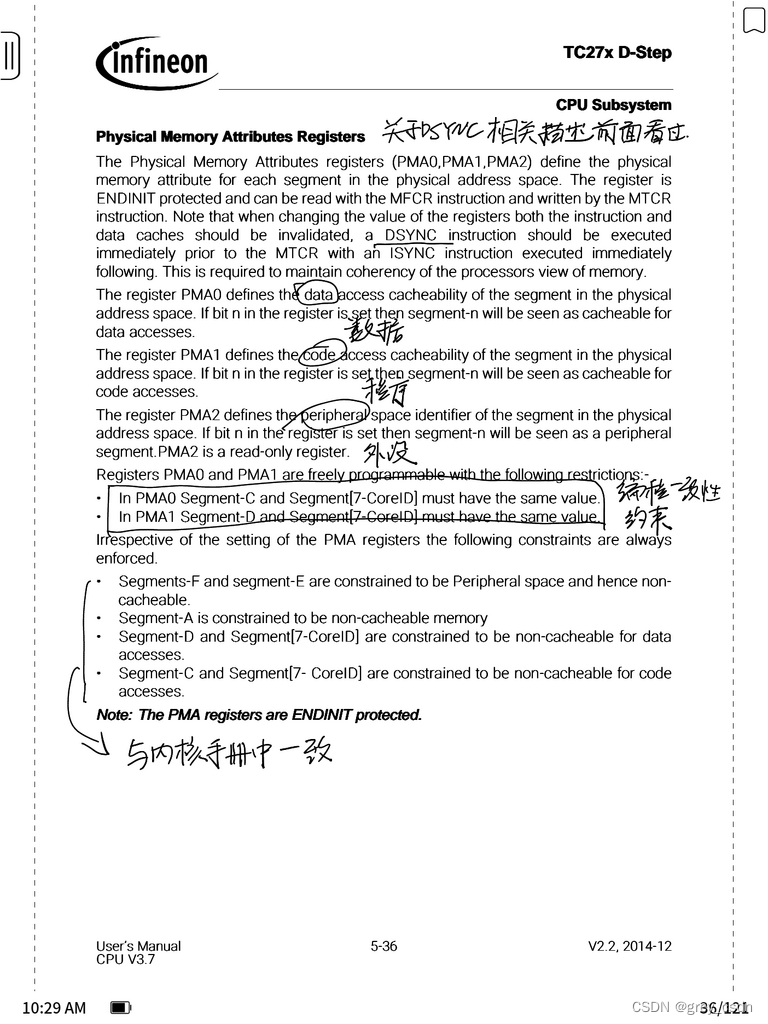

1. DSYNC的命令之前看过,因为cache是具有不可见性的,通过这个命令可以让数据刷新到存储中去。

2. PMAx,三个寄存器分别是对数据、程序、外设进行属性的约数。这几个寄存器在处理带有CaChe的段的时候是有一定的编程约束的,实施的时候需要注意。

3. 关于段的对应关系,这部分内容跟内核手册的信息是一致的。

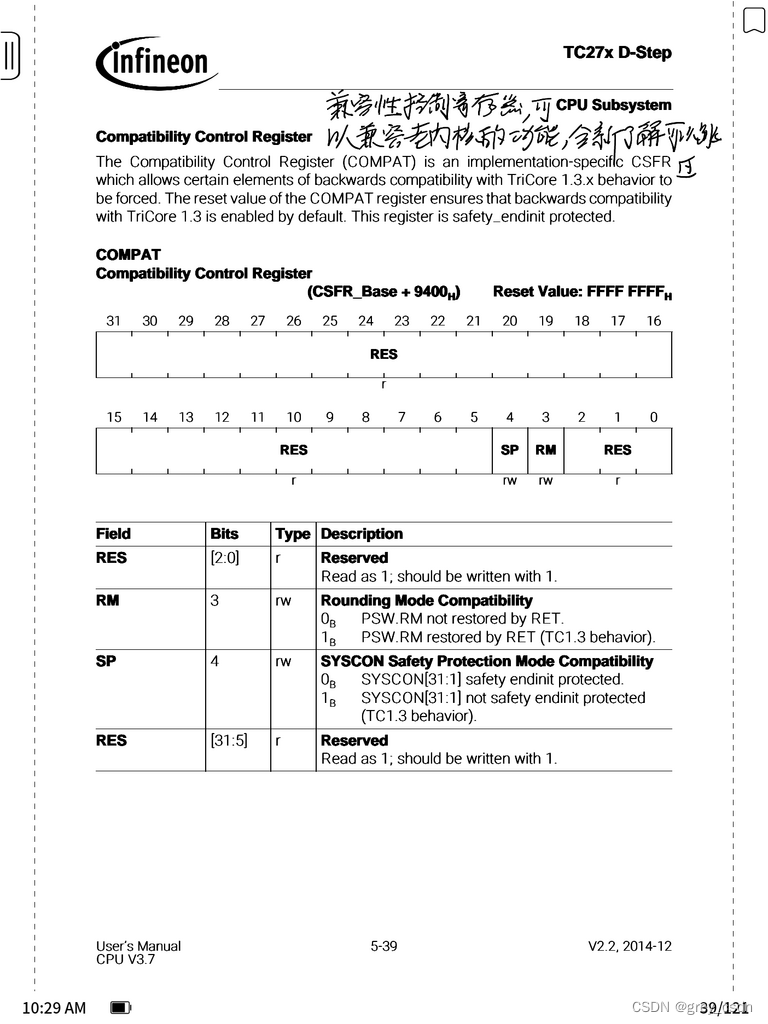

TC275中有一个兼容性寄存器,可以让内核兼容老内核的行为。如果没有老内核的应用历史,这个应该是用不到了。

1. 存储保护不知道是否跟MPU是相同的功能,不同于以前的内核设计,TC275支持的是全地址范围空间内的保护。

2. 保护机制的设置,可以指定CPU获取指令的地址空间。

3. 存储保护的实现就是遵照内核架构的要求设计的,没有什么特殊的部分。

4. 临时保护系统,从内容描述看也是跟内核架构中的描述是一样的。从功能上感觉,有种看门狗的感觉。

1. 存储完整性的检测,有一组寄存器可以支持最后一次的故障的地址检查。

2. 指令从程序存储中获取信息失败的时候,可能不会触发trap。

3. 前面看内核手册的时候好奇这个存储的完整性是否就是ECC的功能,根据前面的几条还是没有一个明确的分析结论,大概率还是ECC检测吧。最后这一条单独把ECC拿出来说了,但是也并不是说ECC只是其中的一条,因为这里讲得是总线的ECC。

1. E核是没有D Cache的,但是可能报出相关的错误。

2. 内部以及外部的存储加载会出现两种不同的错误,这个原因没有弄明白为什么要分开。大概率是因为总显得不同?

3. 安全保护机制发生的时候,有相应的指示信息会记录在寄存器中。

4. 这里的ECC又是单独的一条,但是还是总线相关的。

1. CPU的本地存储是通过ECC进行了保护的,这种机制需要增加存储本身的bit位,这个在之前了解ECC机制的时候其实是看到过的。

2. 数据阵列的方式进行访问,只能够以带有ECC检测功能的模式来进行。

3. 最后这一部分没有看懂,MTU看上去是一个优点复杂或者相应的技术描述超出我个人掌握的词汇范围的一个模块。如果后面有这个模块专门描述的时候,再去做针对性的深入分析。

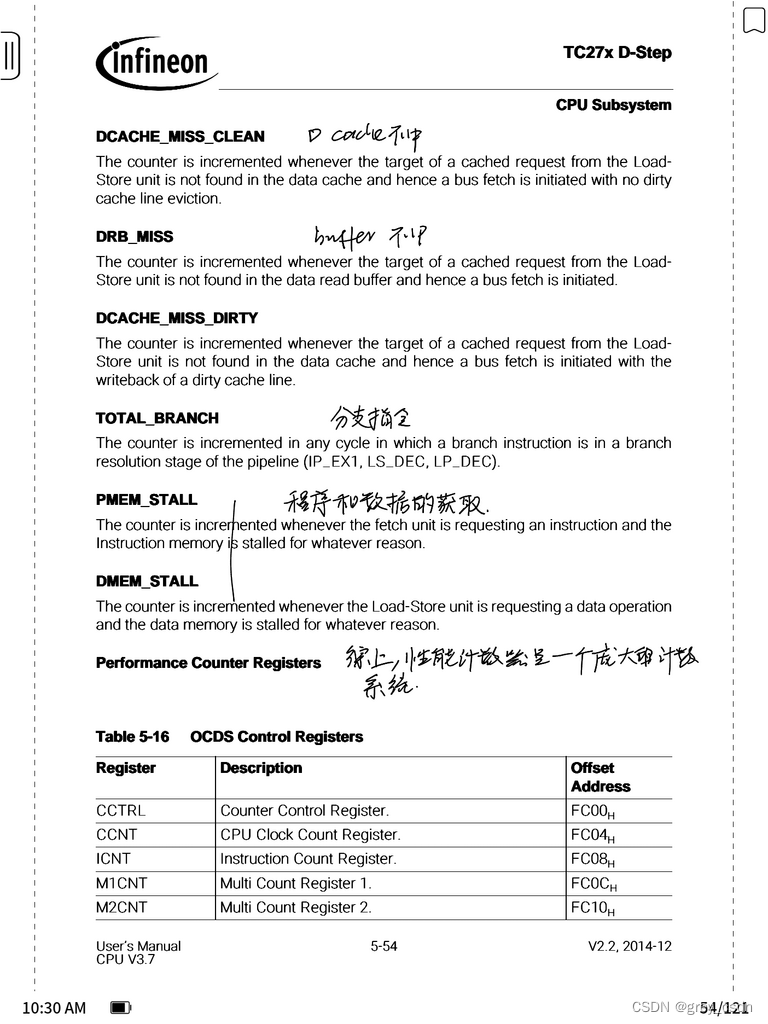

以前看内核手册的时候以为性能计数器只是一个累加的计数器,现在看来不是。性能计数器其实是根据不同的场景或者结果进行分类统计的一个计数器,由此倒是可以看到一些更有针对性的运行效果。看起来,这个性能计数器其实是一个比较庞大的计数器系统。