2023上半年软考中级软件设计师知识点速记分享给大家,快来一起打卡学习吧!

1、码制的表示

2、浮点数的表示

(1)浮点数格式

阶码决定范围,阶码越长,范围越大;

尾数决定精度,尾数越长,精度越高。

(2)浮点数运算过程

对阶→尾数计算→格式化;

对阶:小数像大数看齐,尾数右移。

3、校验码

4、CPU组成

CPU主要由运算器、控制器、寄存器组和内部总线等部件组成。

(1)运算器

● 算数逻辑单位ALU:执行算术运算和逻辑运算。

● 累加寄存器AC:暂存数据,为ALU提供工作区。

● 数据缓冲寄存器DR

● 状态条件寄存器PSW归属有争议

(2)控制器

● 程序计数器PC:存储下一条要执行指令的地址。

● 指令寄存器IR:存储即将执行的指令。

● 指令译码器ID。

● 时序部件。

5、CISC与RISC

CISC(复杂指令集)的特点:指令数量多,指令频率差别大,可变长格式,多种寻址方式,使用微码(微程序)实现,研制周期长。

RISC(精简指令集)的特点:指令数量少,频率接近,定长格式,单周期,多寄存器寻址,多通用寄存器,硬布线逻辑控制,适用于流水线。有效支持高级程序语言,优化编译。

6、流水线技术

流水线建立时间:第1条指令执行时间。

流水线周期:指令分段后,最长段时间。

流水线执行时间(默认使用理论公式,无答案时考虑实践公式)。

理论公式:流水线建立时间+(指令条数-1)*流水线周期。

实践公式:指令段数*流水线周期+(指令条数-1)*流水线周期。

吞吐率=指令条数/流水线执行时间。

最大吞吐率=流水线周期的倒数。

7、局部性原理

时间局部性:指程序中的某条指令一旦执行,不久以后该指令可能再次执行,典型原因是由于程序中存在着大量的循环操作。

空间局部性:指一旦程序访问了某个存储单元,不久以后,其附近的存储单元也将被访问,即程序在一段时间内所访问的地址可能集中在一定的范围内,其典型情况是程序顺序执行。

8、常见存储器

(1)按内容存取

● 相联存储器(如Cache)

(2)按地址存取

● 随机存取存储器(如内存)

● 顺序存取存储器(如磁带)

● 直接存取存储器(如磁盘)

(3)工作方式

● 随机存取存储器RAM(如内存DRAM)

● 只读存储器ROM(如BIOS)

9、Cache

在计算机的存储系统体系中,Cache是(除寄存器以外)访问速度最快的层次。解决CPU与主存之间速度容量不匹配问题。

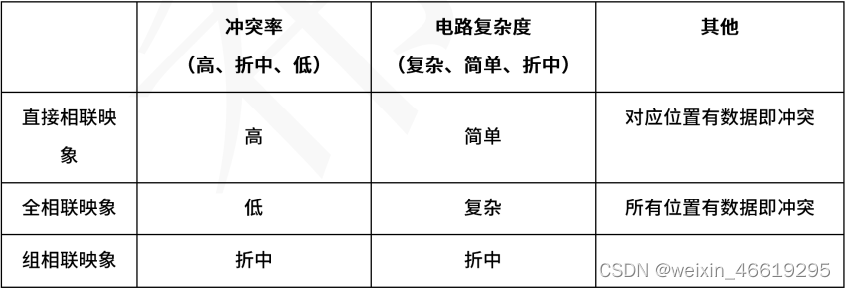

Cache与主存映射三种方式:

10、主存编址计算

内存单元数个数=最大地址+1=最小地址。

内存编址内容:按字编址(每个存储单元存放内容为机器字长一题干定义)、按字节编址(每个存储单元内容为1字节即8bit)。

内存总容量=存储单元个数*编址内容。

内存总容量=单位芯片容量*芯片片数。

芯片片数=内存总容量/单位芯片容量。

单位芯片容量=内容总容量/芯片片数。

![[附源码]Python计算机毕业设计Django高血压分析平台](https://img-blog.csdnimg.cn/85d39437b9f74270ab9c9369eda7a7ee.png)