学习步骤:

我会采取以下几个步骤来学习Cache存储器:

-

确定学习目标:Cache存储器作为一种高速缓存存储器,通常用于提高计算机系统的运行效率。因此,我需要明确学习Cache存储器的目的,包括了解其原理、结构和应用。

-

学习基础知识:在学习Cache存储器之前,需要先掌握计算机组成原理和计算机体系结构等相关基础知识。这些知识包括CPU、存储器、总线、中断、操作系统等,可以通过阅读教材、参考书籍或者网络资源等途径来学习。

-

深入学习Cache存储器:学习Cache存储器的过程中,需要了解其工作原理、逻辑结构和映射方式等关键概念。我会首先学习直接映射、全相联映射和组相联映射等不同的映射方式,以及它们的优缺点。然后,我会学习如何利用高速缓存来提高计算机系统的运行效率,包括读取数据、写入数据、替换数据等操作。

-

实践练习:在学习Cache存储器的过程中,我会通过实践练习来巩固所学知识。例如,通过搭建计算机系统来实现Cache存储器的应用,或者使用一些仿真软件来模拟Cache存储器的运行过程,以提高自己的实践能力。

-

查漏补缺:在学习Cache存储器的过程中,我会及时查漏补缺,通过阅读教材、参考书籍、网络资源或者向专业人士请教等途径来解决自己遇到的问题,以保证学习的质量和效果。

学习目标:

- 理解cache存储器的基本概念和作用,了解为什么要使用cache存储器。

- 掌握cache存储器的逻辑结构,包括cache存储器的块大小、块数、标记等关键参数以及cache与主存之间的映射方式。

- 理解cache存储器的读写策略,包括写直达和写回两种策略的区别和优劣,了解什么时候应该选择哪种策略。

- 掌握cache存储器的替换策略,了解LRU、FIFO等常用的替换算法的优缺点,以及如何选择最适合特定应用的替换策略。

- 熟悉cache存储器的预取策略,包括什么是预取、如何预取以及预取的优化技术等。

- 熟练掌握cache存储器的性能评估方法,包括cache命中率、命中时间、平均访问时间等指标,以及如何通过调整cache存储器的参数来优化性能。

这些目标可以帮助你全面地理解cache存储器的基本概念、逻辑结构、读写策略、替换策略、预取策略和性能评估方法,从而更好地应用和优化cache存储器。

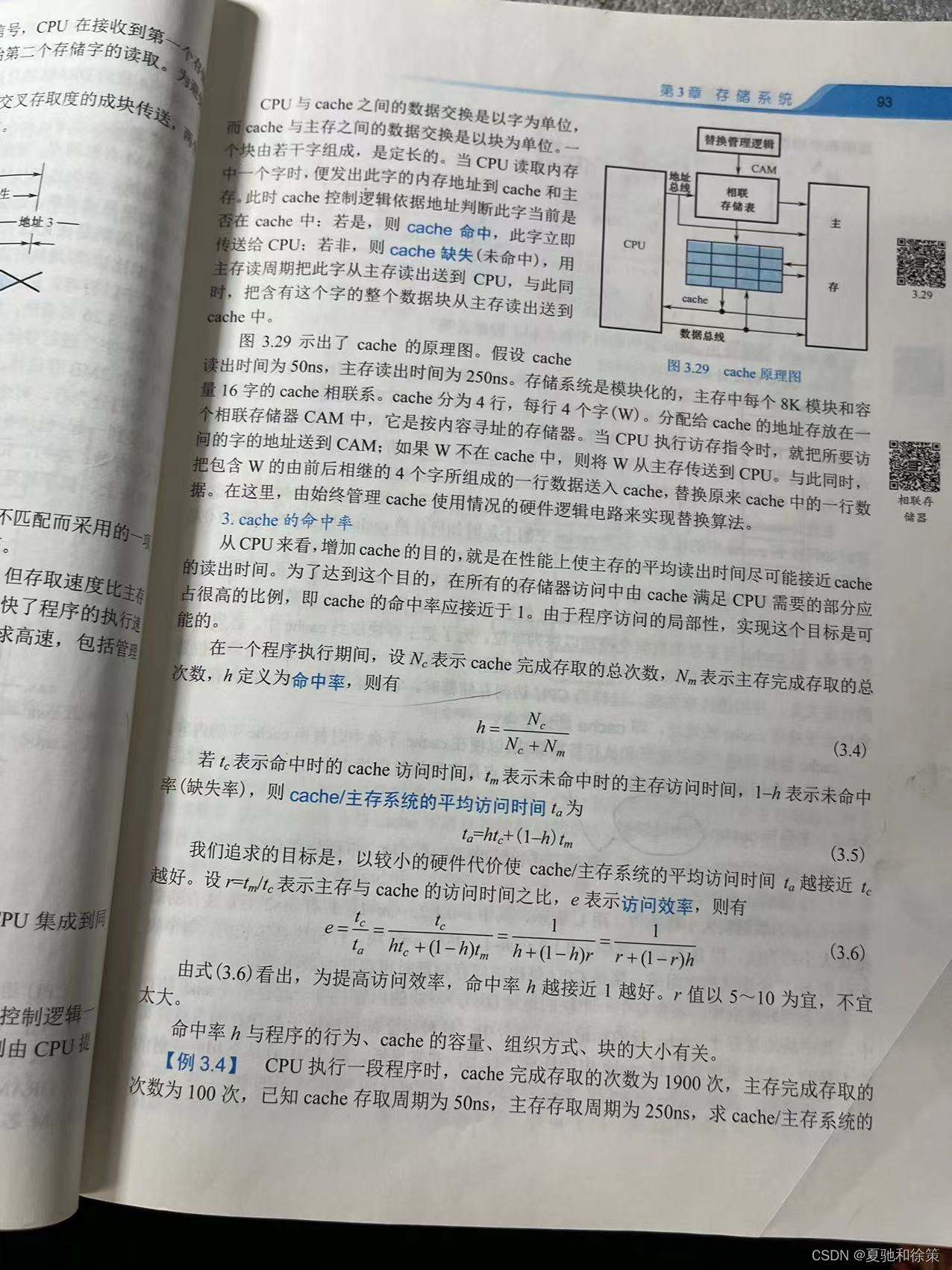

3.6.1 cache基本原理

Cache是一种高速缓存存储器,常用于加速计算机访问主存储器的速度。它的基本原理是通过在CPU和主存之间插入一层较小但较快的缓存存储器来提高CPU访问主存储器的效率。

Cache的工作方式是将最近被CPU访问过的数据和指令存储在其中,如果CPU要访问的数据或指令已经存在于Cache中,CPU就可以直接从Cache中读取,从而避免了访问主存储器的时间延迟。如果要访问的数据或指令不在Cache中,CPU就需要从主存储器中读取,并将其存储到Cache中,以便下一次访问时可以直接从Cache中读取。

Cache的运作过程可以分为三个阶段:

-

缓存访问:当CPU发出一个读写请求时,Cache会首先查看自己是否已经缓存了该数据。如果数据已经存在于Cache中,那么就直接从Cache中读取或写入;如果数据不存在于Cache中,则进入下一个阶段。

-

主存访问:当Cache无法命中(即无法从Cache中找到需要的数据)时,Cache会向主存发出一个访问请求,并等待主存响应。如果主存返回了需要的数据,则进入下一个阶段;否则,返回一个缺失异常。

-

写回:当Cache中的某些数据被修改后,Cache会在适当的时候将这些数据写回主存。写回可以在缓存替换时进行,也可以在Cache满时进行。

在Cache中,数据通常是以块的形式组织的,块的大小可以根据具体应用进行调整。当一个块被存储在Cache中时,还会同时存储一些元数据,例如该块在主存中的地址、块的状态(是否被修改)、最近访问时间等信息。这些元数据可以帮助Cache进行块的替换、调度和维护。

总之,Cache的基本原理是通过在CPU和主存储器之间插入一个较小但较快的缓存存储器来提高CPU访问主存储器的效率。它的工作方式包括缓存访问、主存访问和写回三个阶段,数据通常以块的形式组织,并且会同时存储一些元数据来帮助Cache进行块的替换、调度和维护。

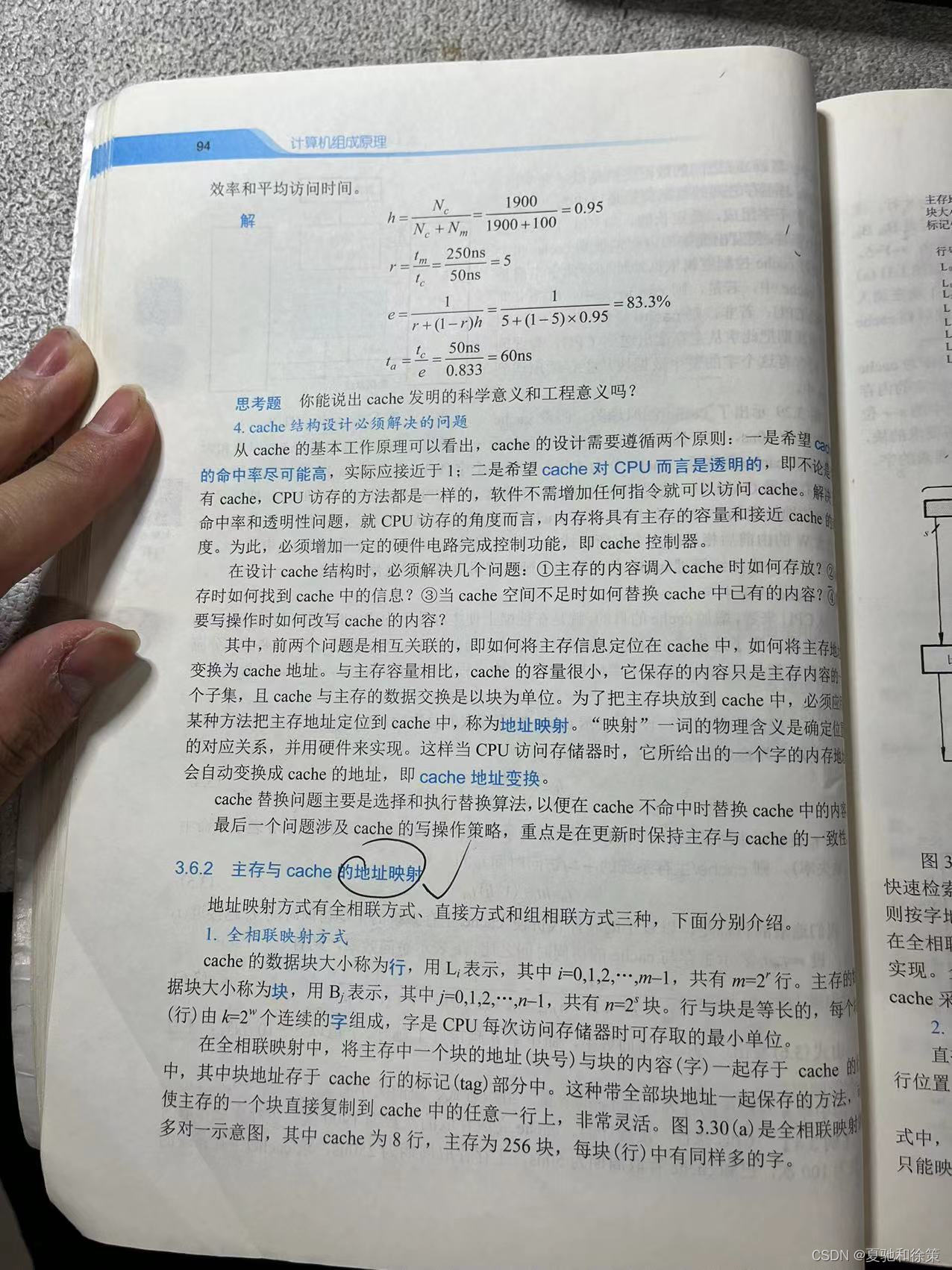

3.6.2 主存与cache的地址映射

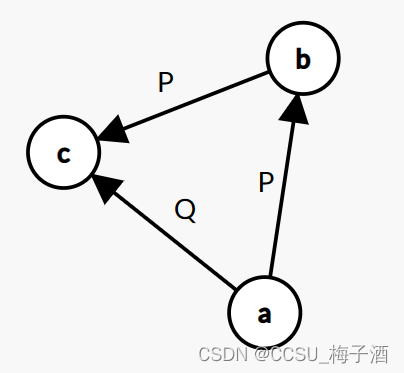

在计算机中,缓存(Cache)是位于主存储器和处理器之间的高速存储器,用于暂时存放处理器需要频繁访问的指令和数据。为了使缓存的访问速度尽可能的快,常常将其设计为与处理器直接相连,而与主存储器之间采用缓存地址映射方式进行交互。

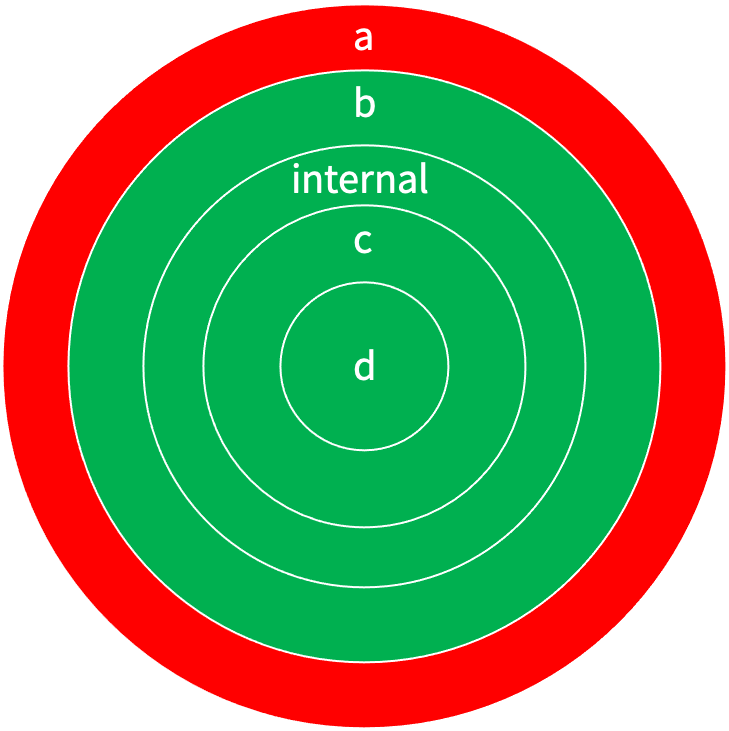

常见的缓存地址映射方式有三种:直接映射、全相联映射和组相联映射。

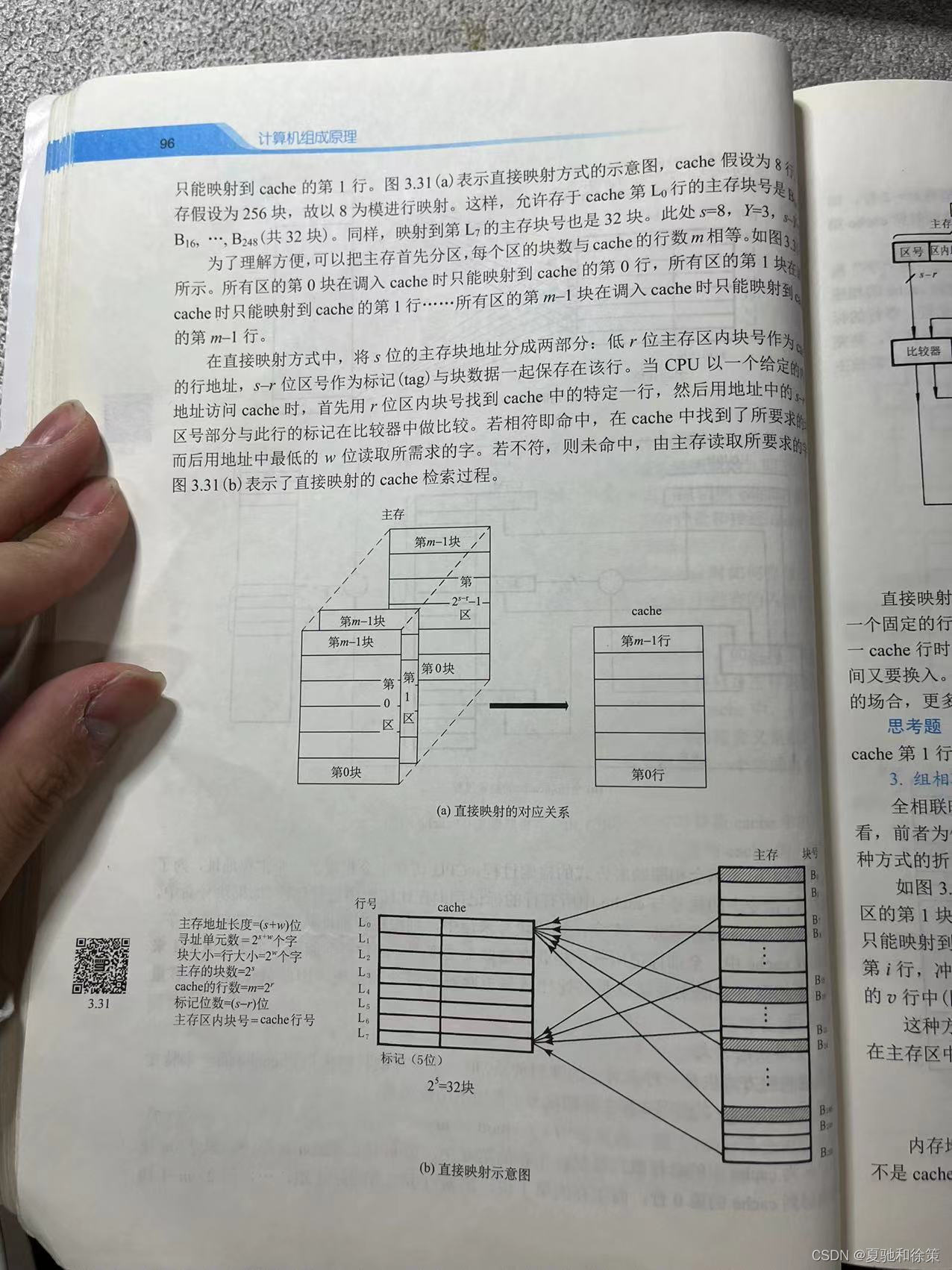

直接映射是指将主存地址的一部分直接映射到缓存地址中,每个主存块都只能映射到缓存中的一个固定位置,当需要读取一个主存块时,先将其地址通过哈希函数映射到缓存地址中,然后访问该位置即可。由于每个主存块只能映射到固定的一个位置,因此在缓存容量有限的情况下,会存在缓存冲突的情况,即多个主存块映射到相同的缓存位置,需要采用替换算法来确定替换哪个缓存块。

全相联映射是指所有的主存块都可以映射到任何一个缓存位置,因此每个缓存位置都可以存储任意主存块,缓存访问时需要遍历所有的缓存块进行查找。由于缓存位置数量有限,同样存在缓存冲突和替换算法的问题。

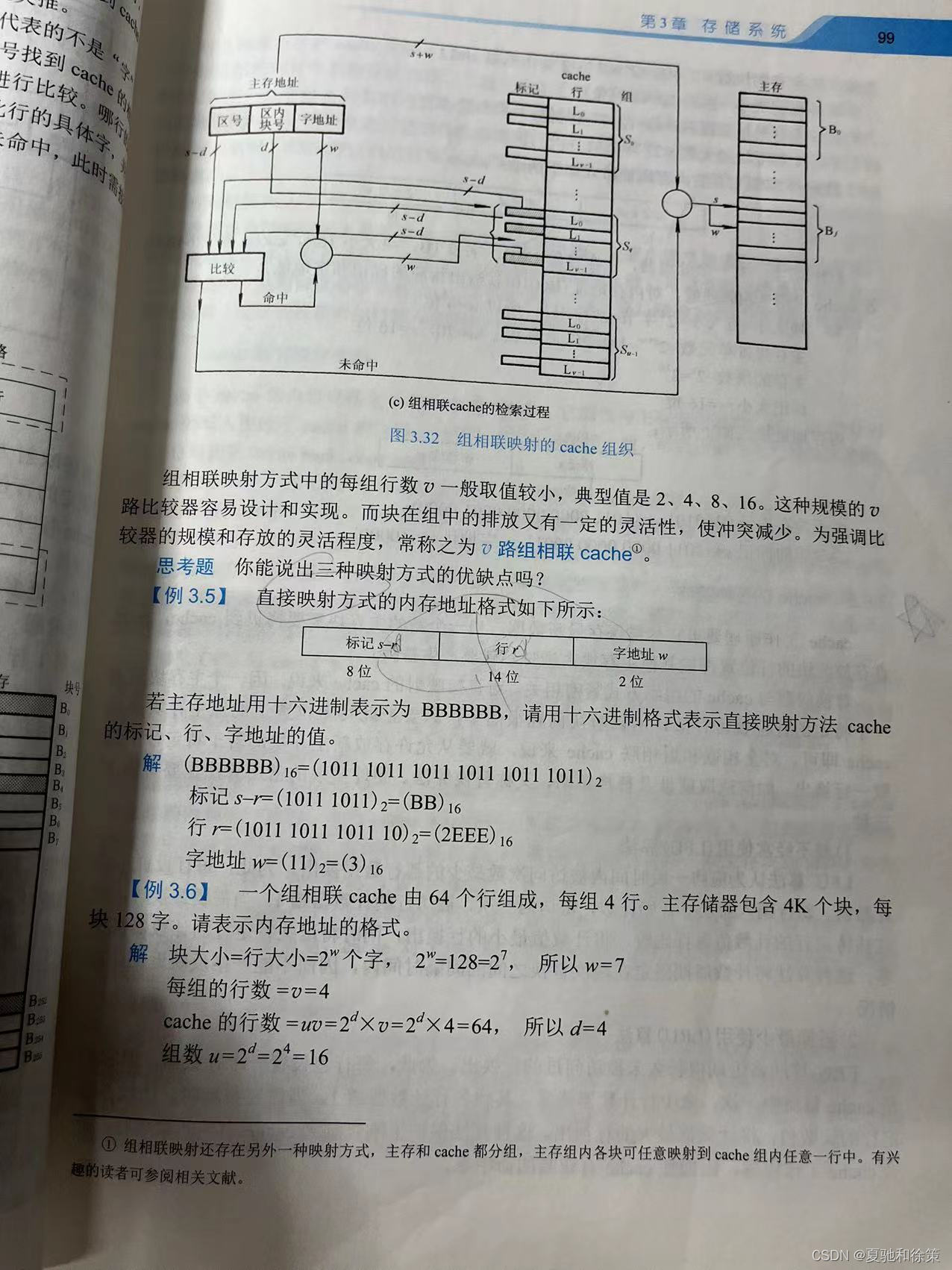

组相联映射则是将缓存分为多个组,每个组中包含多个缓存块,一个主存块可以映射到任意一个组中,但只能存储在该组的某个缓存块中。与直接映射相比,组相联映射减少了缓存冲突的可能性,而与全相联映射相比,可以降低查找的时间。

在实际应用中,通常采用组相联映射作为主流的地址映射方式,因为它兼顾了直接映射和全相联映射的优点,并且易于实现。

3.6.3 cache的替换策略

在 Cache 中,如果 Cache 中没有被请求的数据,则需要从主存中获取数据。而 Cache 有一个固定的容量,当 Cache 已满时,需要使用替换策略将某些已存在的缓存数据替换出去,以便给新的数据腾出空间。Cache 替换策略的目的是使 Cache 中的数据尽可能多地被使用,从而提高 Cache 命中率,减少对主存的访问次数。

常见的 Cache 替换策略有以下几种:

-

直接映射:每个主存块只能映射到 Cache 中的一个固定位置,替换时只能替换这个位置上的块。这种方式简单,但容易发生冲突,导致 Cache 命中率低。

-

全相联映射:每个主存块可以映射到 Cache 中的任意一个位置,替换时选择最近最少使用的块。这种方式可以有效避免冲突,但需要更多的硬件实现,比直接映射复杂。

-

组相联映射:Cache 被分成多个组,每个组中包含若干个 Cache 行,每个主存块只能映射到一个组中的某个行,替换时只在该组中寻找最近最少使用的块。这种方式结合了直接映射和全相联映射的优点,较好地平衡了命中率和实现复杂度。

以上是常见的 Cache 替换策略,实际中也可以根据具体的应用场景选择合适的替换策略。

3.6.4 cache写操作

在计算机系统中,cache存储器的写操作策略指的是当CPU写入数据时,这些数据是直接写入主存,还是先写入cache,再由cache写回主存的方式。常见的写操作策略有两种:

-

写直达(Write-Through)策略:当CPU写入数据时,cache和主存同时被写入。这样可以保证cache和主存中的数据一致,但写操作需要两次存储器访问,因此写操作的速度会比较慢。

-

写回(Write-Back)策略:当CPU写入数据时,只有cache被写入,而不是直接写入主存。当cache中的某个数据块被替换出去时,才将其写回到主存中。这样可以减少写操作的存储器访问次数,提高写操作的速度。但是,由于cache和主存中的数据可能不一致,因此需要在某些情况下进行额外的操作来保证数据一致性。

在使用写回策略的cache中,通常需要使用一些额外的硬件来保证数据一致性。例如,可以为每个cache块设置一个有效位和一个修改位。当某个cache块被读入时,有效位被设置为1,修改位被设置为0。当该cache块被写入时,有效位仍然保持为1,但是修改位被设置为1。当该cache块被替换出去时,如果修改位为1,则需要将该cache块的数据写回到主存中,以保证数据的一致性。

3.6.5 Pentium 4 的cache组织

3.6.5 Pentium 4 的cache组织

Pentium 4 是英特尔公司于2000年推出的一款处理器,其cache组织如下:

-

Level 1 (L1) Cache:分为数据缓存和指令缓存两部分,每个缓存大小均为8KB,采用4路组相联的方式,每路大小为2KB。

-

Level 2 (L2) Cache:大小为256KB或512KB,采用8路组相联的方式,每路大小为32KB,运行频率与CPU主频相同。

-

Level 3 (L3) Cache:大小为2MB或4MB,采用16路组相联的方式,每路大小为256KB。在早期版本中没有L3 Cache,后续推出的Pentium 4 Extreme Edition和Pentium D处理器才开始搭载L3 Cache。

Pentium 4 的cache组织采用分层式结构,即L1 Cache作为第一层,L2 Cache作为第二层,L3 Cache作为第三层,层与层之间采用包含关系,即L2 Cache包含L1 Cache,L3 Cache包含L2 Cache。这样的设计可以提高数据访问效率,减少数据访问延迟。

3.6.6 使用多级cache减少缺失损失

多级Cache是一种减少缺失损失的策略。其基本思想是在CPU与主存之间增加一层或多层Cache,让缓存能够更好地利用程序访问的局部性原理,从而减少缺失率和缺失开销。

在多级Cache中,每一级的Cache容量和速度都会不同。一般情况下,较小但速度更快的Cache作为L1 Cache,接下来的较大而速度相对较慢的Cache作为L2 Cache,再之后可能还有L3 Cache等。不同级别的Cache之间也可能采用不同的替换算法和写操作策略。

当CPU需要访问数据时,它首先会检查L1 Cache,如果数据在L1 Cache中,则直接返回数据;如果数据不在L1 Cache中,则会向下一级的Cache(如L2 Cache)中查询,以此类推。当数据在Cache中被找到后,它会被加载到更高级别的Cache中,以提高下一次访问的速度。

使用多级Cache的好处在于,它能够减少缺失率和缺失开销,因为更大、更慢的Cache可以容纳更多的数据,并且更快的Cache可以更快地提供数据。这样,访问速度会更快,缺失率和缺失开销也会更小。不过,多级Cache也会增加硬件成本和设计难度,需要考虑多级Cache之间的协作和一致性问题。

总结:

Cache存储器作为一种高速缓存,其理解和掌握对于计算机体系结构的学习和实践都是至关重要的。以下是Cache存储器的重点、难点和易错点:

重点:

- Cache存储器的基本原理:Cache存储器是主存储器的一种高速缓存,用于存储CPU频繁访问的指令和数据。

- Cache存储器的地址映射:包括直接映射、全相联映射和组相联映射,不同的映射策略会影响Cache存储器的效率和命中率。

- Cache存储器的替换策略:包括最近最少使用算法(LRU)、先进先出算法(FIFO)和随机替换算法等,不同的替换策略会影响Cache存储器的性能。

- Cache存储器的写操作策略:包括写回和写直达两种,不同的写操作策略会影响Cache存储器的一致性和性能。

- 多级Cache存储器的实现:包括L1 Cache、L2 Cache、L3 Cache等多级Cache存储器的实现和管理,可以有效减少缺失损失和提高系统性能。

难点:

- 理解Cache存储器和主存储器的地址映射关系以及不同映射策略的优缺点。

- 掌握Cache存储器的替换策略,特别是LRU算法的实现。

- 理解Cache存储器的写操作策略及其影响,包括一致性和性能方面的问题。

- 理解多级Cache存储器的实现原理和管理方法。

易错点:

- Cache存储器的地址映射策略选择不当会影响Cache的效率和命中率。

- 替换策略的实现不当会影响Cache的性能,特别是LRU算法的实现需要注意细节。

- 写操作策略的选择和实现需要注意一致性和性能的平衡。

- 多级Cache存储器的实现和管理需要注意不同级别Cache之间的协作和数据一致性。

![[230503] 2021年托福阅读真题第1篇|Grinding Grain 磨粒](https://img-blog.csdnimg.cn/1faf66b6335c474dbc828c9f81637a1c.png)