目录

- 一、简介

- 二、PCIe物理层结构及功能

- 2.1 PCIe端对端连接方式

- 2.2 PCIe组成

- 2.2.1 逻辑层(Logic)

- 1 发送逻辑

- 2 接收逻辑

- 2.2.2 电气层(Electrical)

- 1 物理层-电气(Physical Layer Electrical)

- 2 数据传送----差分方式

- 2.2.3 PLP介绍

- 三、其他相关链接

- 1、PCI总线及发展历程总结

一、简介

本文主要对PCIe物理层的组成、功能进行详细的总结,通过图文的方式方便读者快速掌握。

物理层物理层是PCIe总线的最底层,将PCIe设备连接在一起。PCIe总线的物理电气特性决定了PCIe链路只能使用端到端的连接方式。

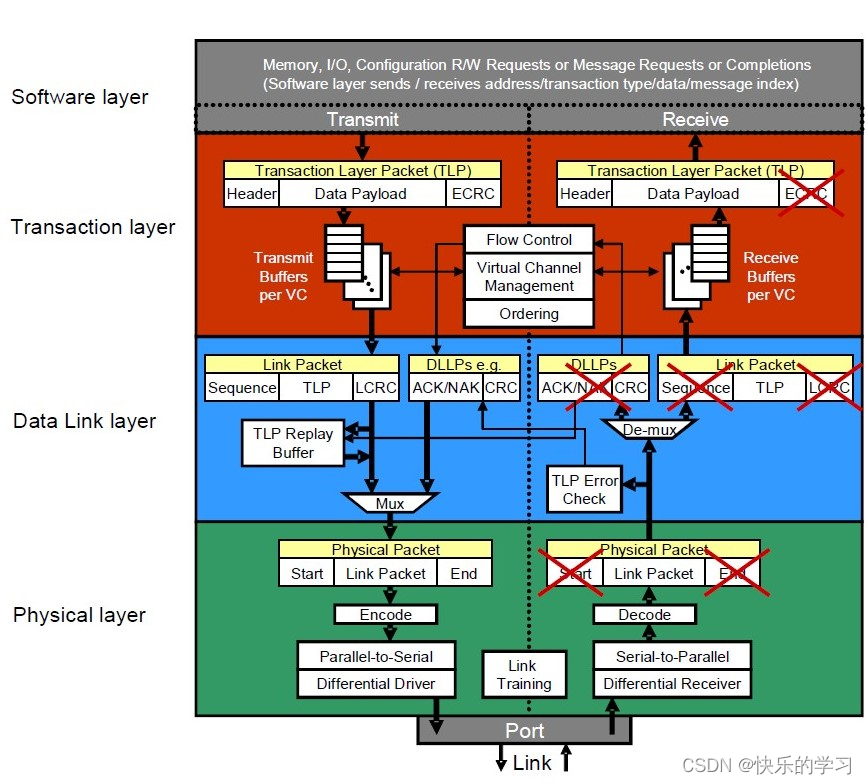

PCIe总线的物理层为PCIe设备间的数据通信提供传送介质,为数据传送提供可靠的物理环境,发送端数据链路层(Data Link Layer)的DLLP和TLP报文通过物理层(Physical Layer)发送至接收端的物理层,再传送至接收端的数据链路层。物理层是PCIe体系结构最重要,也是最难以实现的组成部分。

PCIe总线的物理层定义了LTSSM(Link Training and Status State Machine)状态机,PCIe链路使用该状态机管理链路状态,并进行链路训练、链路恢复和电源管理。PCIe总线的物理层还定义了一些专门的“序列”,有的书籍将物理层这些“序列”称为PLP(Phsical Layer Packer),这些序列用于同步PCIe链路,并进行链路管理。值得注意的是PCIe设备发送PLP与发送TLP的过程有所不同。对于系统软件而言,物理层几乎不可见,但是系统程序员仍有必要较为深入地理解物理层的工作原理。

二、PCIe物理层结构及功能

2.1 PCIe端对端连接方式

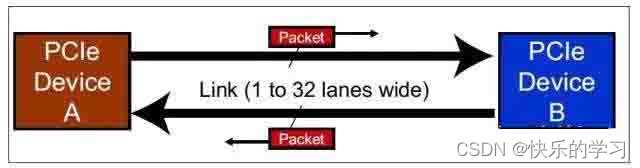

与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。PCIe总线使用的层次结构与网络协议栈较为类似。下图端到端的数据传递PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如下图所示。

2.2 PCIe组成

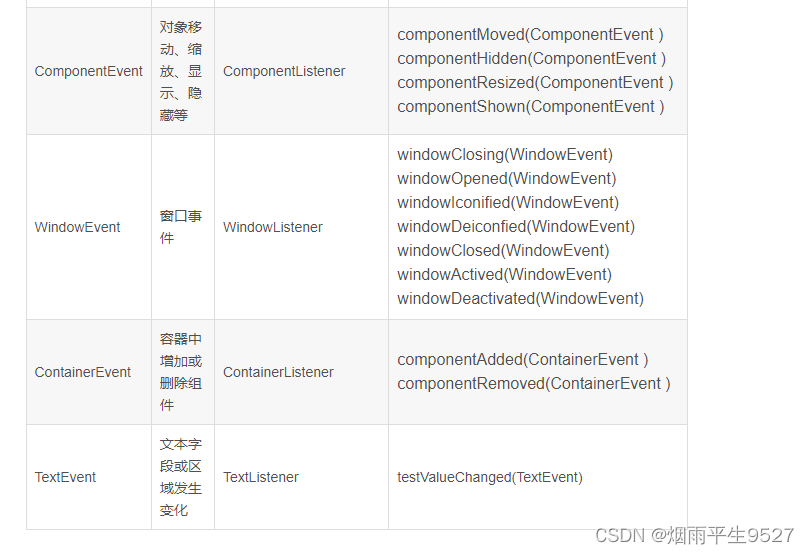

物理层又分为两层:逻辑层(Logical)和电气层(Electrical)。逻辑层主要负责与数据链路层之间的数据交互,由发送逻辑Tx和接收逻辑Rx组成。电气层是物理层的模拟接口,包括了差分信号驱动和接收器。

2.2.1 逻辑层(Logic)

1 发送逻辑

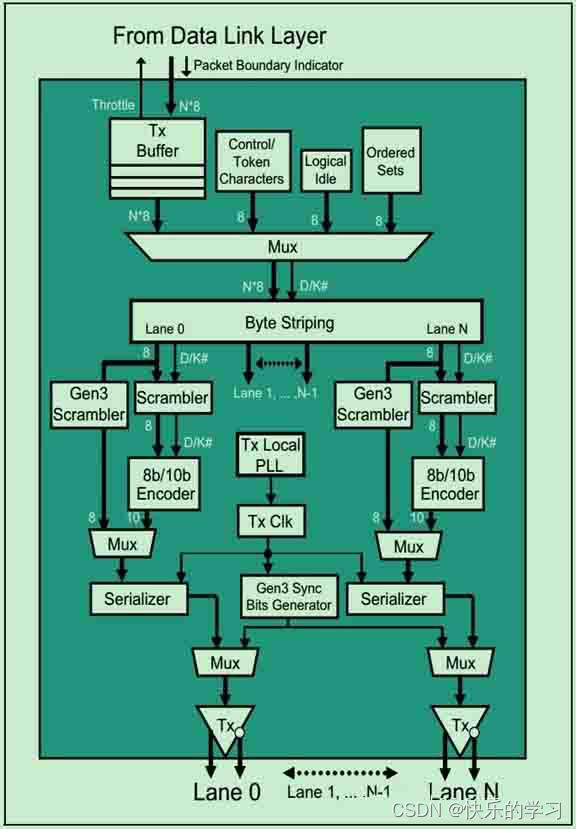

1、 从发送端数据链路层下发的DLLP/TLP在到达物理层后,会先放入Tx Buffer中。在Tx buffer中,DLLP/TLP被加上前缀Start和后缀End封装帧;

2、 多路复用器(MUX):DLLP/TLP通过多路选择器MUX;

3、 字节拆分(Byte Stripping)逻辑:由于PCIe总线可能包含多个Lane, Byte Stripping组件将DLLP/TLP数据报文按照各个字节(character)依次分发到不同的Lane;

4、扰频器(Scramble):数据进入每个Lane之后都会做加扰,使用一种算法,产生伪随机数,以便伪随机的加扰数据包的每个字节(异或);

5、8b/10b编码器:将已加扰的的字符变为10比特的符号(symbol),8/10b编码( Only for Gen1/2), 128b/130b编码(Only for Gen3);

6、并行到串行转换器:将10比特的符号转化为串行比特流。8b/10b编码器250MHz的频率输出到转换器,转换器以2.5GHz的频率定时输出串行比特流,最后发送到PCIe链路中。

具体流程图如下:

2 接收逻辑

1、接收时钟恢复:在串行比特流中,有频繁的1-0,0-1的转换,因此接收器PLL可以用来同步接受时钟与发送时钟。根据恢复的时钟定时发送10b的符号,并不断调整两个时钟之间的微小时钟频率变化(恢复时钟与本地产生的相关时钟);

2、弹性缓冲区:接收端的逻辑层从PCIe链路的各个Lane中获得串行数据,10b的符号被定时输入到弹性缓冲区;

3、8b/10b解码器:将10b的符号转换回8b的字符,同时检查进入的10b数据是否有错误;

4、去扰频器(De-Scramble):将加扰数据包再现为去除加扰的数据包流;

5、反字节拆分(Byte Un-Stripping):将每个通道的字节进行反拆分形成字节流,送入过滤器;

6、过滤器逻辑:将串行字节流中的逻辑空闲系列,各类有序集去除;将TLP和DLLP和其对应的开始结束边界字符一起送到接收缓冲区;

7、接收缓冲区:检查Start和End标识后送入Rx Buffer,保存TLP和DLLP,准备发送至数据链路层;

接收逻辑流程图如下:

2.2.2 电气层(Electrical)

1 物理层-电气(Physical Layer Electrical)

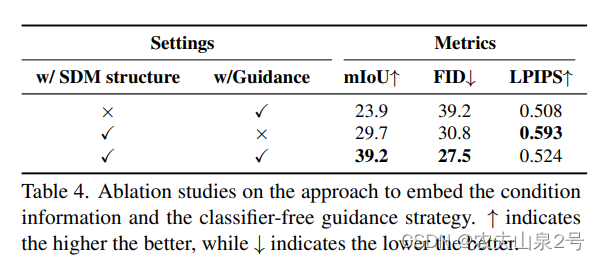

链路上的物理发送器和接收器AC 耦合的,如下图。AC 耦合电容器的大小在 75~200nF 之间。发送器的 DC 共模电压时在链路定向和初始化期间确定的。DC 共模阻抗通常是 50Ω,而差动阻抗通常是 100Ω。

术语"交流耦合”仅表示设备之间的物理路径中放置有电容,并用于通过信号的高频(AC交流)分量,同时阻塞低频(DC直流)部分。许多串行传输都使用这种方法,因为它允许发送器和接收器的共模电压(信号的正负交叉的电平,即0, 1电平之间)不同,这意味着它们不需要具有相同的参考电压。

2 数据传送----差分方式

PCIe链路使用差分信号进行数据传送,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe链路可以由多个Lane组成。高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。该电容也被称为AC耦合电容,具体 如下图所示。

差分信号的应用:

一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。因此差分信号可以使用更高的总线频率。此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。

具体计算如下图:

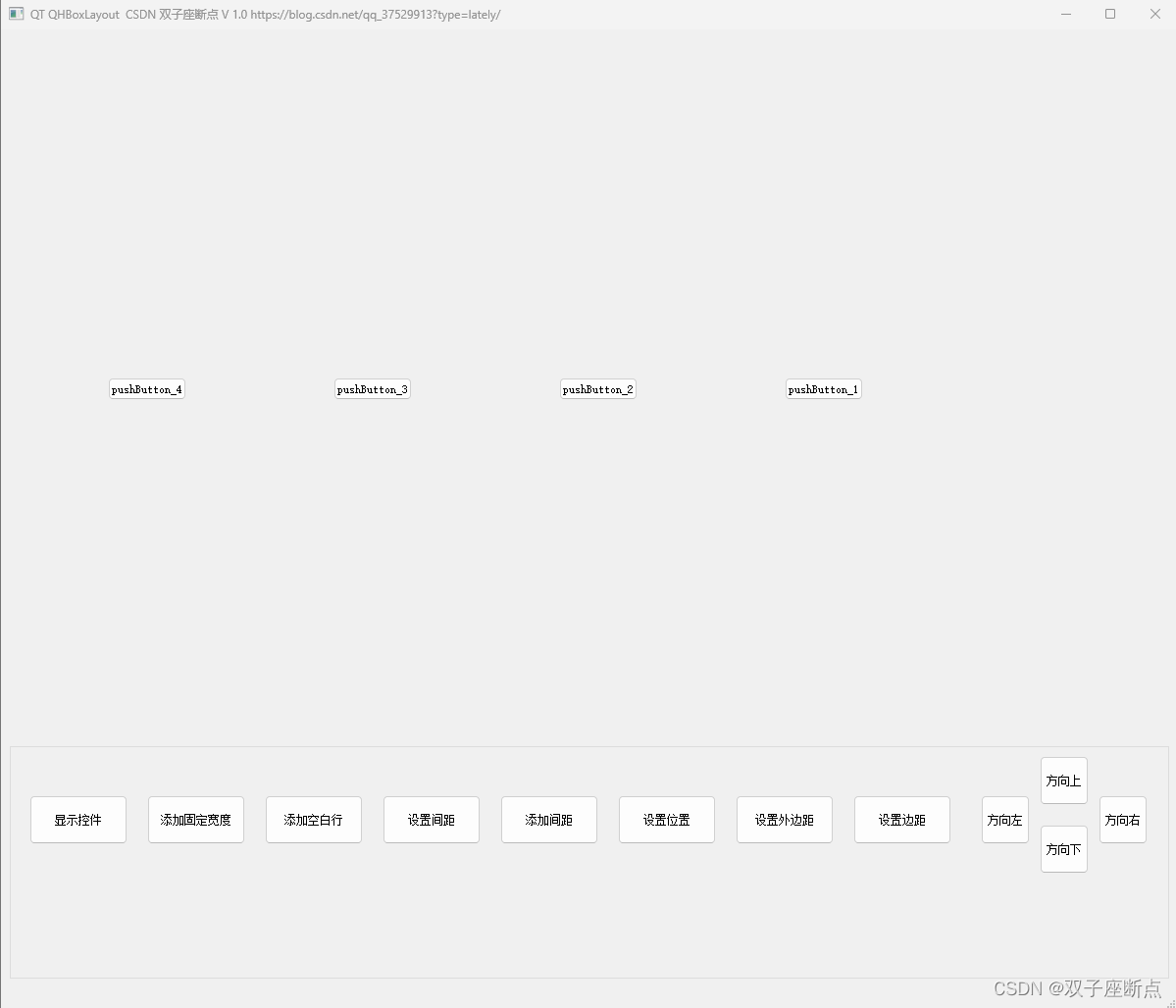

2.2.3 PLP介绍

PLP(Physical Layer Package)是物理层封装的数据包,源于发送器设备的物理层,终止与接收器设备的物理层。PLP 是一种非常简单的数据包,开始是 1 字节的 COM 字符,后面是定义 PLP 类型以及含有其它信息的 3 个或多个字符。PLP 的大小是 4 字节的整数倍,规范将这种数据包成为有序集(Ordered Set),PLP包在链路上两个直接连的数据链路层之间传输(没有路由功能),主要用于链路训练过程(LinkTraining process),时钟容差补偿(Clock Tolerance Compensation,CTC)以及更改链路功耗状态(Changing Link Power States,包结构如下图所示。 命令集/有序集(Ordered Sets)

命令集/有序集(Ordered Sets)

设备之间发送的流只使用物理层。尽管这种信息对于接收端来说很容易进行识别,但是它并没有被封装成数据包的形式,原因是它没有包起始字符和包结束字符。因此作为一种替代方法,这种信息被组织成了一种被叫做”命令集(OrderedSets) ”的东西,如上图所示,对于Gen1和Gen2的数据率下,一个命令集使用一个单独的COM字符作为起始,然后后面接着3个或以上的其2他字符用于定义要发送的信息。命令集的大小总是4byte的整数倍,下图展示了一个命令集的例子。在Gen3操作模式中,命令集的格式就不同于上述的Gen1/Gen2格式了。

物理层会对DLP或者TLP包进行封装加上start和end,如下图所示: