doc说明

一级标题分大的,二级标题尽量加,三级标题是具体问题

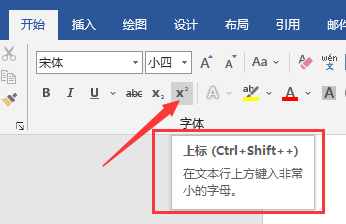

语法

我的老毛病-易错的

多驱

复制粘贴导致前后一样

管脚约束还是直接选吧

多驱动

Vivado WARNING:Multi-driven net Q with xth driver pin 警告的原因和消除方法

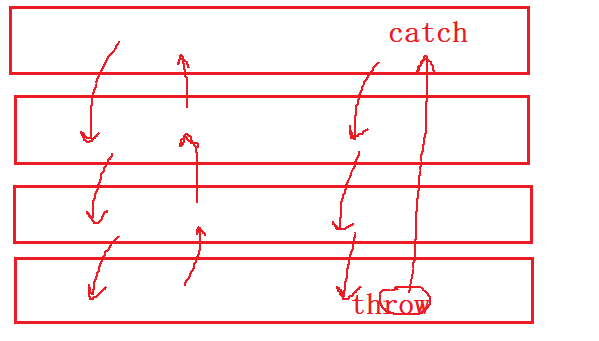

出现这个警告的原因是很简单的。大多是编写出了下面这样的烂代码:一个信号被两个数据源驱动

也就是,一个寄存器两次赋值

这个错误是因为对于同一个信号,在不同的地方给它赋值。比如在两个always块中给同一个信号赋值。但是要注意,综合报错的位置不一定是错误赋值的位置,追踪定位这个错误的方法:

1:在整个工程文件中,搜索出现多驱动的信号,详细对照这个信号的赋值情况

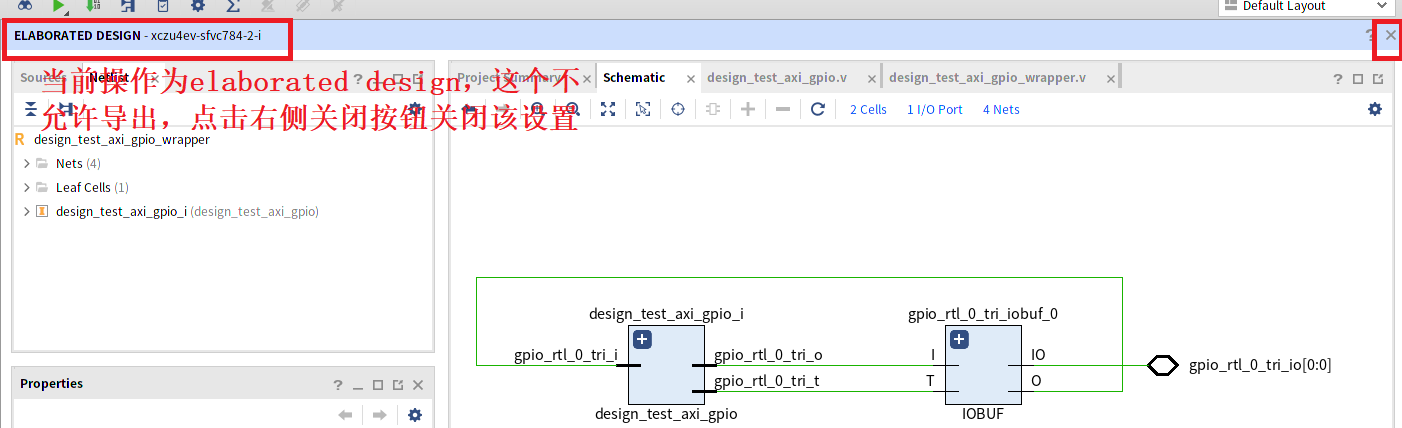

2:直接生产RTL Schematic, 通过生产的电路图,查看是否有多驱动的情况出现

3:注意输入信号不要赋值

端口声明

[Synth 8-2543] port connections cannot be mixed ordered and named

端口声明多写了个逗号

忘记更新文件

不会的

寄存器

reg [7:0]mem[31:0]前面的是深度/个数,后面的是宽度

其他

1)expect a comma,一般是定义的时候少了相应的;

比如说,wire【15:0】dout没有加上;就会出现这种错误;

2)A net is not a legal lvalue in this context.定义类型错误,将wire型定义成了reg型的,

- reg ‘out_valid’ declared in a module/macromodule,cannot also be declaredinput or inout;

这种类型应该是模块之间的定义出现了错误,需要检查连接模块之间的连线是否定义成了一样

- SystemVerilognamed argument: use –sv switch to enable this SystemVerilog construct.

一般是在调用module的时候会出现这种情况;注意在时序

- expecting an ’=’ or ‘<=’ sign in an assignment

可能是因为定义错误导致的,时序电路和组合逻辑采用的赋值方式不同,分别采用阻塞赋值和非阻塞赋值等方式。

6)‘inn1’: undeclaredidentifier没有声明相应的变量为wire型还是reg型的

7)input/output/inout‘avg’ declared as vector or array, then redeclared as scalar.(无向量结构)

是以下的错误,定义input【15:0】avg;wire avg;没有加上范围向量。

8)Part-selectoperator cannot be applied to scalar.

avg <= sum[18:3] + {15’b0, sum[2]} ;这种错误,选择部分的的内容也不可以加到向量中去。前一部分可以采用移位的方式来实现选位的功能;也可能是由于sum的位宽定义错误;(可能都没有定义位宽,默认为1)

9)bit-select operatorcannot be applied to scalar;单个bit的运算不可以加到向量中去。第8)9)问题可能有sum定义的位宽不对导致(可能都没有定义位宽,默认为1);也可能是由于verilog不提供相应的解决的选定位数的方法导致的;

10)port sizes differin port connection.位宽不一致导致的逻辑错误。

11)illegal out(或者output)port specification.定义输出的属性错误

12)expecting a rightparenthesis (‘)’)是指少了右括号);相应的expecting a semicolon (‘:’)是指少了分号。可能是由于在if判断语句中写如if ( a= b ),导致的错误,对的应该为if ( a == b)

13 ) illegal expression primary.可能是类似于将always写成always这样的语法错误。

14)A Verilog keyword was found where an identifier wasexpected.程序中出现了相应的Verilog的关键字,有一个关键字列表,是一些不可以被定义为变量的名字的列表,这个需要注意。

作者:集成电路基础与数字集成电路设计

链接:https://www.jianshu.com/p/1251e40e121c

来源:简书

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

ifdef…elsif…else…endif

`ifdef CONDITION

EXPRESSION1

`elsif CONDITION2

EXPRESSION2

`esle

EXPRESSION3

`endif

仿真

clk

1. timescale 没设置好,导致时钟太大,系统跑不动,所以卡住了

【问题描述】:替换mig时,因为mig和系统的时钟不同步,需要解决跨时钟域的问题,所以添加了axi_clock_converter ip。类似于一位的fifo,左边s连接系统大概50Mhz,右边m连接mig,200Mhz。

1.在使用该IP时,发现s_axi正常,m_axi数据不对出现x态。(正常情况下应该就只有时钟转换而已,s什么样,m出来什么样)

2.系统拉出来mig的线,没有正常运行出现的数据

【问题发现】:看数据流向发现s_axi进入的数据正常,m那边却会变成x态,对比rst没问题,看一下时钟,发现量级不对。发现只在run.sh里面加了timescale但是没有在fpga_top_tb里加,加上重跑就好了。

【问题解决】:在顶层测试文件里添加timescale1ns/1ps

【学到】1. IP结构去看xilinx生成的,更快更准确

- 按着数据流向去查问题,往前找

- 注重rst和clk,波形是不是对,clk量级是不是对

rst

#综合Synthesis

vivado synth 8-976 variable should not be used in outpupt port connection

模块端口输出不能到REG寄存器,wire变量可以在always 语句中做右值,但左值只能是REG型,

output reg pready; ❌

output wire pready⭕️

[Synth 8-462] no clock signal specified in event control

同时有

[Synth 8-7124] Expression condition using operand "ARESETn " doesn`t match with the corresponding edges in even control

原因:always @(posedge clk or negedge rst)

- rst没用上

- rst没用对

必须要用到rst,而且一定要注意if(!rst)

[ 解决方法] 😄

module counter( input clk, enable, clear, output reg [3:0] q);

always @ ( negedge clk, negedge enable) begin

if (!enable) begin

q <= q;

end

else begin

q <= q + 1;

end

end

endmodule

vivado综合出现[Synth 8-91] ambiguous clock in event control

查阅相关资料,目前有两种情况:

1.always[vivado 导出硬件出现“ERROR: Common 17-69] Command failed: write_hw_platform is only supported for synthesized, implemented, or checkpoint designs close_design”错误敏感变量没有得到使用 常见有rst信号

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-CIrH9dih-1662086243536)(D:\Myfiles\keepgoing\note\assets\v2-1cfa90d6be3142aa136d7fe2dff62368_720w.jpg)]

代码修改如下即可:

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-FUe1pWOv-1662086243537)(D:\Myfiles\keepgoing\note\assets\v2-5c4e69df974423932f946c517791abf2_720w.jpg)]

2.always块中语法问题

敏感变量都有使用,为何还会出现该问题,检查语法是否出现和rst并行的if语句。

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-vXpgL19w-1662086243540)(D:\Myfiles\keepgoing\note\assets\v2-9ffc9c47b45c7e949549be3260c56021_720w.jpg)]

去掉该层次的if即可:

,所以数组大了之后电路也就大了,综合起来当然更加耗费时间。

多了解一下fpga性能优化,你就不会这么写code了,深度和宽度是影响fpga收敛和性能德一方面,synthesis久因为vivado尝试不同的stratage,甚至是让综合算法进去了一个时间复杂度最坏的情况。再加上也有可能是你的机器性能原因

Vivado报错:[Runs 36-527] DCP does not exist

问题描述:综合工程时,某个IP文件被标红,出现[Runs 36-527] DCP does not exist… 的报错

解决办法:如果是在windows系统上用Vivado打开工程,当工程路径过长时,可能会出现这样的问题。比如:

D:\BaiduNetdiskDownload\FPGA\DBF\fpga-filter-implementation-master\fpga-filter-implementation-master\LMS_Simulation\LMS_Adaptive_Filter.runs\clk_wiz_0_synth_1

只要把工程转移到短一点的路径,再打开综合就行了。

参考链接:https://forums.xilinx.com/t5/Design-Entry/Runs-36-527-DCP-does-not-exist/td-p/1215525

设计

分频程序编译错误,显示[Vivado 12-4739] create_clock:找不到 ‘-objects [get_ports clk_p]’ 的有效对象。

编写了一个简单的分频程序,想要把200MHz的时钟作为输入,输出2MHz的时钟信号。但是在编译的时候却提示了一系列的错误。包括:[Vivado 12-4739] create_clock:未找到"-对象 [get_ports clk_p]"的有效对象。[Common 17-55] "set_property"需要至少一个对象。[放置 30-494] 设计为空分辨率:检查opt_design是否删除了设计中的所有叶单元格。检查是否已实例化并连接了所有顶级端口。经过查询,发现这可能是因为端口名称不匹配、没有输出等原因导致的。但是经过反复的检查,我认为我的程序并没有这样的问题,所以想请教一下大家该怎么解决这个问题。主程序、约束文件与激励文件在附件中。板子用的型号是:xc7a100tfgg484-2,Vivado版本为2020.1

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-hcdOM6x3-1662086243543)(D:\Myfiles\nut\FPGA\assets\renditionDownload.png)]

BEST SOLUTIONvtf_led_test.v 是仿真用的文件,综合时不能使用,否则会因为没有输入输出,所有的逻辑会被删除,包括正常的输入输出port.

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-uxnmjMk5-1662086243558)(D:\Myfiles\nut\FPGA\assets\renditionDownload-1638955888321.png)]

我是同样的错误,出现错误的原因是:

将tb文件放到了design sources中,而没有放到sim中

#其他

##路径不要太长!

Windows操作系统对路径长度有260个字符的限制,这可能会影响Vivado工具。为避免此问题,请在创建项目、定义IP或托管IP项目以及创建块设计时使用尽可能短的名称和目录位置

3. vivado 12-4739

找不到port

哎,真的是,你综合tb哪来的端口呢?被你气死啊

4. Netlist 29-358 reg of type FDCP cannot be timed accurately

异步时序的问题

5. port connections cannot be mixed ordered and named

错误原因:tb端口声明的最后一个后面多加了一个逗号

!删除端口的时候要仔细看看符号啊

xvlog.log

ERROR: [VRFC 10-1247] port connections cannot be mixed ordered and named

对于verilog十分不熟悉的我每写一段代码都要Debug很久。在例化一个模块的时候,由于涉及到的输入输出太多,complie出现了上述错误。

问题的解决方案

。。。可能是因为某个位置多打了一个逗号。。。

6. [DRC 23-20] Rule violation (REQP-61) - IBUFDS has invalid driver

Hi

I am doing one project in Vivado Vertx7 Evaluation board, during implementation I am getting one error which I have mention below.

I get these errors in implementation:

[DRC 23-20] Rule violation (REQP-61) ibufds_connects_I_active - IBUFDS mb_core/clk_wiz_1/inst/clkin1_ibufds pin I has an invalid driver.

[DRC 23-20] Rule violation (REQP-62) ibufds_connects_IB_active - IBUFDS mb_core/clk_wiz_1/inst/clkin1_ibufds pin IB has an invalid driver.

Note:- In this project I am using Microblaze processor and Axi_ahb_litebridge.

I am requesting forum member to help in this regards.

Thanks & Regards

Rajneesh

ans:

The error message is to notify customers that they need to set IOSTANDARD and LOCs in order to protect devices from accidental damage that could be caused by the tools randomly choosing a pin location or IOSTANDARD without knowledge of the board voltage or connections.

For example:

If a pin is tied to ground on a board and ISE Design Suite chooses this pin as an output that is driving high, this causes contention.

If you have a termination scheme on the board for a pin that is the HSTL or SSTL recommended termination and ISE Design Suite chooses LVCMOS18 (default), the signal integrity of the signal will be less than optimal.

The default I/O standard for the 7 Series is LVCMOS18 for single-ended signals for all banks, the default I/O standard was LVCMOS25 in previous architectures.

As the message indicates, the error can be down graded to a warning by using the following constraints

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

These cannot be set in the XDC file. It is recommended to place the command in a script.tcl file and source this Tcl file inside the project or the larger scripting flow.

问题是在写uart的时候遇到的

原因是之前写rx、tx模块的时候,已经写了差分,但是最后写top的时候没有删去,还在top里写了差分,变成好几个差分

解决:删去例化程序里的差分,只在top写差分

也就是说,差分是给接口的,只需要在顶层写就好了

PR时,专用时钟对不够用了,需要将多出来的指定

[Place 30-675]

[Place 30-172] Sub-optimal placement for a clock-capable IO pin and PLL pair. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets i_pl/i_pll/i_mea_lx_pll_wrp/iclk2_ibufg] >

当然是类似这样的error,很疑惑,这对时钟我正常使用,为什么就出现问题了呢?

查看电路图:

如上图,AD1_ADR以及AD1_BDR都是时钟引脚,外部时钟从这个引脚上进入FPGA,之后FPGA设计中使用其中的一对时钟。

可以看出,上面的这两队时钟信号,对应到FPGA的引脚不是时钟专用引脚,而是普通引脚,这就是问题的根源,我们一般在电路图的设计中,总要将时钟接到FPGA的专用时钟引脚上,例如:

上图中的MRCC,以及SRCC,可以供时钟引脚使用。

由此看来,出现这样的原因是电路设计的锅?

但是呢?我们也不能抱怨,问题并不是说我们做FPGA设计的束手无策,这样的设计,也许是无心的,但是有时候也存在这样情况,例如时钟比较多,时钟专用引脚不够,怎么办呢?

只能用普通IO来接时钟,我们如何在FPGA设计中解决这个问题?

其实仔细看人家提示的错误就好了,人家说了,你可以通过加约束解决这个问题:

如:

[Place 30-172] Sub-optimal placement for a clock-capable IO pin and PLL pair. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets i_pl/i_pll/i_mea_lx_pll_wrp/iclk2_ibufg] >

把这条提示加入XDC约束文件里面即可,原理就是绕过PAR的检查,但是没有解决根本问题。

————————————————

版权声明:本文为CSDN博主「李锐博恩」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/Reborn_Lee/article/details/102943738

导出

[vivado 导出硬件出现“ERROR: Common 17-69] Command failed: write_hw_platform is only supported for synthesized, implemented, or checkpoint designs close_design”错误

这个错误表示当前项目不支持导出,如下图所示

IP

##打包IP

在封装自定义IP的时候有可能会出现这两条警告,一条是关于时钟信号,另一条是复位信号

[IP_Flow 19-3157] Bus Interface ‘rst_n’: Bus parameter POLARITY is ACTIVE_LOW but port ‘rst_n’ is not *resetn - please double check the POLARITY setting.

[IP_Flow 19-5661] Bus Interface ‘clk’ does not have any bus interfaces associated with it.

原因分析:

两条警告的解释:

- rst_n信号的优先级是低,但是其没有连接到resetn(原文是 ‘rst_n’ 不是*resetn,这里感觉是没有连接到总线复位信号,见下文)

- clk信号没有任何一个总线接口(AXI)与其相连

这个警告是因为IP核打包器在设计中推断出了时钟端口或是复位端口。例如:如果信号名称包含以下任何一种:[ ]clk,[ ]clkin, [ ]clock[ ], [ ]aclk 或 [ ]aclkin,那么IP打包器就会为将其判断成为时钟接口。被自动判断出的接口,IP打包器会倾向于认为你使用AXI接口来处理这个信号,因为IP打包器工具主要是针对于AXI接口。

所以如果你的IP中并不使用AXI总线,这两条警告可以直接忽略,在实际的IP中不会有任何的影响。

解决方法:Edit Interface–Parameters—Overriden–POLARITY: ACTIVE_LOW??

xcelium打不开ip,protected source code

导出xcelium时选择的Compile library不一样

最好使用绝对路径,导出的run.f也是不一样,选绝对路径,这里就是绝对路径

#HAPs

@E:signal 011 error in m_xilinx的错误!

可能是环境问题,换用了2018.3的vivado,并且把Ooption由fast换成了advance

option set synthesis_strategy advanced

环境和策略问题