内容摘取自<Rockchip_RK3568_Hardware_Design_Guide_V1.0_CN.pdf>

1.1概述

本章对于RK3568产品设计中的ESD/EMI防护设计给出了建议,帮助客户更好的提高产品的抗静电、抗电

磁干扰水平。

1.2 术语解释

本章中的术语解释如下:

ESD(Electro-Static discharge): 静电释放;

EMI(Electromagnetic Interference):电磁干扰,包括传导干扰和辐射干扰两部分;

1.3 ESD 防护

从模具上做隔离,接插件能内缩的尽量内缩于壳体内,让静电释放到内部电路上的距离变长,能量变弱,测试标准由接触放电条件变为空气放电等;

在PCB布局时做好敏感器件的保护,隔离;

布局时尽量将RK3568芯片及核心部件放在PCB中间,不能放在PCB中间的需要保证屏蔽罩离板边至少2MM以上的距离,且要保证屏蔽罩能够可靠接地;

应该按功能模块及信号流向来布局PCB,各个敏感部分相互独立,对容易产生干扰的部分最好能隔离;

要求合理摆放应对ESD器件,一般要求摆在源头,即ESD器件摆放在接口处或静电释放处;

元件布局远离板边且距插接件有一定距离;

PCB表面一定要有良好的GND回路,各接插件在表层都要有较好的GND连接回路。有加屏蔽罩的应尽量跟表层地相连,并在屏蔽罩焊接处多打地孔接地。要做到这一点,就要求各个连接座部分在表层不要走线,也不要出现大范围切断表层铜皮的走线;

表层板边不走线且多打地孔;

必要时要做好信号跟地之间的隔离;

多露铜,以便加强静电释放效果,或者便于增加加泡棉等补救措施

如果有经连接器实现板对板连接时,建议全部信号串接一定阻值的电阻(2.2ohm-10ohm之间,具体以能满足SI测试为准), 以及预留TVS器件,可提升抗静电浪涌能力

RK3568 nPOR管脚的100nF电容必须靠近管脚放置,电容的地焊盘必须有一个0402地过孔,空间允许建议打两个以上,更良好的接地。

关键信号比如Reset,时钟,中断等敏感信号与板边距离不得小于5mm

其它外围芯片如果有带Reset管脚,建议增加100nF电容必须靠近管脚,电容的地焊盘必须有一个0402地过孔,空间允许建议打两个以上,更良好的接地。

整机设计为浮地设备时,建议各接口不要分地设计。

机器外壳为金属时,电源是三孔,要求金属外壳必须良好连接大地

预留屏蔽罩位置,屏蔽罩的应尽量跟表层地相连,并在屏蔽罩焊接处多打地孔接地,要做到这一

点,就要求各个连接座部分在表层不要走线,也不要出现大范围切断表层铜皮的走线

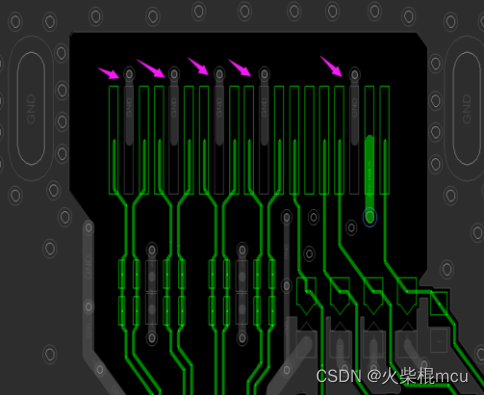

从PCB上进行隔离,让静电只能释放在部分区域,比如座子地管脚单独过孔和内层的地层连接,对表层的PCB进行Keepout,表层的地铜皮和管脚尽量远离,即让敏感信号远离静电易放电区域(表层地铜皮)等等,如图在表层隔离HDMI信号与GND的距离。

1.4 EMI 防护

电磁干扰三要素:干扰源、 耦合通道及敏感设备。我们不能处理敏感设备,所以处理EMI就只能从干扰源跟耦合通道入手了。解决EMI问题,最好的方式就是消除干扰源,消除不了的就想办法切断耦合通道或者避免天线效应;

PCB上干扰源一般很难完全消除,可以通过滤波、 接地、 平衡、 阻抗控制,改善信号质量(如端接)等方法来应对。各种方法一般会综合运用,但良好的接地是最基本的要求;

常用应对EMI材料有屏蔽罩,专用滤波器,电阻,电容,电感,磁珠,共模电感/磁环,吸波材料,展频器件等;

滤波器选择原则:若负载(接收器)为高阻抗(一般的单端信号接口都是高阻抗,比如SDIO,RBG,CIF等),则选择容性滤波器件并入线路;若负载(接收器)为低阻抗(比如电源输出接口),则选择感性滤波器件串入线路。使用滤波器件后不能使信号质量超出其SI许可范围。差分接口一般使用共模电感来抑制EMI;

RK3568展频的能分模块使用。展频的程度需根据相关部分对信号的要求而定。具体措施见RK3568展频说明;

DDR3_CLKP/N, DDR4_CLKP/N, LPDDR3_CLKP/N之间RC的电路,不得删减,可改善EMI

所有时钟串接的匹配电阻,建议保留,提供匹配阻抗,提高信号质量的改善措施;

DC电源输入处,有条件可预留电源共模电感或EMI滤波器;

USB, HDMI, VGA,屏连接座等接口处增加预留共模电感或滤波电路;

有加散热器时,要注意散热器也有可能耦合EMI能量,产生辐射,在选用散热器时除了满足热设计要求,还应满足EMI测试要求。散热器要预留接地条件,当有需要接地时,将散热器接地,此处不好明确接地点个数及怎么选择接地点,需要第一个版本硬件在实验室实际测试时依据实际情况整

改;

EMI跟ESD对LAYOUT的要求有高度一致性,前述ESD的LAYOUT要求,大部分适用于EMI防护。另外增加下面的要求;

尽量保证信号完整性;

差分线要做好等长及紧密耦合,保证差分信号的对称性,以尽量减少差分信号的错位跟时钟,

避免转化成引起EMI问题的共模信号;

有插件器件等带金属壳器件的元件,应避免耦合干扰信号从而辐射。也要避免器件的干扰信

号从壳体耦合到其他信号线;

所有时钟串接的匹配电阻靠近CPU端(源端), CPU管脚和电阻之间走线必须控制在400mil以内;

如果PCB超过4层板,建议让所有时钟信号尽量走内层;

防止电源辐射,电源层覆铜必须内缩,以一个H(电源和地之间的介质厚度)为单位,建议内

缩20H;