牛客网Verilog刷题——VL28

- 题目

- 答案

题目

请编写一个序列检测模块,输入信号端口为data,表示数据有效的指示信号端口为data_valid。当data_valid信号为高时,表示此刻的输入信号data有效,参与序列检测;当data_valid为低时,data无效,抛弃该时刻的输入。当输入序列的有效信号满足0110时,拉高序列匹配信号match。

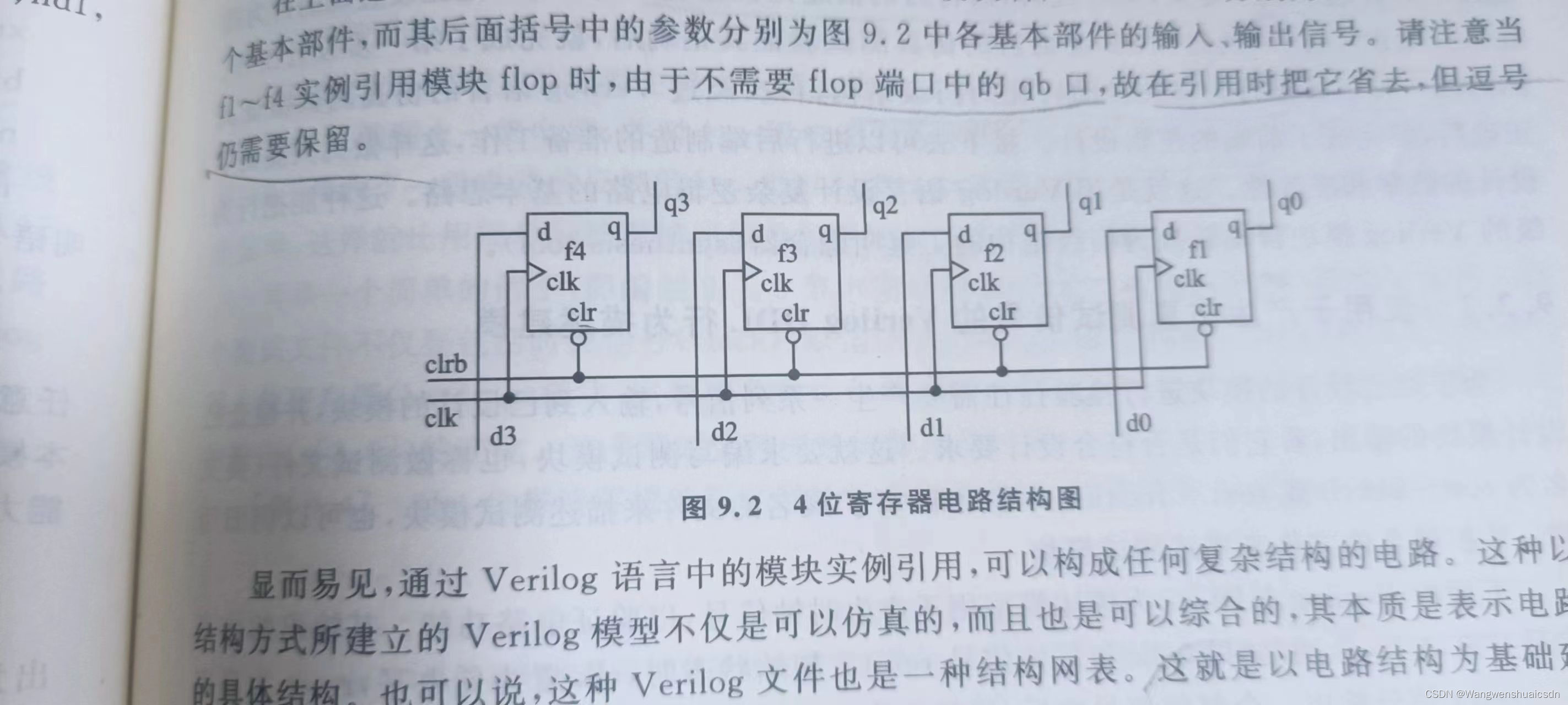

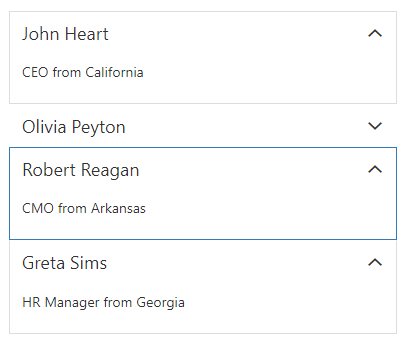

模块的接口信号图如下:

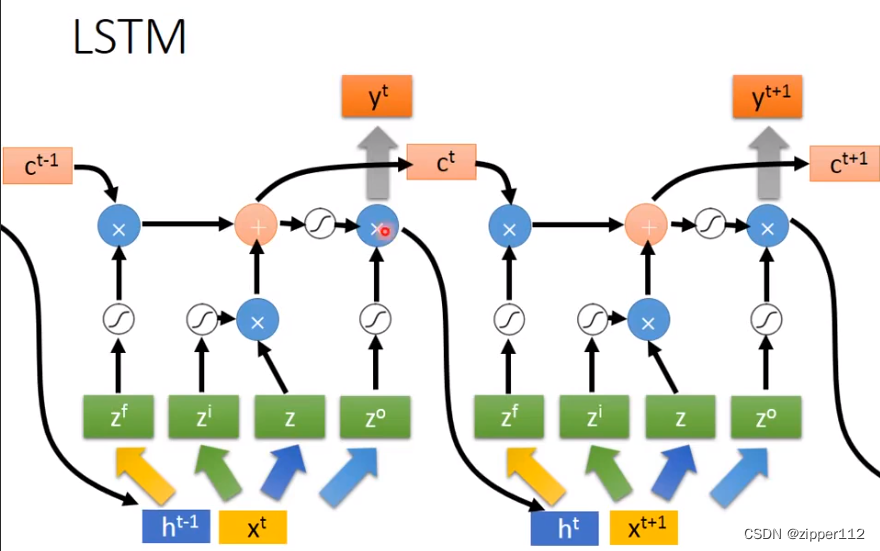

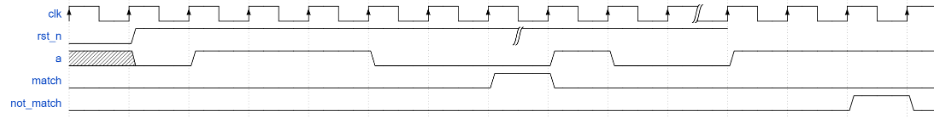

模块的时序图如下:

请使用状态机实现以上功能,画出状态转移图并使用Verilog HDL编写代码实现以上功能,并编写testbench验证模块的功能。

| 信号 | 类型 | 输入/输出 | 位宽 | 描述 |

|---|---|---|---|---|

| clk | wire | Intput | 1 | 系统时钟信号 |

| rst_n | wire | Intput | 1 | 异步复位信号,低电平有效 |

| data | wire | Intput | 1 | 单比特信号,待检测的数据 |

| data_valid | wire | Intput | 1 | 输入信号有效标志,当该信号为1时,表示输入信号有效 |

| match | reg | Output | 1 | 当输入信号data满足目标序列,该信号为1,其余时刻该信号为0 |

答案

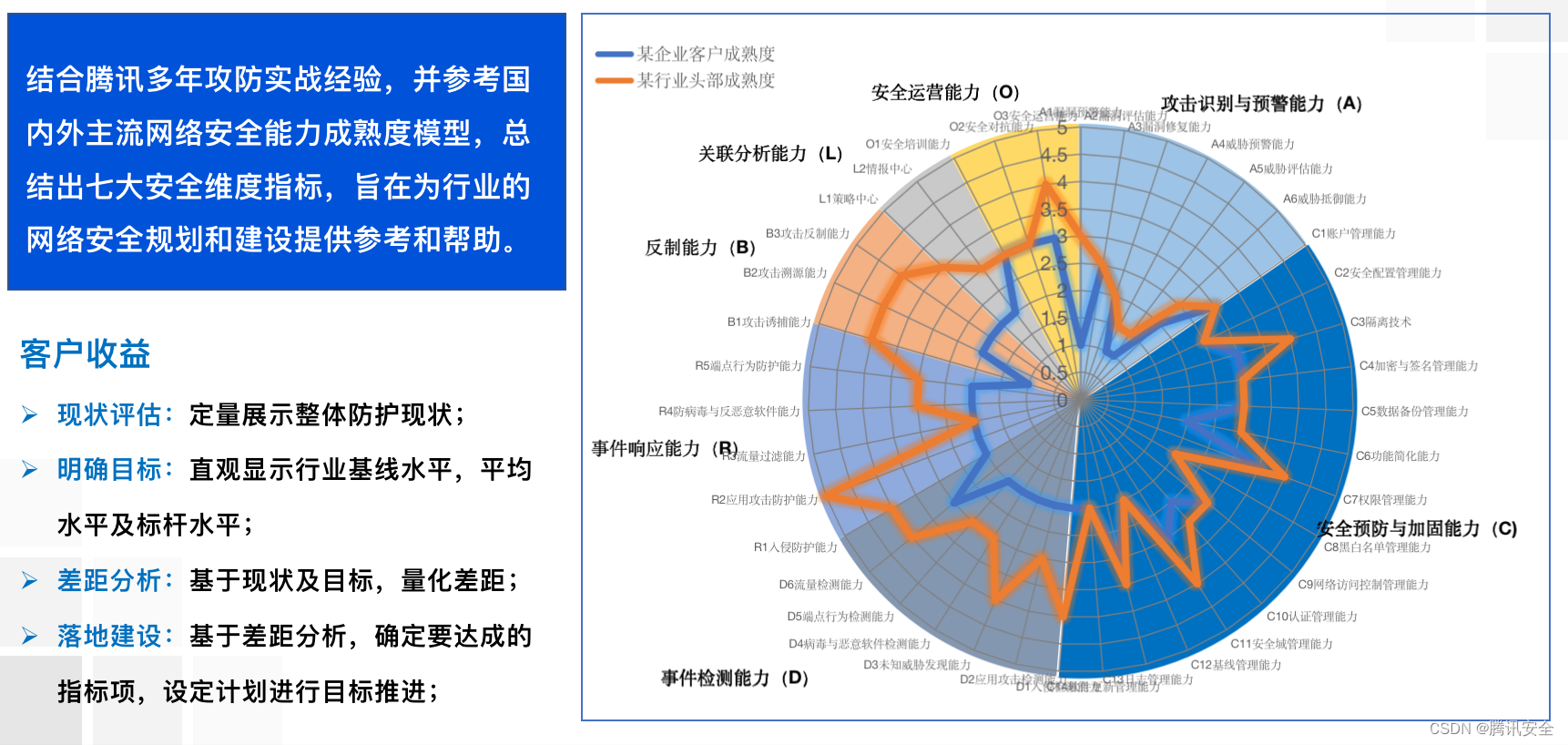

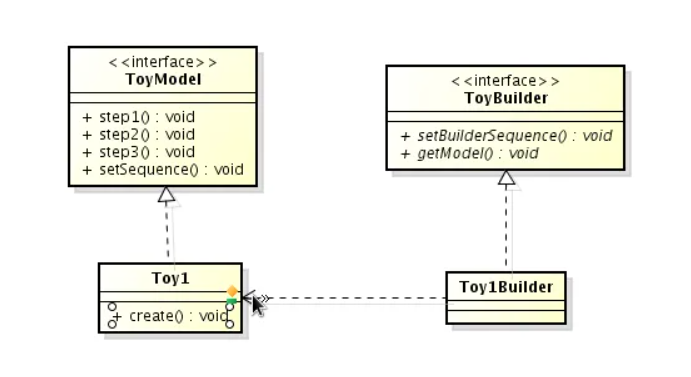

题目中要求使用状态机实现,可以画出其状态转换图,,如下。

根据状态转换图,编写Verilog代码,如下。

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

input data_valid,

output reg match

);

//采用状态机实现

localparam IDLE = 3'd0,

S0 = 3'd1,

S1 = 3'd2,

S2 = 3'd3;

reg [2:0] curr_state;

reg [2:0] next_state;

//-------三段式状态机--------

//第一段

always @(posedge clk or negedge rst_n)

if(!rst_n)

curr_state <= IDLE;

else

curr_state <= next_state;

//第二段

always @(*) begin

next_state = IDLE;

case(curr_state)

IDLE: next_state = (data_valid && (~data)) ? S0 : IDLE;

S0 : next_state = (data_valid && data) ? S1 : S0;

S1 : next_state = (data_valid && data) ? S2 : S1;

S2 : next_state = IDLE;

default: next_state = IDLE;

endcase

end

//第三段

always @(posedge clk or negedge rst_n)

if(!rst_n)

match <= 1'b0;

else if(curr_state == S2 && data == 0)

match <= 1'b1;

else

match <= 1'b0;

endmodule

另外,我们还可以用移位寄存器的方式进行实现,如下。

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

input data_valid,

output reg match

);

//采用移位寄存器实现

reg [3:0] r_data;

always @(posedge clk or negedge rst_n)

if(!rst_n)

r_data <= 8'b0000_0000;

else if(data_valid)

r_data <= {r_data,data};

else

r_data <= r_data;

always @(posedge clk or negedge rst_n)

if(!rst_n)

match <= 1'b0;

else if(r_data[2:0] == 3'b011 && data == 0)

match <= 1'b1;

else

match <= 1'b0;

endmodule