Moudule

概念介绍

到目前为止,你已经熟悉了一个模块,它是一个通过输入和输出端口与其外部交互的电路。更大、更复杂的电路是通过将较小的模块和其他连接在一起的部分(例如赋值语句和always块)组合而成的更大模块来构建的。因为模块可以包含其他模块的实例,由此形成了一个层级结构。

By now, you’re familiar with a module, which is a circuit that interacts with its outside through input and output ports. Larger, more complex circuits are built by composing bigger modules out of smaller modules and other pieces (such as assign statements and always blocks) connected together. This forms a hierarchy, as modules can contain instances of other modules.

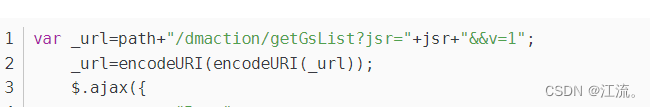

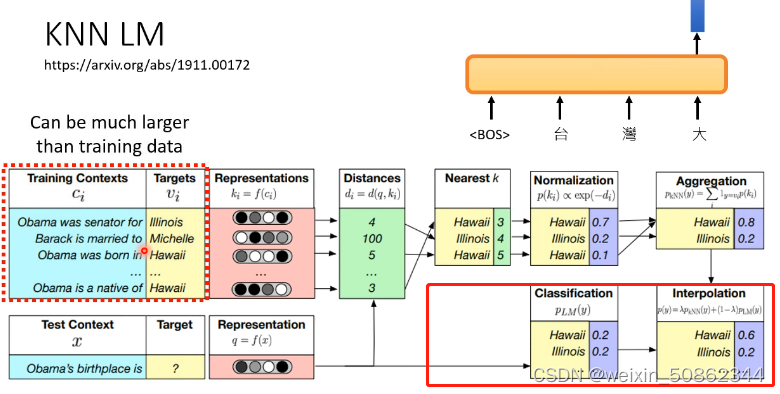

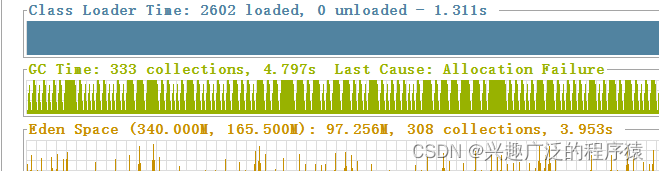

下面这张图展示了一个非常简单的电路及其子模块。在这个练习中,创建一个实例模块mod_a,然后这个模块的三个引脚(in1,in2,和out)连接到你的顶层模块的三个端口(a,b,和out)。这个模块mod_a是给定给你的——你必须实例化它。

The figure below shows a very simple circuit with a sub-module. In this exercise, create one instance of module

mod_a, then connect the module’s three pins (in1,in2, andout) to your top-level module’s three ports (wiresa,b, andout). The modulemod_ais provided for you — you must instantiate it.

在连接这些模块时,只有在模块上的端口才是重要的。你不需要知道模块内部的代码(结构)。模块mod_a看上去像这样:

When connecting modules, only the ports on the module are important. You do not need to know the code inside the module. The code for module

mod_alooks like this:

module mod_a ( input in1, input in2, output out );

// Module body

endmodule

![![[Pasted image 20230411225523.png]]](https://img-blog.csdnimg.cn/3c83001620094fed9e3525d68a42e6fd.png)

模块的层级结构是由下面这样构成的,在一个模块中实例化其它模块,只要所有的模块都隶属于同一个工程(这样编译器能够知道从哪里找到这些模块)。一个模块的代码并不会被写到其它模块的主体里面去。(不同模块的代码是不嵌套的)

The hierarchy of modules is created by instantiating one module inside another, as long as all of the modules used belong to the same project (so the compiler knows where to find the module). The code for one module is not written inside another module’s body (Code for different modules are not nested).

你可能需要将信号通过端口名或者端口位置来连接。作为额外的练习,两种方法都尝试下。

You may connect signals to the module by port name or port position. For extra practice, try both methods.

方法

连接信号到模块端口

有两种常采用的方法将wire 连接到端口:位置连接法和名字连接法

There are two commonly-used methods to connect a wire to a port: by position or by name.

位置连接法

通过位置去将wire 连接到端口的语法通常是更常见的,因为它使用了一个类C语法。在例化一个模块时,端口根据模块的声明从左到右依次被连接。例如:

The syntax to connect wires to ports by position should be familiar, as it uses a C-like syntax. When instantiating a module, ports are connected left to right according to the module’s declaration. For example:

mod_a instance1 ( wa, wb, wc);

上面这段verilog代码例化了一个mod_a模块并且给它了一个模块名字“instance1”,然后连接信号wa(在这个新模块之外)和这个新模块的第一个端口(in1),连接信号wb和这个新模块的第二个端口(in2) ,连接信号wc和这个新模块的第三个端口(in3)。 这个语法的一个缺点就是如果这个模块端口的排序改变了,所有的例化模块都需要找到并且改变到匹配这个新模块的顺序。

This instantiates a module of type

mod_aand gives it an instance name of “instance1”, then connects signalwa(outside the new module) to the first port (in1) of the new module,wbto the second port (in2), andwcto the third port (out). One drawback of this syntax is that if the module’s port list changes, all instantiations of the module will also need to be found and changed to match the new module.

名字连接法

即使端口顺序改变了,通过姓名连接信号和端口仍然让wires保持正确的连接性。但是,这个语法更加冗长。

Connecting signals to a module’s ports by name allows wires to remain correctly connected even if the port list changes. This syntax is more verbose, however.

mod_a instance2 ( .out(wc), .in1(wa), .in2(wb));

上面的verilog代码将mod_a模块例化成了“instance2”, 然后将信号wa连接到端口in1,wb连接到端口in2,wc连接到端口out。注意端口顺序是不相关的,因为连接根据对应的名称来生成的,无关它在子模块端口列表中的位置。还要注意在语法里面端口名前面的点!

The above line instantiates a module of type

mod_anamed “instance2”, then connects signalwa(outside the module) to the port namedin1,wbto the port namedin2, andwcto the port namedout. Notice how the ordering of ports is irrelevant here because the connection will be made to the correct name, regardless of its position in the sub-module’s port list. Also notice the period immediately preceding the port name in this syntax.

模块代码示例

module top_module (

input a,

input b,

output out

);

// Create an instance of "mod_a" named "inst1", and connect ports by name:

mod_a inst1 (

.in1(a), // Port"in1"connects to wire "a"

.in2(b), // Port "in2" connects to wire "b"

.out(out) // Port "out" connects to wire "out"

// (Note: mod_a's port "out" is not related to top_module's wire "out".

// It is simply coincidence that they have the same name)

);

/*

// Create an instance of "mod_a" named "inst2", and connect ports by position:

mod_a inst2 ( a, b, out ); // The three wires are connected to ports in1, in2, and out, respectively.

*/

endmodule

总结

- 两种方法尽量用名字连接法,防止被例化的模块改了端口顺序

- 第二种例化方法不要忘记每个端口前的

. - 模块例化也是一条一句,也要以分号

;结尾