3.1

板卡技术要求

3.1.1

主要性能指标

本着向下兼容的原则,以太网交换板的设计尽量保留传统信息处理平台的基本功

能和接口,重点考虑提升设备的性能和扩展性。本课题以太网交换板的主要性能指标

如下:

(

1

) 具有大容量无阻塞的交换功能;交换容量不小于

16Gbps

;

(2) 支持千兆光以太网接口和电以太网接口;

(3) 单节点实时业务无丢包,平均转发时延

≤

1ms

。

3.1.2

主要物理接口

按照

VPX

标准要求,结合实际应用需求,以太网交换板的主要物理接口如下:

(

1

) 提供

20

个

Serdes

接口,接口连接到背板连接器,通过背板分别为数据平

面和控制平面提供数据交换。

(2) 提供

4

个

1000 BASE-T

接口和

4

个

1000 BASE-X

接口,接口连接到背板

连接器,通过背板转接板到设备前面板,为设备提供数据接入或交换扩展。

(3) 提供一组串行点灯信号,接口连接到背板连接器,指示前面板数据接口的

状态。

(4) 提供

1

个

RS232

管理串口和

1

个

1000 BASE-T

管理网口,同时连接到本

板和背板连接器,本板端口形式为通用

RJ45

接口;背板侧通过背板到前

面板,便于整机的调试。

(5) 提供板卡

+3.3V

、

+12V DC

电源输入接口,接口连接背板连接器。

3.2

方案设计

3.2.1

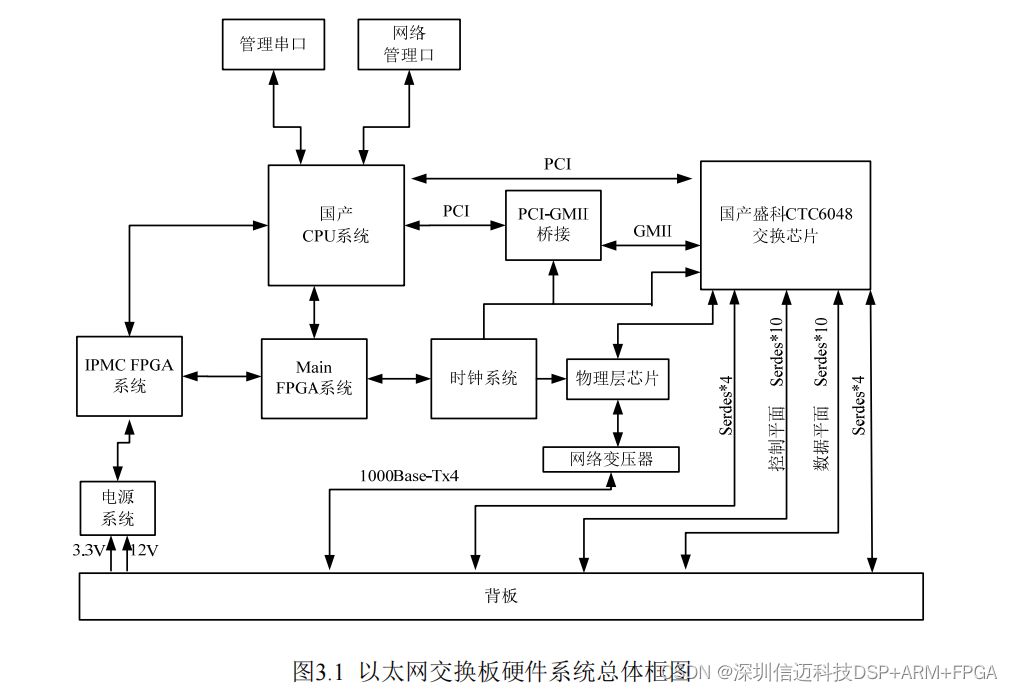

硬件系统原理框图

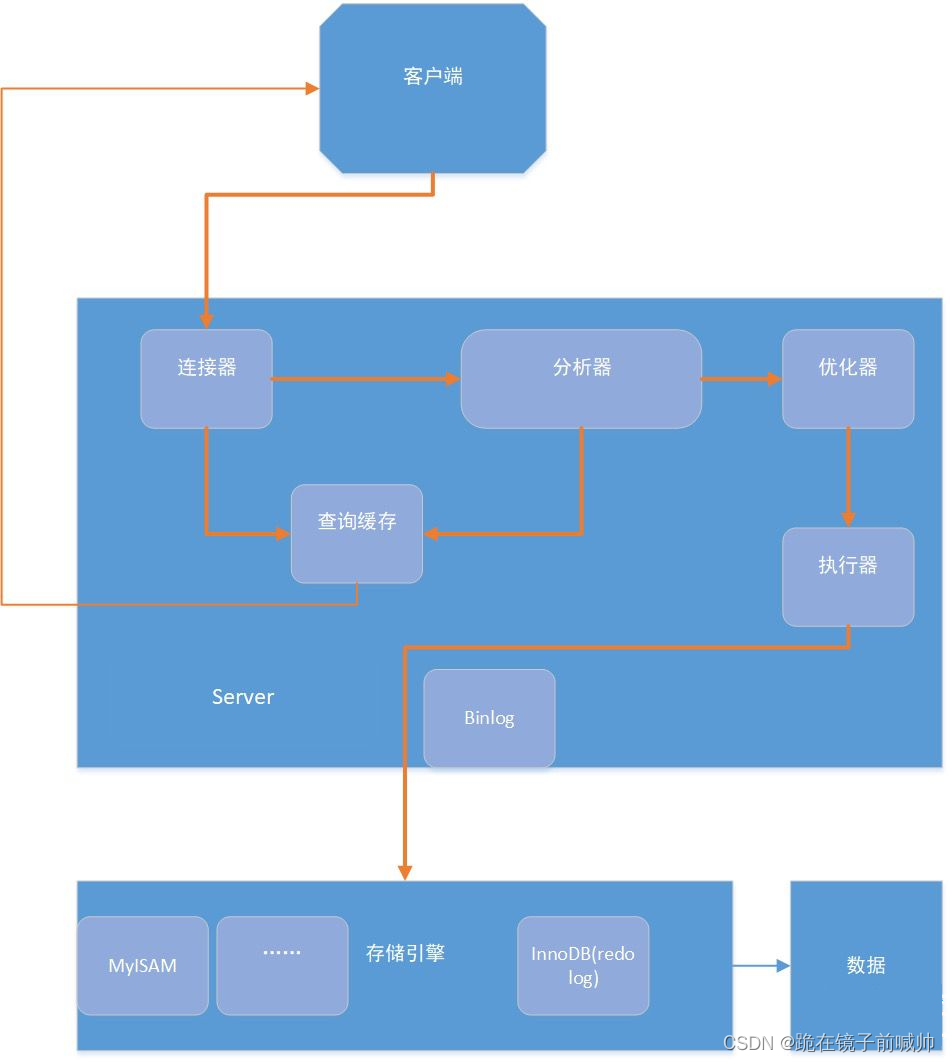

以太网交换板是信息处理平台的核心,主要包括中心控制和核心交换两个功能模

块。中心控制模块主要完成整机维护、控制、协议处理等功能,交换模块完成业务数

据和控制信息的交换功能。从硬件系统上,以太网交换板主要由

CPU

系统、

CTC6048

交换系统、时钟电源系统、

FPGA

处理系统等几个部分组成。硬件系统总体框图如图

3.1

所示。

盛科交换芯片提供

24

对

Serdes

到

RT2

连接器,其中

4

对接光模块直接输出到前

面板,剩余

20

对通过背板输出到各业务槽位,分别作为数据平面和控制平面的交换

总线。交换芯片还提供

4

对

SGMII

串行总线,通过外挂千兆以太网

PHY

芯片输出

4

个

10/100/1000 Base-T

接口到前面板。从控制平面和数据平面接收的数据进入以太网

交换芯片

CTC6048

,由其完成以太网帧同步、

FCS

校验、分组缓存以及关键字提取

之后,根据特定字段区分出以太网帧的类型,对于业务信息则由

CTC6048

内部专用

的网络转发处理引擎进行业务信息分类、网络交换查表、网络交换决策、分组封装、

输出调度等处理过程,对于协议和控制信息则通过控制通道发送到

CPU

系统进行处

理。

CPU

系统采用龙芯

2F

作为处理器,然后通过

PCI

及

LocalBus

扩展出板卡需要

的管理网口、管理串口等接口,实现对整个模块的管理控制。

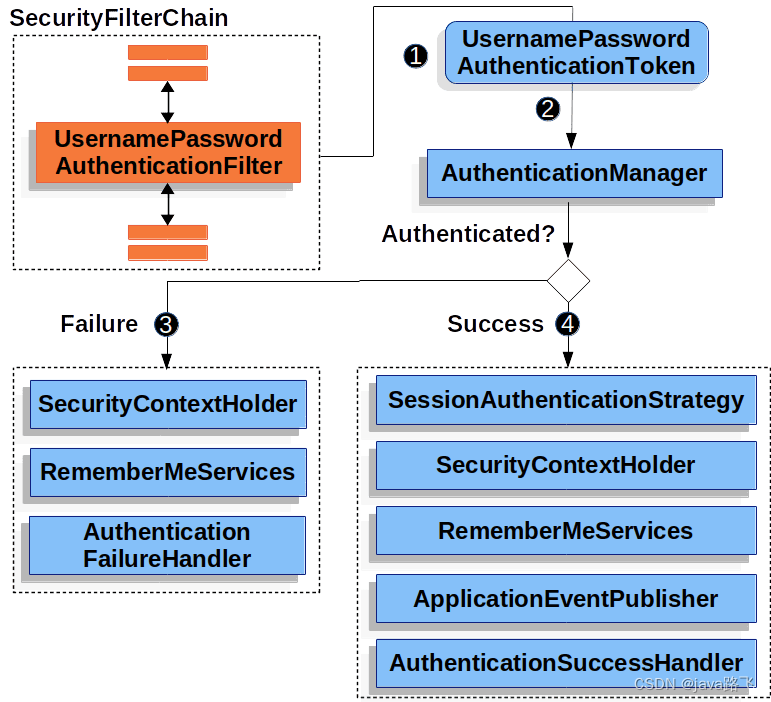

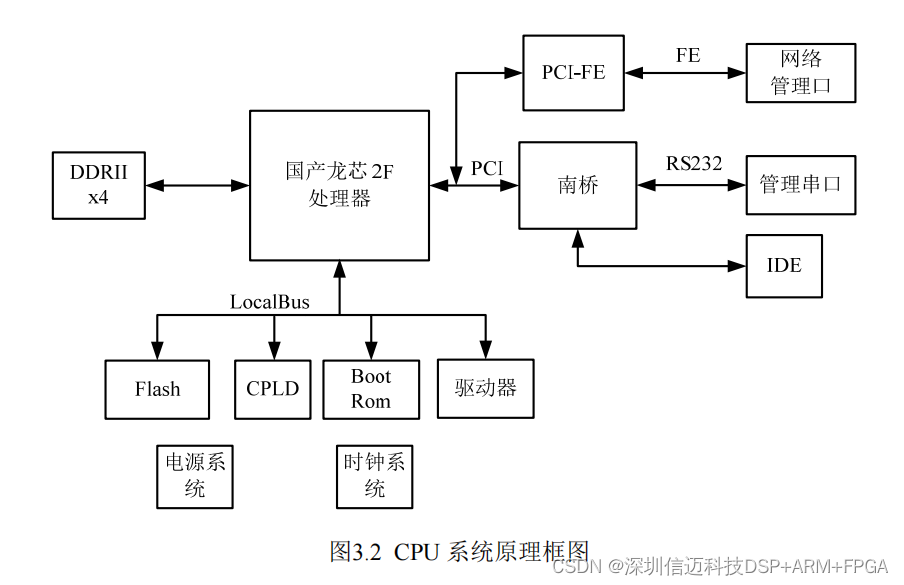

3.2.2

CPU

系统

CPU

系统完成以太网交换板的控制与协议处理,其原理框图如图

3.2

所示,以龙

芯

2F

处理器为核心,同时配以

BIOS

程序存储器、

DDR2 SDRAM

存储器、南桥控制

器、复位及控制逻辑、以太网控制器等,并通过

PCI

及

LoclBus

扩展出系统所需要的

管理串口、管理网口等其他接口用于系统调试和加载程序。时钟模块提供各个芯片正

常工作所需的各种时钟,包括系统时钟(

SYSCLK

)、存储器时钟(

MEMCLK

)、PCI

接口时钟(

PCICLK

)以及为南桥控制器提供

66MHz

、

48MHz

、

14.318MHz

、

32KHz

四种参考时钟。电源变换模块同时提供各个芯片正常工作所需的各种电源。

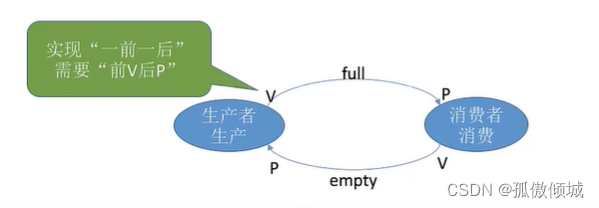

3.2.3

CTC6048

交换系统

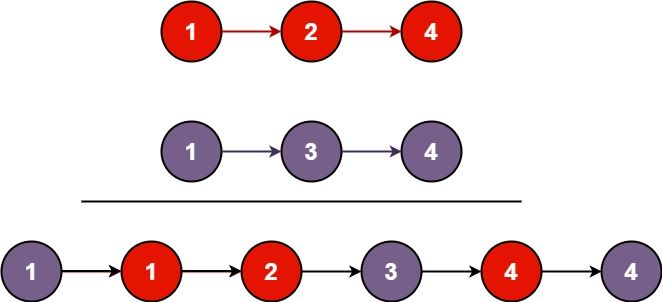

图

3.3

是

CTC6048

以太网数据收发数据流向图。

1

片千兆以太网

PHY

与

CTC6048

间通过

4

个

SGMII

相连,引出

4

个

GE

接口到背板连接器,通过背板及前面板转接

板到整机前面板;

CTC6048

还直接出

28

对

Serdes

总线,其中

4

对到背板

P2

连接器,

通过背板到前面板转接板上的光模块,经光模块输出到整机前面板;

10

对到背板

P2

连接器、

10

对到背板

P3/P4/P5

连接器,再通过背板到各业务槽位,作为各业务板信

息交互的控制通道和数据通道;最后

4

对

Serdes

总线到背板

P6

连接器,作为备用总

线,当整机为了提高可靠性要求主备切换时,可以作为主备以太网交换板信息交互的

通道。

另外,

CTC6048

通过

PCI-GMII

桥接模块实现与

CPU

的通信,用来作为

CPU

与

CTC6048

间数据报文的收发。

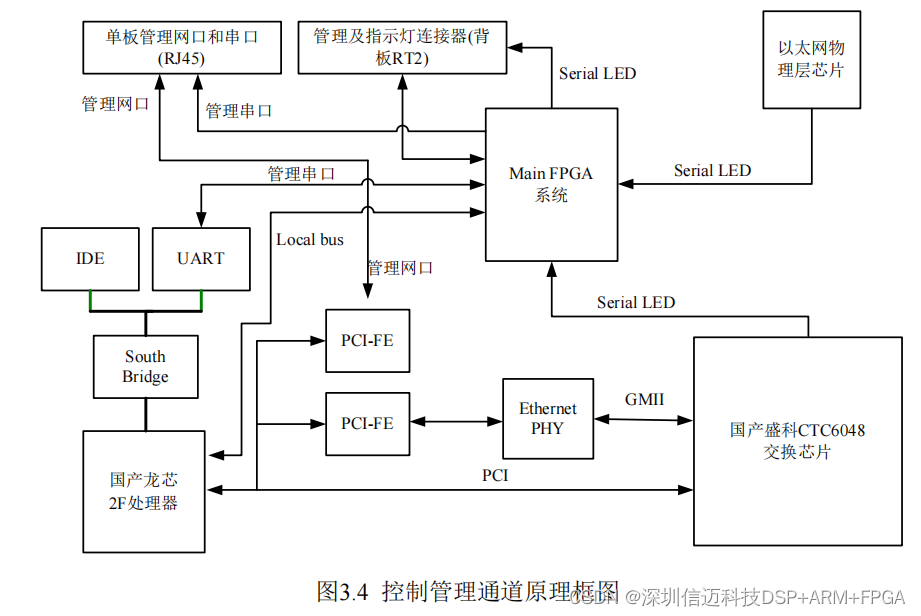

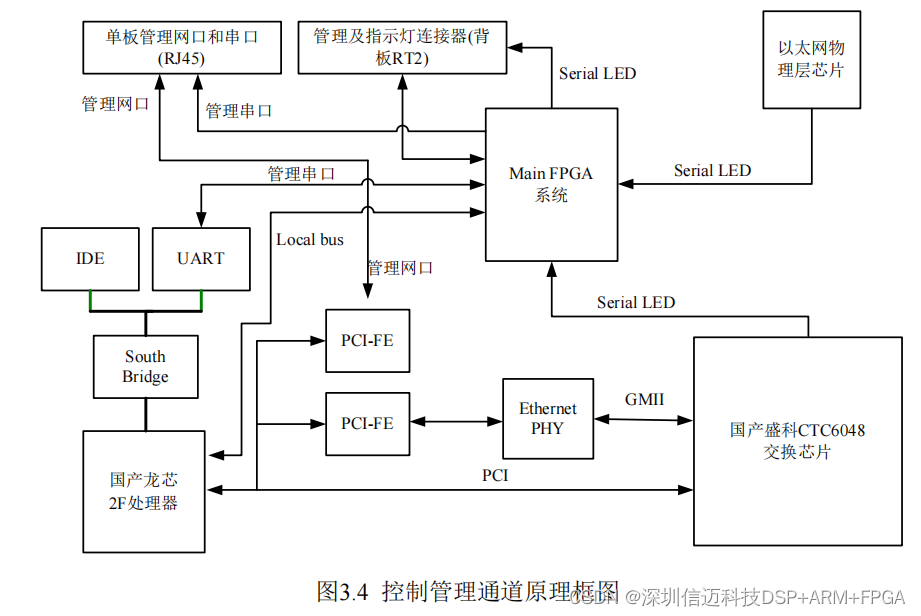

3.2.4

控制和管理通道

控制和管理通道的原理图如图

3.4

所示,在控制通道中,处理器通过

33MHz PCI

通道控制和管理

CTC6048

;处理器还通过

PCI-FE

桥接芯片,扩展出一个管理网口;

通过总线桥芯片扩展出一个管理串口,然后进入

FPGA

,在

FPGA

内完成串口切换。

管理网口和串口既连接到本板

RJ45

连接器,又连接到背板连接器,通过背板输出到

前面板航插连接器,这种连接方式既可利于单板的调试,也便于用户在电路板进入密

闭机箱后对整个系统进行管理和配置。

CTC6048

对需要上报给

CPU

处理的数据以

GMII

接口送出,但龙芯处理器并不

提供

GMII

接口,无法直接对接,间接互联的办法如下:

CTC6048

的

GMII

接口通过

Ethernet PHY

芯片扩展出一个千兆以太网口,龙芯处理器通过

PCI-FE

桥接芯片扩展

槽一个千兆以太网口,两个以太网之间直接对接,从而实现了协议数据的上报。

CTC6048

和

Ethernet PHY

均提供串行指示灯(

Serial LED

)接口,通过在

FPGA

内进行汇接,提取需要在前面板显示的端口的状态,然后封装成帧,以

Serial LED

接

口送到背板连接器,最后通过背板到面板指示灯模块。

FPGA

系统还用来为各芯片提

供复位、时钟、端口计数等功能,

CPU

通过

Local Bus

对其内部寄存器进行访问。

以太网交换板方案实现

4.1

国产芯片的特点

上一章论述了以太网交换板的设计方案,本章首先介绍国产芯片的特点,然后对

方案的具体实现进行详细论述。

国产芯片主要有以下特点:

(

1

) 接口集成度较低

龙芯处理器对外接口仅包括基本的数据地址总线、

DDR

接口、

PCI

总线,无其

他通信接口,对于常见的以太网等通信接口需要通过外围芯片进行扩展;交换芯片的

CPU MAC

接口对外提供

PCI

和

GMII

接口,分别用于管理数据和业务数据的传输,

不仅造成

IO

数量多,而且与龙芯片处理器互连时需要单独的桥接芯片,而博通公司

的同类产品早在几年前已普及

PCIE

高速串行总线进行数据传输,且不区分管理数据

和业务数据,大大简化了

IO

数量和接口设计。

(2) 芯片面积及功耗较大

受当前生产工艺及成本等多方面的影响,本设计选用的龙芯

2F

处理器采用

90nm

工艺,单芯片典型功耗

3W

,交换芯片和

FPGA

及配套存储器采用

65nm

工艺,其中

交换芯片内核电流超过

20A

,

FPGA

配套的可编程存储器封装

18mmx18mm

,封装尺

寸远超过

Altera

公司相同容量的存储器件。

(3) 可参考资料少

基于设计人员的开发习惯等因素,设计人员更倾向于选取成熟的国外芯片,导致

国产芯片的应用领域受限,如龙芯最主要的应用领域还集中在政府、教育等对性能要

求不高的领域,国产

FPGA

也集中应用在某些专用领域,可参考的资料比较少,对开

发过程中出现的问题无法提供技术参考。

(4) 价格稍高

国产芯片出货量少导致其成本较高,进一步导致用户数量少,形成恶性循环。随

着国家自主可控战略的实施,这些情况正在逐渐改善。

国产芯片的上述特点给本设计带来较大的开发难度。如龙芯处理器和交换芯片的

之间的数据通道需要通过桥接芯片进行转换后才能实现互连,增加了芯片数量和功

耗,加之国产化芯片的尺寸也较大,而

VPX 6U

板卡外围尺寸仅为

233.35mm*160mm

,

祛除加固罩、连接器等占用的空间,实际有效布局布线面积为

209mm*137mm

,给

PCB

的布局布线带来较大的困难。为了解决这一问题,设计采用板卡叠加的形式,

并统筹考虑各模块的功能与散热情况,将以太网交换板分为三个子板:即

CPU 子板、

电源子板、交换系统母板。本人承担电源子板和交换系统母板的全部硬件设计及

FPGA

设计工作。下面将简要介绍

CPU

子板,详细论述电源子板及交换系统母板的

实现。

4.2

CPU

子板

CPU

子板按照

ETX

标准进行设计,外形尺寸为

114mm*95mm

,采用

4

个

80

针,

针间距为

0.8mm

的高速连接器实现板间互联。

CPU

子板在标准

ETX

信号定义上进行

了部分修改,板间连接器的接口信号包括

PCI

接口信号、

USB

总线信号、

IDE

信号、

COM

信号、复位信号,以及通用处理器并行总线

LOCAL

总线信号。

CPU

通过上述

信号与交换系统母版各功能模块通信,相互协作完成系统要求的功能。

4.3

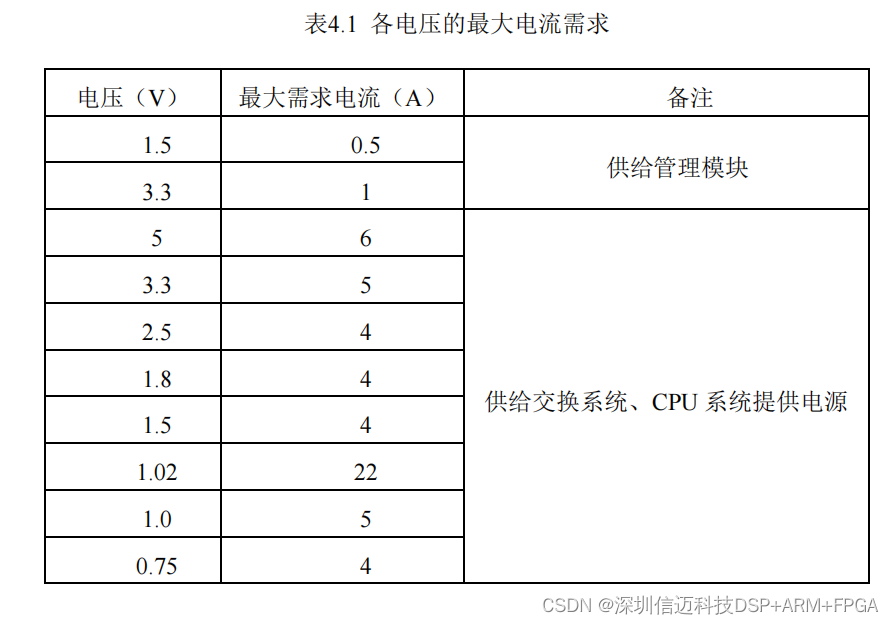

电源子板

4.3.1

芯片选型

根据上一章节系统电源方案设计可以看出,以太网交换板需要的电源种类较多,

在电源芯片选型时重点考虑以下几点:

(

1

) 供应商、生命周期。

芯片的生命周期和供货周期会给生产带来较大影响。芯片一旦停产,可能需要重

新寻到替代产品,甚至需要重新设计。

(2) 输出额定电流。

根据芯片的功耗(可以查数据手册)来预估该芯片对某种电压的电流需求,然后

利用这些数据来指导电源芯片的选型,重点关注电源芯片在高温下的降额指标。

(3) 转换效率

转换效率高,可以降低芯片工作时产生的热量,提高板卡在恶劣环境下的可靠性。

(4) 封装及外围器件数量

封装小,外围器件数量尽量少,可以节省印制板空间,降低设计复杂度,提高系

统的可靠性。

(5) 芯片种类

在满足上述条件的前提下,尽量减少芯片种类,便于器件的维护和采购。

4.3.2

方案实现

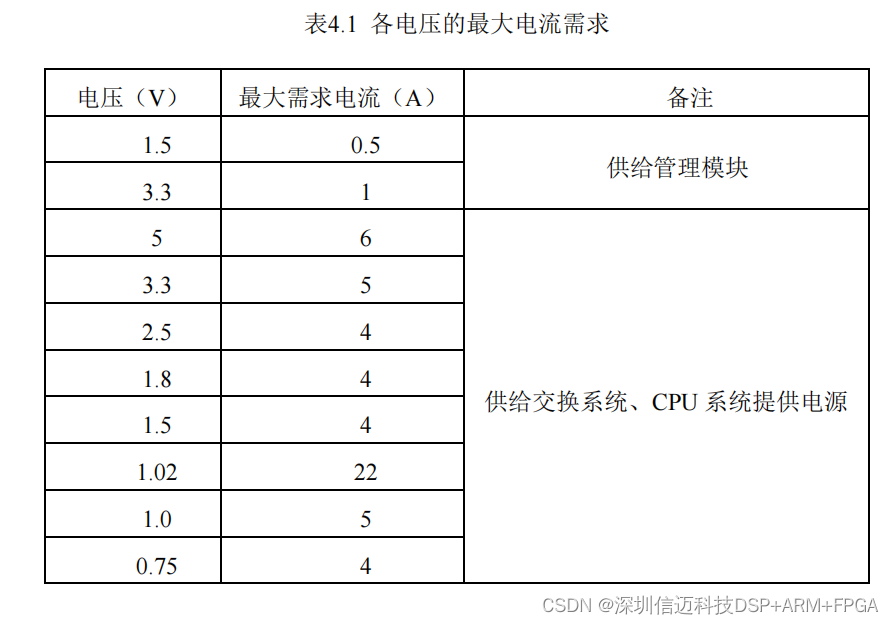

各电压对电流的需求如下表所示。