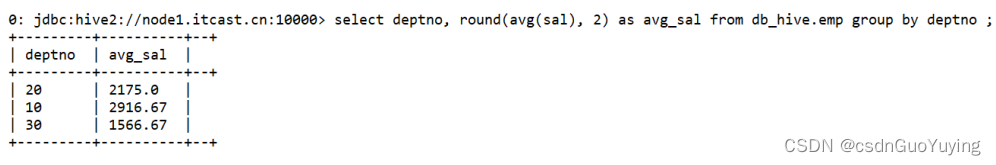

计算机的基本组成

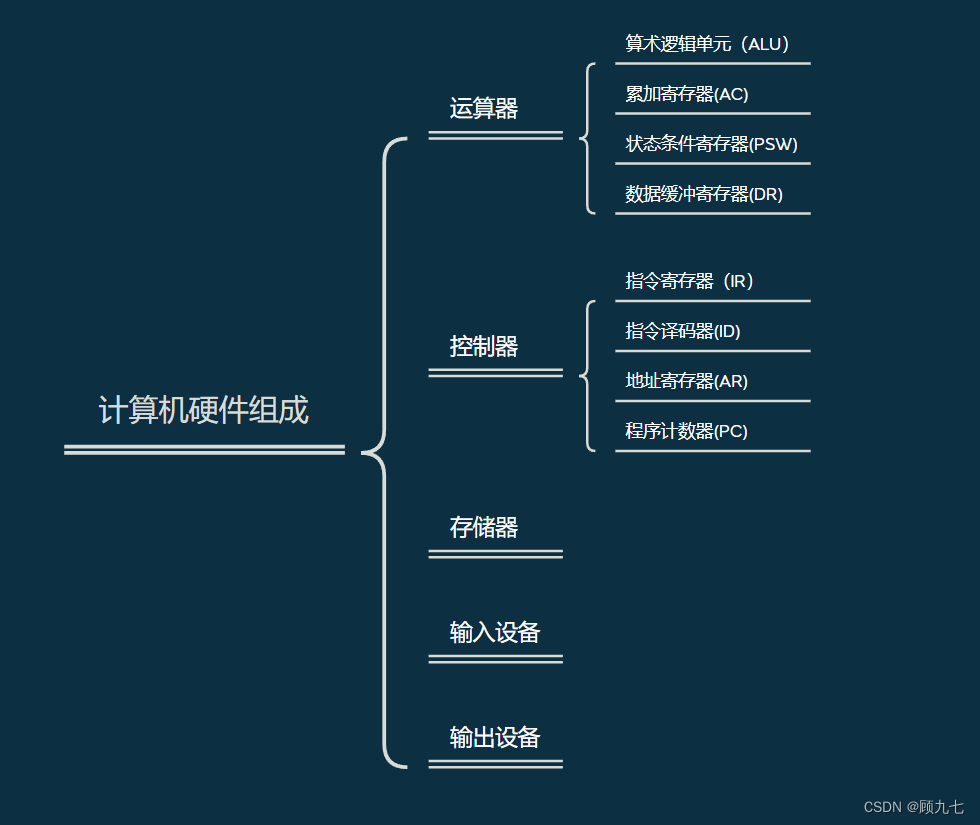

计算机组成逻辑图

计算机部件作用

一级部件作用

- 运算器:计算机的执行部件,受控制器控制,执行算术运算或逻辑运算

- 控制器:决定计算机运行过程的自动化。不仅能保证程序指令的正确执行,还能处理异常事件。

- 存储器:记忆设备,分为内存和外存

- 输入设备、输出设备:称为外设

二级部件作用

-

算术逻辑单元(ALU):执行算术运算或逻辑运算,包含加减乘除、与或非

-

累加寄存器(AC):当算术逻辑单元执行算术或逻辑运算时,为ALU提供工作区。提供运算数据或暂存运算结果。

-

状态条件寄存器(PSW):保存算术指令和逻辑指令运算或测试的各种结果状态码。如:运算结果进位标志、运算结果为0标志等

-

数据缓冲寄存器(DR):数据、指令在cpu、内存和外设之间的中转站、缓冲区。对内存执行读写操作时,保存一条指令或一个数据字

-

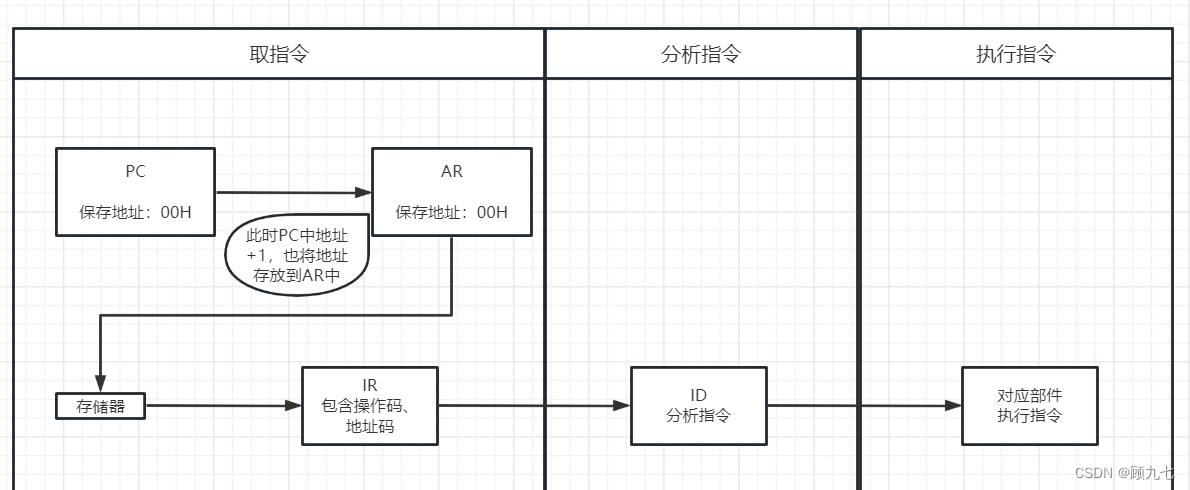

指令寄存器(IR):cpu执行指令时,从内存中取出放在缓冲寄存器中,然后放入指令寄存器暂存,指令译码器根据其中的内容生成指令,控制其他部件工作。不可被访问到

-

指令译码器(ID):指令由操作码和地址码组成。指令译码器对操作码进行分析,生成对应指令,控制其它部件工作

-

地址寄存器(AR):执行指令时,因内存和cpu执行速度差异,需保存地址信息,直到指令完成

-

程序计数器(PC):具有寄存信息和计数两个功能。执行方式分为顺序执行和转移执行。程序执行时,将指令的地址保存在PC中,直到加载到内存时,才能确定,因此pc的内容是第一条指令的地址,执行过程中,cpu修改pc的内容以保证pc内保存的是执行的指令的地址,此为顺序执行。转移执行,是cpu直接将转移指令给出的转移地址修改进去,或者根据位移量进行修改

CPU

CPU组成

CPU作用

- 程序控制

- 时间控制

- 操作控制:CPU产生每条指令的操作信号并将操作信号传给相应的操作部件,控制相应部件根据指令的要求进行操作。

- 数据处理

计算机的基本单位与进制

计算机的基本单位(空间大小由小到大)

- 位 b bit

- 字节 B Byte 1B = 8b

- 千字节 KB 1KB = 1024B

- 兆字节 MB 1MB = 1024KB

- 吉字节 GB 1GB = 1024MB

- 太字节 TB 1TB = 1024GB

最小的数据单位:b

最小的存储单位:B

进制与进制转换

进制表示

- 二进制(B)数值由0和1组成,逢二进一

- 八进制(O)数值由0到7组成,逢八进一

- 十进制(D)平常使用的表示方式。数值由0到9组成,逢十进一

- 十六进制(H)数值由0~9和A/B/C/D/E/F表示,字母分别表示10/11/12/13/14/15,逢十六进一

进制转化

十进制转R进制

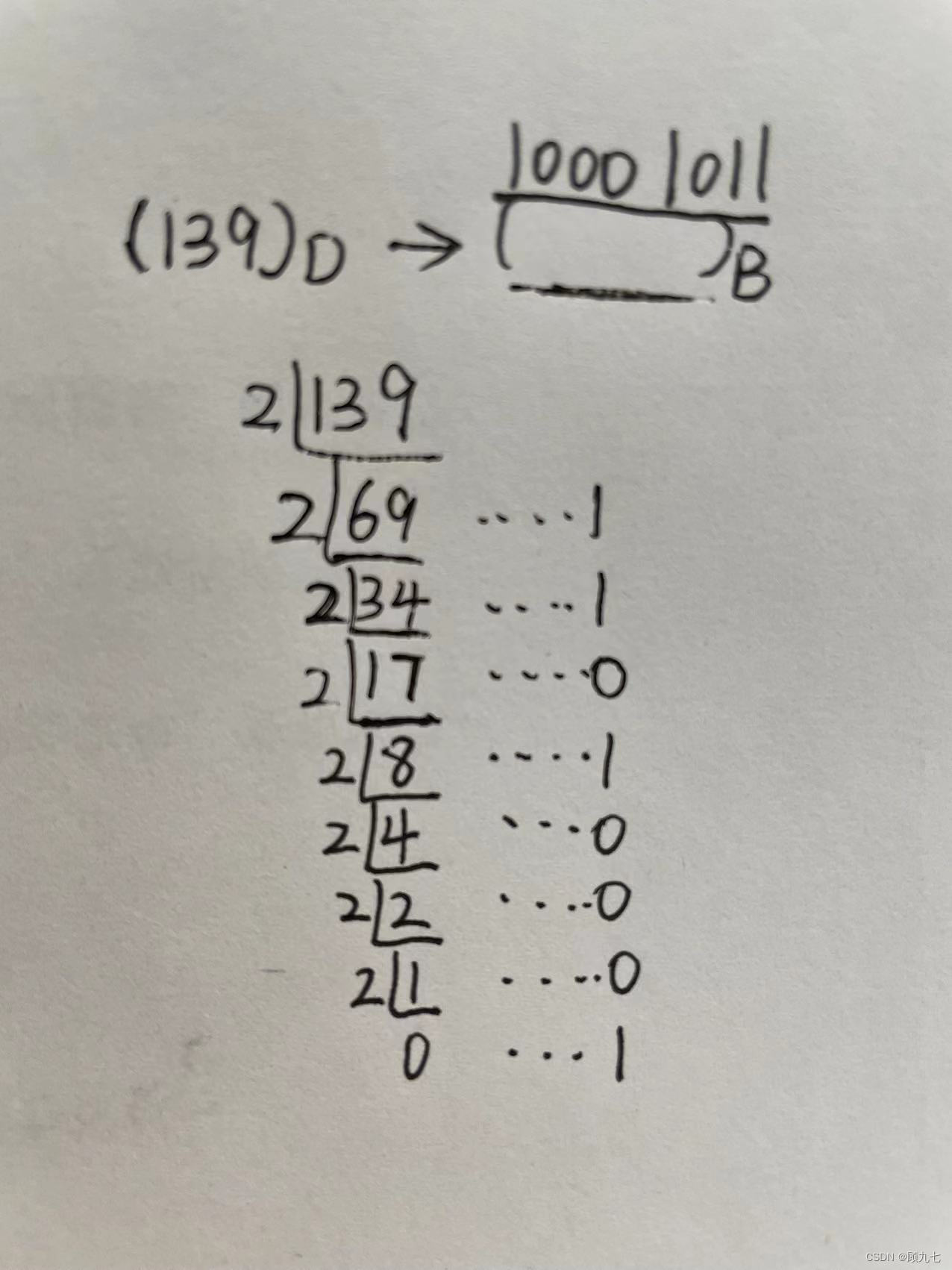

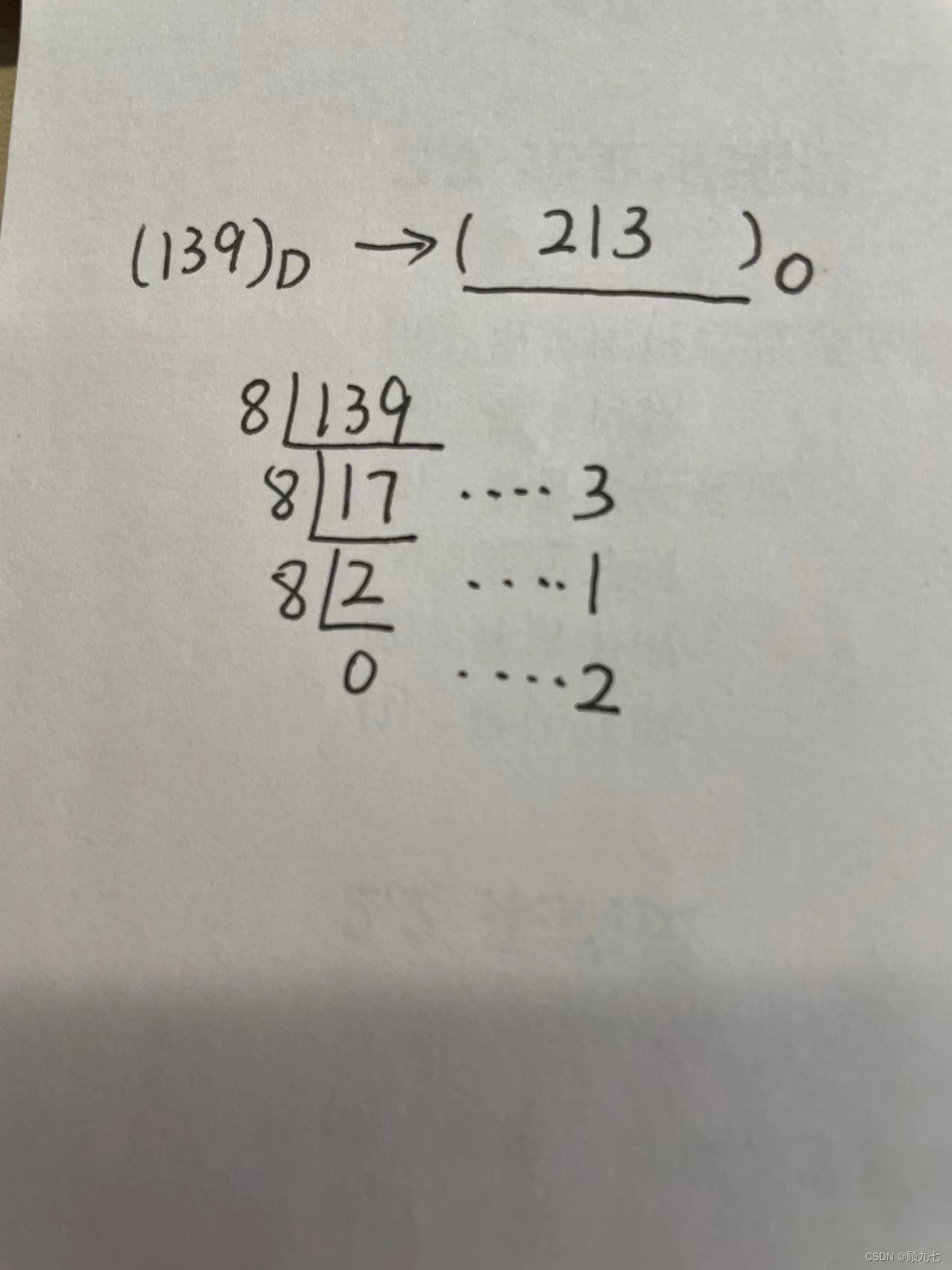

除R取余法

D数做被除数,R做除数。一直除,直到商为0,将余数由下向上取出排列

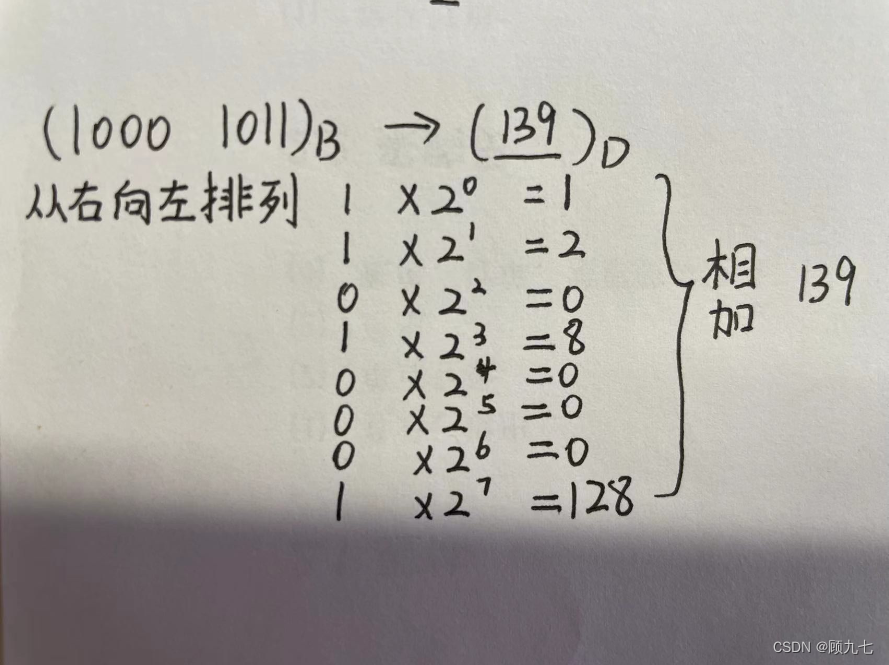

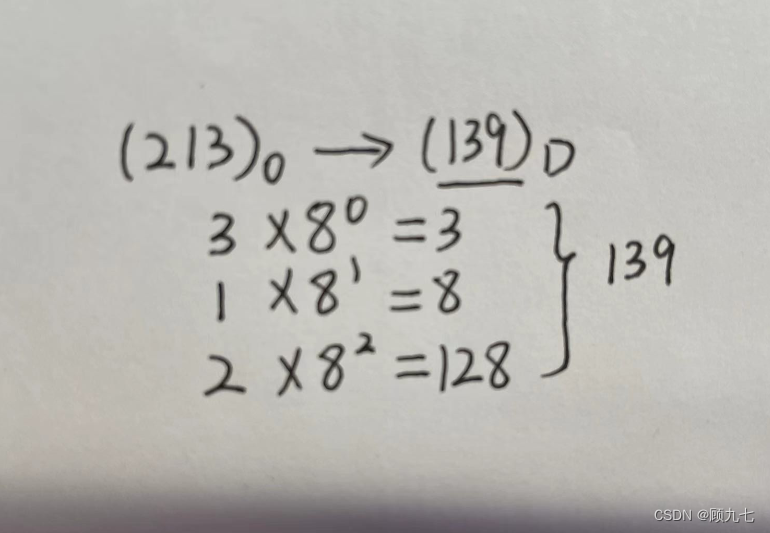

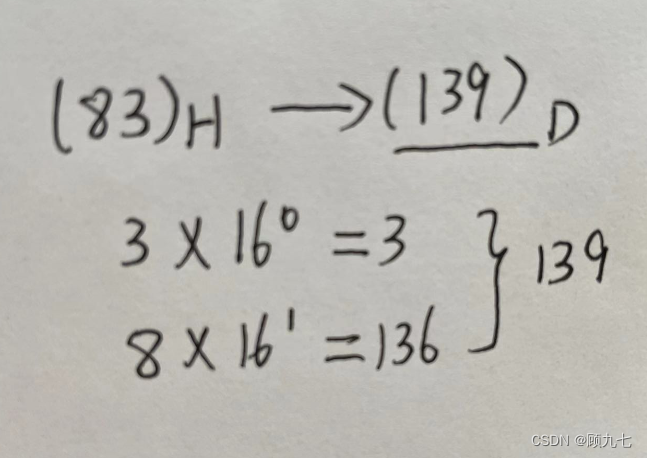

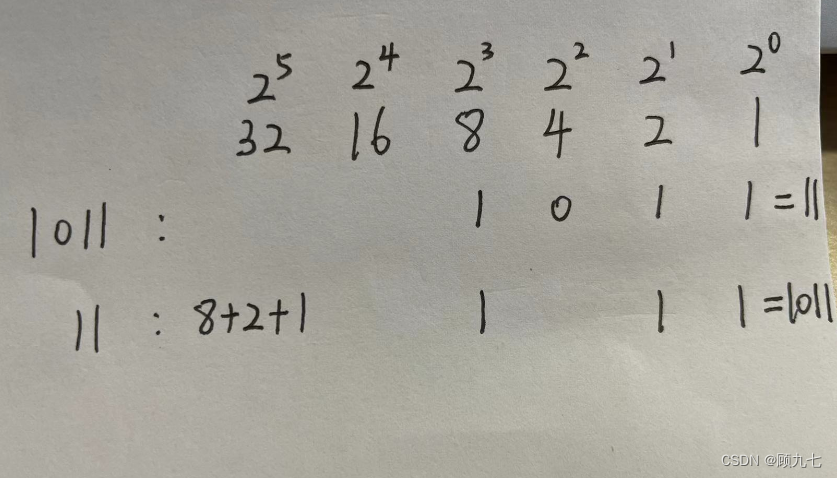

R进制转十进制

按权展开求和法

R进制数从左到右,每位数乘R的index-1

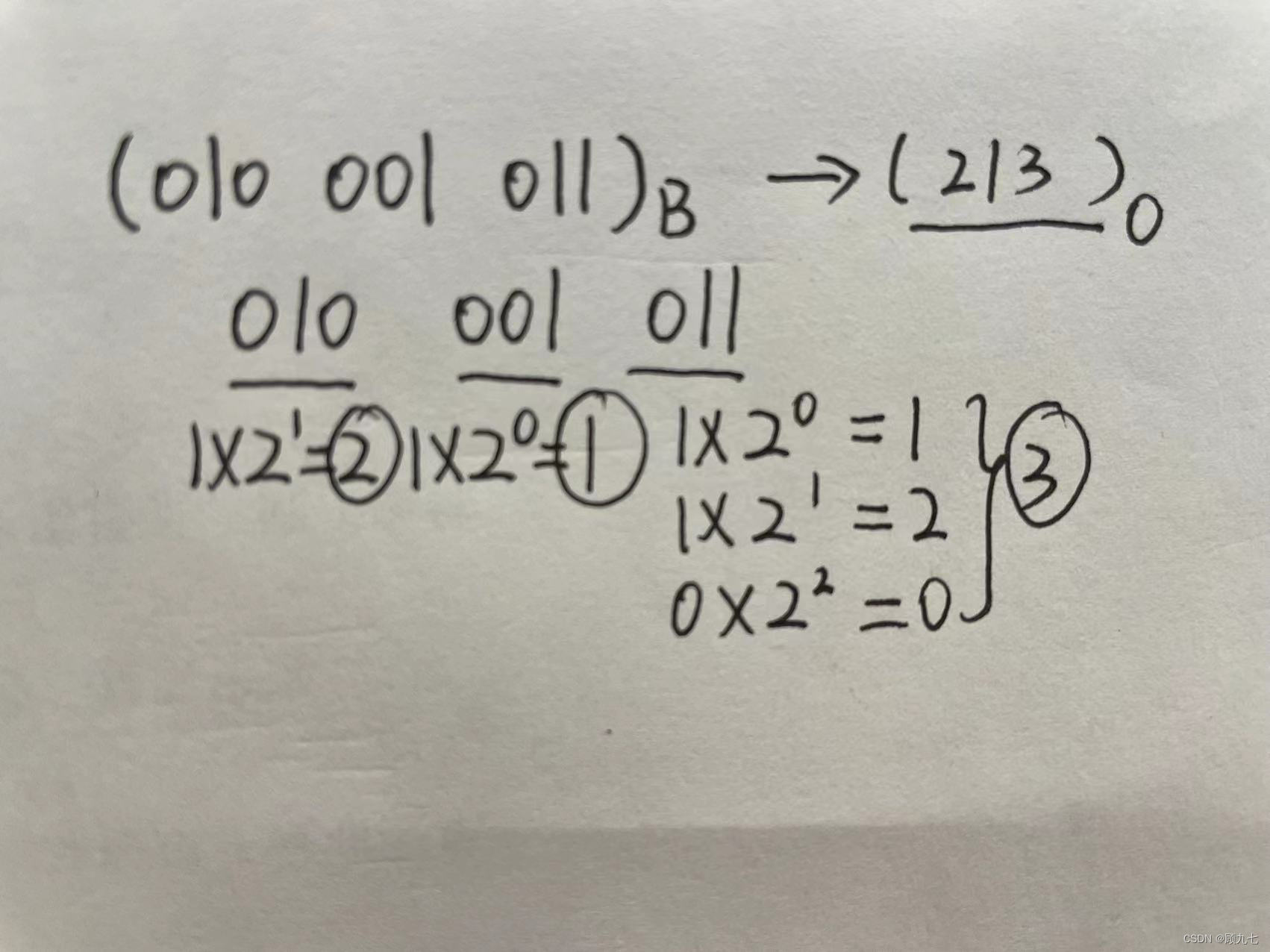

二进制转八进制

三位二进制数可表示一位八进制数,因2的3次方为8,八进制的表示是由0~7组成的

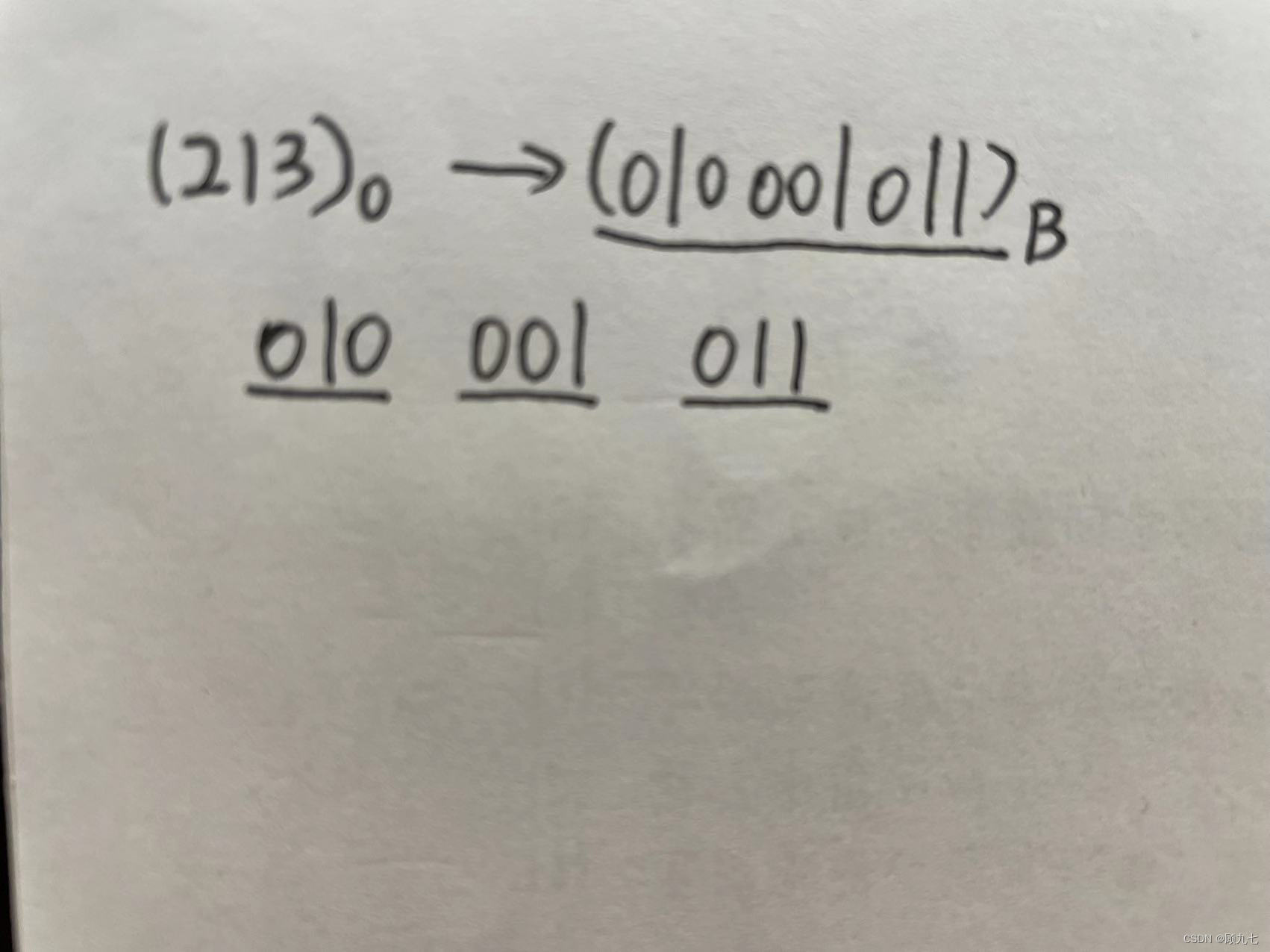

八进制转二进制

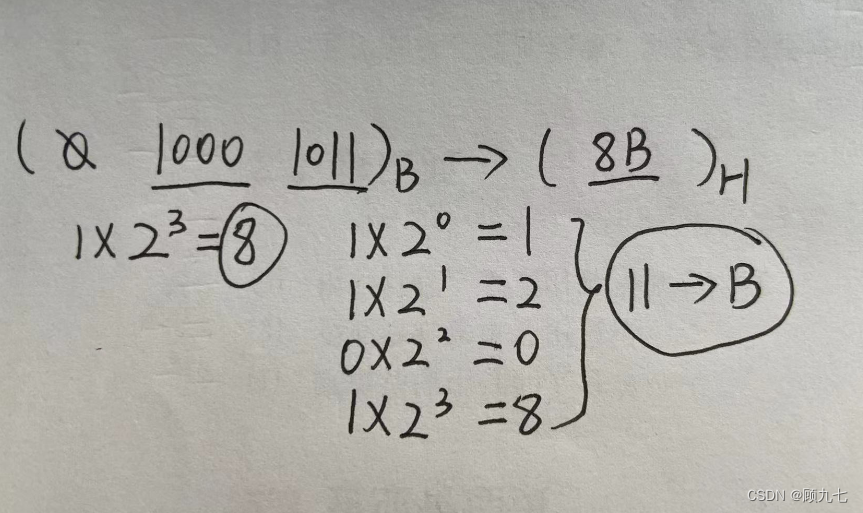

二进制转十六进制

四位二进制数可表示一位十六进制数,因2的4次方为16,十六进制最大为15

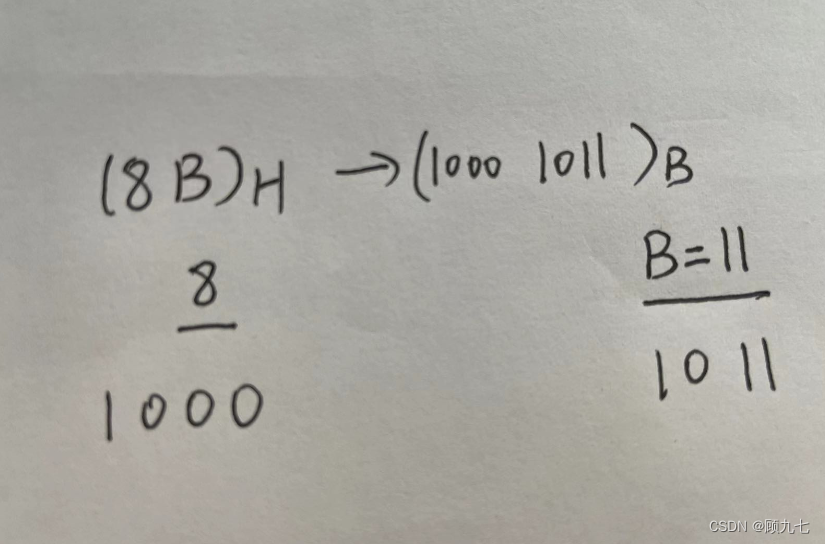

十六进制转二进制

其他进制与二进制的计算

当其他进制数与二进制不好对应时,可将2的次方值写在一旁,用加法计算。

原码反码补码移码

各种数值在计算机中的表示形式称为机器数,采用二进制计数制,符号使用0和1表示,0代表正数,1代表负数。

机器数有无符号数和有符号数之分,无符号数即为正数,有符号数为负数。机器数的最高位代表正负

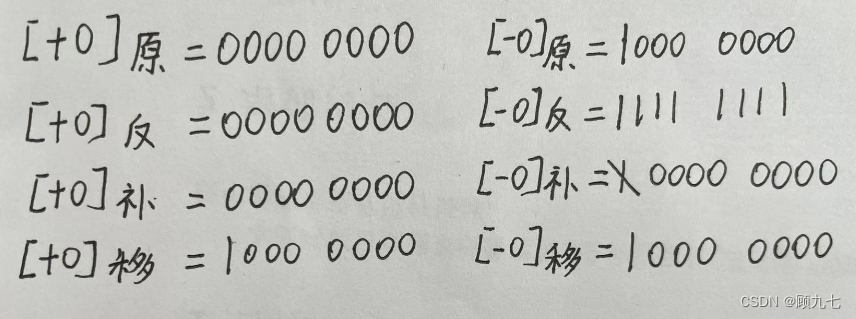

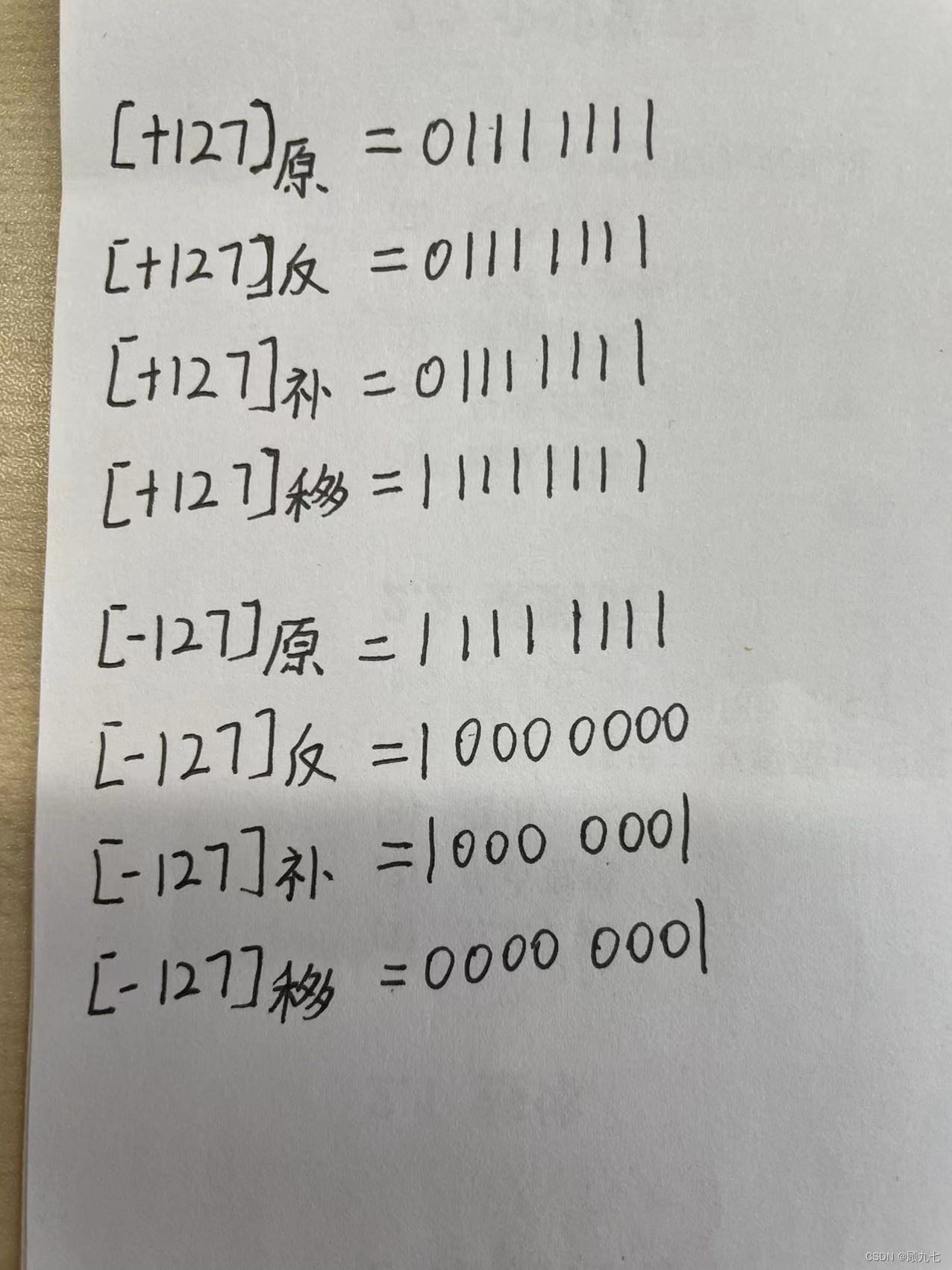

原码

原码表示法中,最高位为符号位,符号位后的值称为数值的绝对值。

0在原码中有两种形式:+0 = 0000 0000 ,-0 = 1000 0000

反码

无符号数的反码:与原码相同,无改变

有符号数的反码:符号位不变,绝对值按位求反

补码

无符号数的反码:与原码相同,无改变

有符号数的反码:反码末位加1。

补码特性: 补码再取补码= 原码

在补码表示中,0有唯一的表示形式:+0补 = 0000 0000 ,-0补 = 0000 0000

移码

无论有符号数还是无符号数,将补码的符号位取反

浮点数

产生的原因

当机器字长为n时,定点数的补码和移码可表示2n个数,原码和反码只能表示2n-1个数。表示范围较小,所以产生了浮点数。浮点数是小数点位置不固定的数,可表示更大范围

性质

在十进制的世界,2782.3527 = 0.27823527104

同样的,在二进制的世界,11001010.01 = 1100.10100124

浮点数定义:二进制数N,也可表示为N=2E*F,其中E称为阶码,F称为尾数。由阶码和尾数表示的数为浮点数。这种表示数的方法称为浮点表示法。

-

浮点表示法表示的数,阶码为带符号的整数,尾数为带符号的纯小数(纯小数指整数位为0的小数)

-

表示格式如下:阶符 | 阶码 | 数符 | 数码

-

浮点数的表示范围大小由阶码决定,表示的数值精度由尾数决定

-

如果浮点数的阶码(包含一位阶符)用R位的移码表示,尾数(包含一位数符)用M位的补码表示,则这种浮点数所能表示的数值范围为:

最大的正数:

最小的负数:

规格化浮点数

规格化就是将浮点数的尾数绝对值限定在【0.5,1】之间

寻址

重要寻址方式按计算速度排列(CPU内部通用寄存器的访问速度比内存中要快)

- 立即寻址,操作数就在指令中

- 寄存器寻址,操作数保存在寄存器中,指令中给出操作数所在的寄存器名

- 直接寻址,从内存中获取操作数的内存地址,指令中为操作数的地址

- 寄存器间接寻址,操作数保存在某个内存单元中,内存地址保存在某寄存器中

- 间接寻址,指令中给出操作数地址的地址。

- 相对寻址

- 变址寻址

工业标准IEEEE754浮点数格式中解码用移码、尾数用原码表示

校验码

作用

检测数据传输过程中是否发生了错误

特性

- 码距位为2,可检错

- 码距大于等于3,可检错,有可能可以纠错

奇偶校验码

通过在编码中增加一位来使1的个数为奇数(奇校验)或者偶数(偶校验)

14. 码距为2,可检错

15. 分为奇校验和偶校验

16. 对于奇校验,只能检测出奇数个数据位出错的情况

17. 常用的奇偶校验码有三种:水平奇偶校验码、垂直奇偶校验码、水平垂直校验码

海明码

在数据位之间特定位置插入k个校验码,通过扩大码距来实现检错和纠错

18. 码距至少为3,可检错,有可能可纠错

19. n表示数据位个数,k表示校验位个数。海明码的格式要保证:2k-1 >= n+k

循环冗余校验码

利用生成多项式为k个数据位产生r个校验位进行编码,编码长度为k+r

20. 码距为2,可检错

21. 代码格式为k个数据位后排列r个校验位

22. 在求循环冗余校验码编码时,采用的是模2运算

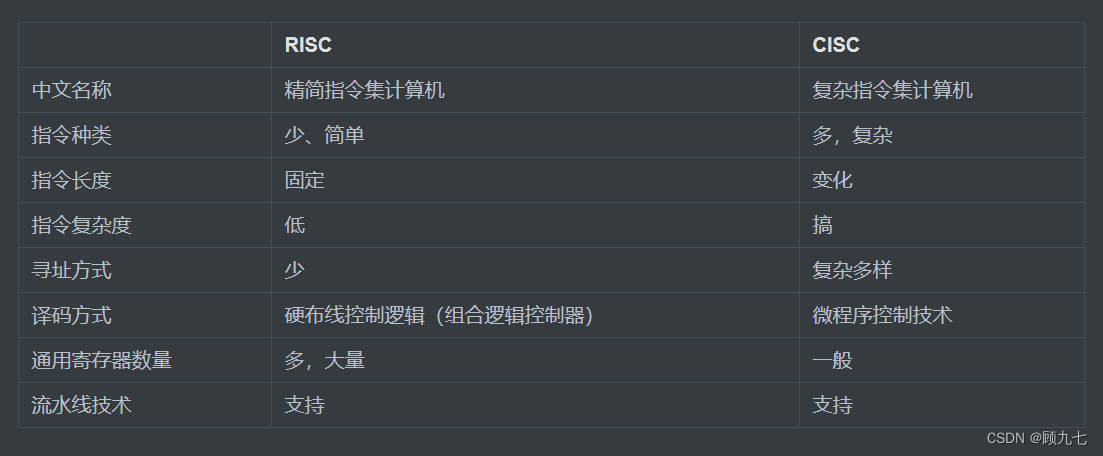

RISC与CISC

流水线

即指令的流水处理。假设指令处理经过三步取指令、计算、输出结果,三步分别记为F/C/O,花费时间分别为0.2s、0.4s、0.1s。

有时间T1、T2、T3、T4、T5…Tn

T1:F1(取出第一条指令)

T2:F2(取出第二条指令)、C1(计算第一条指令)

T3:F3、C2、O1(输出第一条指令的结果)

T4:F4、C3、O2

…

常用概念

- 流水线执行n条指令时间计算公式:第一条指令的执行时间+(n-1)*指令执行过程中时间最长的时间段

- 吞吐率:最长时间段的倒数。若是n条指令的吞吐率,则为n/执行时间

- 加速比 = 采用流水线执行的时间/顺序执行的时间

- 操作周期:最长时间段

性质

- 要使加速比与效率最大化,应对流水线各级采用相同的时间

- 流水线采用异步处理不会提高性能

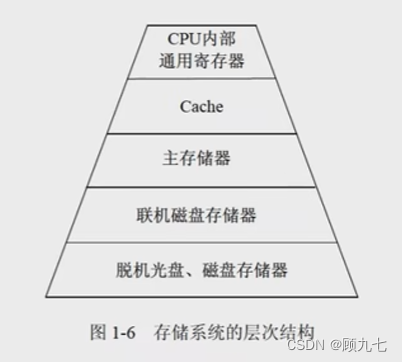

存储器

cache:SRAM

主存:DRAM,周期性刷新,保证数据

存储器的分类

- 按所处位置分类:

- 内存:速度快、容量小

- 外存:速度慢、容量大

- 按构成材料分类:

- 磁存储器

- 半导体存储器:静态存储器(SRAM)、动态存储器(DRAM)

- 光存储器

- 按工作方式分类:

- 读/写存储器RAM

- 只读存储器ROM

- 固定只读存储器

- 可编程的只读存储器PROM

- 可擦除可编程的只读存储器EPROM

- 电擦出可编程的只读存储器EEPROM

- 闪速存储器flash 是按块存储,按块删除。U盘。在断电后,不会丢失数据。可代替ROM,不可代替主存

- 按访问方式分类:

- 按地址访问

- 按内容访问

- 按寻址方式分类:

- 随机存储器RAM

- 顺序存储器SAM

- 直接存储器DAM

知识点

- 相联存储器:是一种按内容访问的存储器

- 虚拟存储器:由主存和辅存组成

- 空间局部性:CPU在访问了x02之后,可能会访问x01或x03,空间上的

- 时间局部性:CPU在访问了x02之后,在短时间内,可能会再次访问x02

高速缓存

现世原因

作为CPU与内存的中转。由于CPU速度超快,内存速度只是快,在存取数据时就会出现CPU能源耗损,所以出现了速度比内存快5~10倍的cache。但cache对于程序员来说是透明的(此处说的透明是说根本看不到)

CPU/cache/内存

cache用来存放当前最活跃的程序和数据。如果cache中没有保存,就将从内存中取出的数据,备份一份到cache中;如果cache中已有了,就直接取cache中的数据。

替换算法

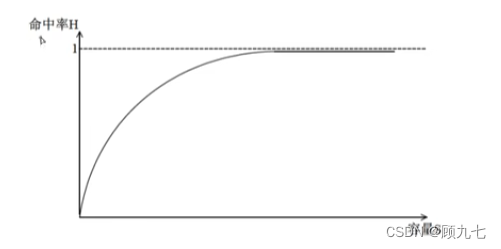

当cache无足够的存储空间存放新的活跃的程序或数据时,就需要使用替换算法替换掉已有的数据。其目标就是使cache可获得尽可能高的命中率。

cache的容量大小决定的命中率的高低,

容量越高,命中率越大,此处要注意不是一直都是线性提高;

但是容量高、命中率大,命中时间就长,成正比。

常见替换算法:

- 随机替换算法

- 先进先出算法

- 近期最少使用算法

- 优化替换算法

地址映像方法

说到了替换算法,就要说下cache怎样保存内存中的数据。

CPU工作时,送出的是主存单元的地址,而应从cache存储器中读写信息,这时就需要将内存地址转成cache存储器地址,这种地址的转换称为地址映像。

-

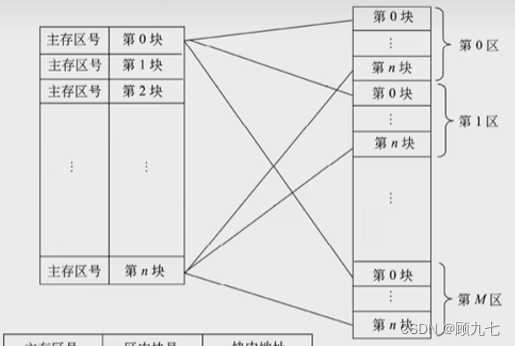

直接映像:主存的块与cache的块对应关系是固定的(冲突大)

内存先分“区”,区内含“块”

cache分“块”

内存的n区中的第0块,一定会放在cache的第0块

-

全相联映像:内存与cache存储器均分成相同大小的块,允许内存的任一块可以调入cache的任一块中(冲突小)

-

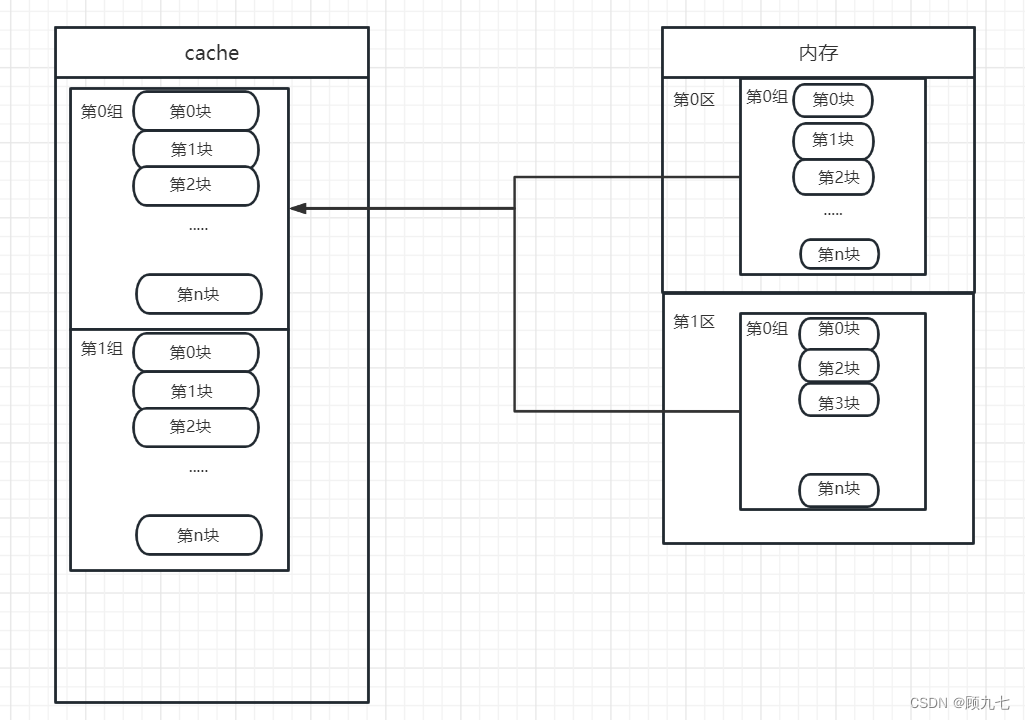

组相联映像:(冲突较小)

cache 先分“组”,再分“块”

内存先分“区”,后分“组”,再分“块”

内存的n区中的第0 组一定会对应到cache的第0组,内存组中的块对于cache中的块又是“全相联映像”,既可对应的第0块,也能对应到第1块

cache与主存地址的映射是由硬件自动完成

中断

计算机执行程序过程中,遇到急需处理的事件时,暂停当前正在执行的程序,转去执行有关服务程序,处理完后自动返回源程序,这个过程称为中断

知识点

- 中断向量:每一个中断向量对应一个中断服务程序入口地址,当中断程序较多时,为提高中断响应的反应速度,将中断向量汇集成中断向量表

- 中断响应时间:从发出中断响应到进入中断服务程序

- 保存现场:即日程生活中被打断时的ctrl+s。目的是可正确返回被中断的程序继续执行

- 为便于实现多级中断嵌套,用堆栈保护断点和现场最有效(先入后出)

- I/O设备发出的中断请求是可屏蔽中断,电源掉电是不可屏蔽中断

- 异常是指令执行过程中处理器内部出现的特殊事件,比如“除运算除数为0”;中断是来自处理器外部的请求,比如“DMA传送结束”

输入输出(I/O)控制方式

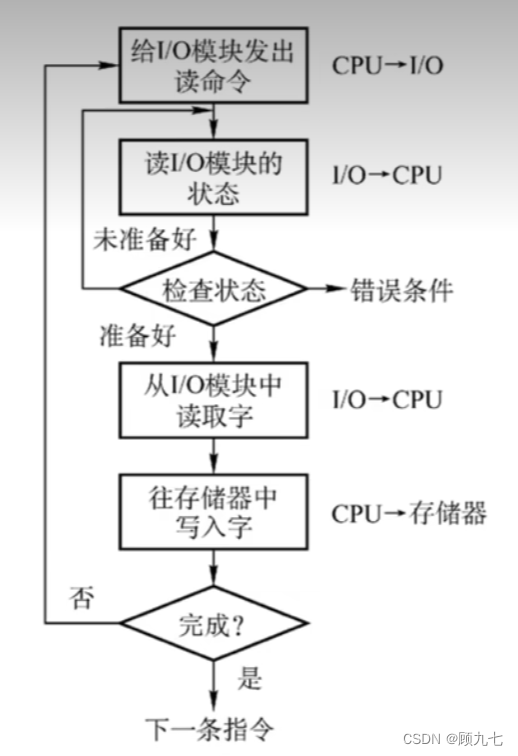

程序查询方式

- CPU和I/O设备串行工作,这就导致CPU的利用率低

- 需要由CPU将数据保存在内存中

- 一次只能读/写一个字

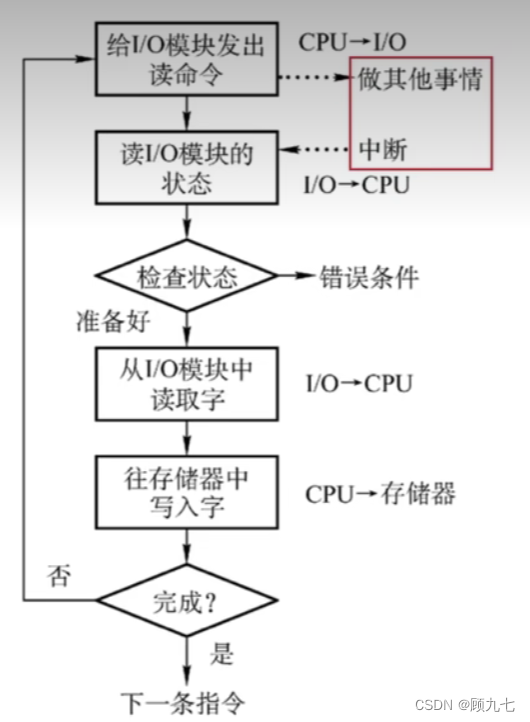

中断驱动方式

- CPU和I/O设备可并行工作

- 需要CPU将数据保存在内存中

- I/O设备通过中断主动向CPU报告执行完成

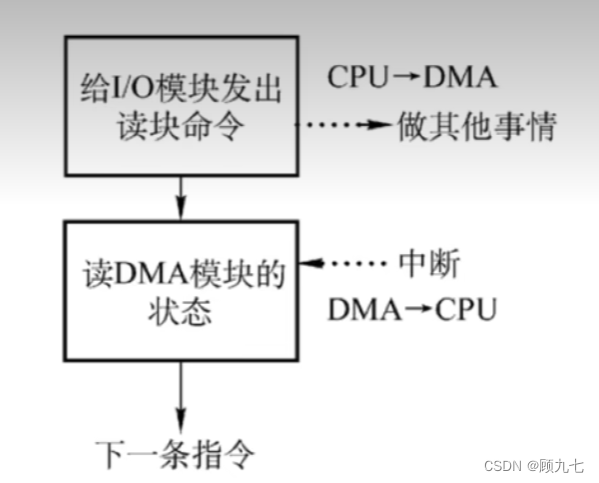

直接存储方式DMA

- CPU和I/O设备并行工作

- 数据传输工作过程中无需CPU参与

- 由外设直接将数据保存在内存

- 一次读写的单位为块,不是字

只限了解的知识点

- DMA操作占用的资源是系统总线,CPU是在一个总线周期结束响应DMA请求的

- 采用DMA传送数据时,每传送一个数据都需要占用一个存储周期

总线(题偏、杂,分低)

计算机系统中,采用总线结构,便于实现系统的积木化构造,也可减少信息传输线的数量。

分类

- 数据总线

- 地址总线

- 控制总线

常见总线

- ISA总线

- EISA总线

- PCI总线:并行传输的内总线

- PCI Express总线

- 前端总线

- RS-232C

- SCSI总线:并行传输外总线

- SATA

- USB

- IEEE-1394

- IEEE-488总线

机密技术与认证技术

常见的计算机网络安全威胁有窃听、篡改、假冒、否认

加密技术

窃听对应的解决技术就是加密技术。加密可阻止对手的被动攻击

常见的加密技术

对称加密(共享密钥加密)

人员A与人员B在数据传输过程中,A用对称加密密钥加密要传输的内容,B需要得到同一个密钥解密传输内容。

只存在一个密钥

缺点:密钥分发有问题。在密文传输给B之后,密钥传输给B的方式需要明文

优点:解密加密速度快;适合加密大量明文数据

非对称加密(公钥体系、公开密钥体系)

人员A与人员B各自有一把公钥、一把私钥,其中公钥人人都知。A给B传输数据时,先用B的公钥加密,B获取密文之后,用自己的私钥解密,反之亦然。

公钥与私钥之间无联系,不可通过推断得知对应的公钥或私钥

优点:密钥分发无问题

缺点:解密加密速度慢;不适合加密大量明文数据

认证技术

篡改对应的解决技术是摘要;假冒和否认对应的解决技术是数字签名。认证可以阻止对手的主动攻击

常见的认证技术

摘要

人员A在给B发送信息时,在密文中携带着使用哈希算法明文 AH 生成的摘要,

B在接收到后,解密密文生成明文,再次使用哈希算法对明文 BH 进行处理。两次的摘要进行对比,若对比相同,咋未被篡改;否则被篡改了。

数字签名

A在密文中增加对摘要用自己的私钥进行加密的密文,

B获取后先对整个密文解密,再次使用A的公钥对摘要密文进行解密(此处就可以确定是不是A发送的消息),再对内容密文进行解密。

对内容明文进行哈希算法处理后,对比。就可以确定内容是否被篡改。

用发送方的私钥进行签名(加密),用发送方的公钥解密

数字证书

目的是防止别有用心之人C在人员A和人员B公钥信息传输过程中,将A给B的自己的公钥替换成C的公钥,这样即使使用了摘要和数字签名技术,也无法避免“假冒”的情况,所以引入了第三方机构的参与–数字证书。

该技术只针对非对称加密,CA机构有自己的私钥和公钥。人员A向CA机构申请数字证书,将人员A的基本信息、A的公钥发送给CA机构,CA机构使用自己的私钥进行加密(签名)。人员B在得到密文之后,从CA机构那里获取A的数字证书,使用CA机构的公钥解密获取A的公钥,以此来解密A的密文。这样即使C篡改了A发给B的A的公钥,也没关系,B根本不会使用A发过来的公钥。

加密算法

常见对称加密算法

- DES

- 3DES

- IDEA

- RC-5

- AES:分组加密算法

- RC4

常见非对称加密算法

- RSA

- ECC

- DSA

MD5

- 是一种摘要算法

- 对任意长度的输入计算得到的结果长度为128位

可靠性技术

R1、R2、R3…表示部件的可靠性

串联系统可靠性计算公式:R= R1R2R3*…Rn

**并联系统(冗余系统)**可靠性计算公式:R= 1-(1-R1)(1-R2)(1-R3)…(1-Rn)

逻辑与、或、同或、异或

true为1,false为0

逻辑与&

0&0 = 0

1&0 = 0

0&1 = 0

1&1 = 1

逻辑或 ||

0 || 0 = 0

1 || 0 = 1

0 || 1 = 1

1 || 1 = 1

逻辑同或

相同为 1 ,不同为 0

逻辑异或

相同为 0 ,不同为 1

杂知识点

- 主动攻击:重放、IP地址欺骗、拒绝服务、系统干涉、修改数据命令

- 被动攻击:流量分析、会话拦截

- 算数左移相当于给操作数执行乘2操作