系列文章目录

本系列博客重点在深圳大学计算机系统(3)课程的核心内容梳理,参考书目《计算机组成与设计》(有问题欢迎在评论区讨论指出,或直接私信联系我)。

第一章 计算机组成与设计01——计算机概要与技术_@李忆如的博客-CSDN博客

第二章 计算机组成与设计02——指令:计算机的语言_@李忆如的博客-CSDN博客

第三章 计算机组成与设计03——计算机的算术运算_@李忆如的博客-CSDN博客

第四章 计算机组成与设计04——处理器

梗概

本篇博客主要介绍深入计算机组成与设计第四章处理器的相关知识。

一、引言

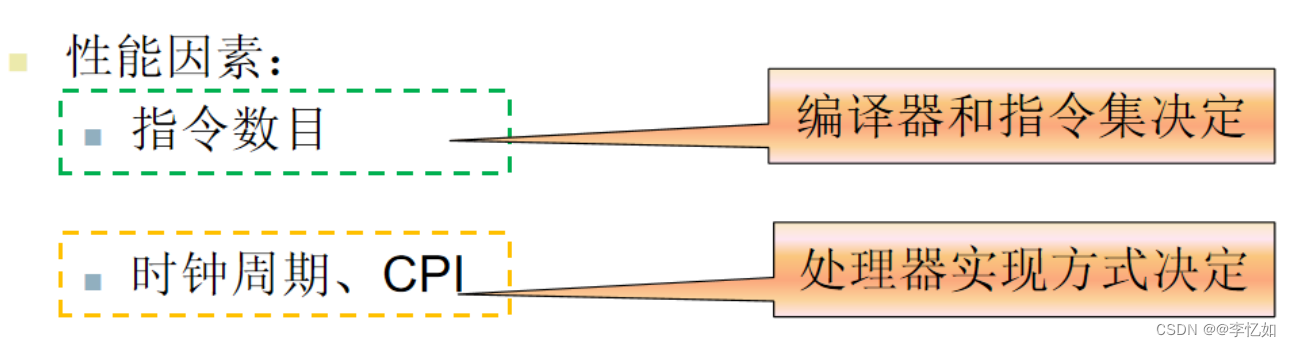

1.计算机性能因素

计算机性能因素与其决定因素如下:

2.基本的MIPS实现(指令部分)

一个基本的MIPS的实现方式如下:

指令的执行步骤如下:

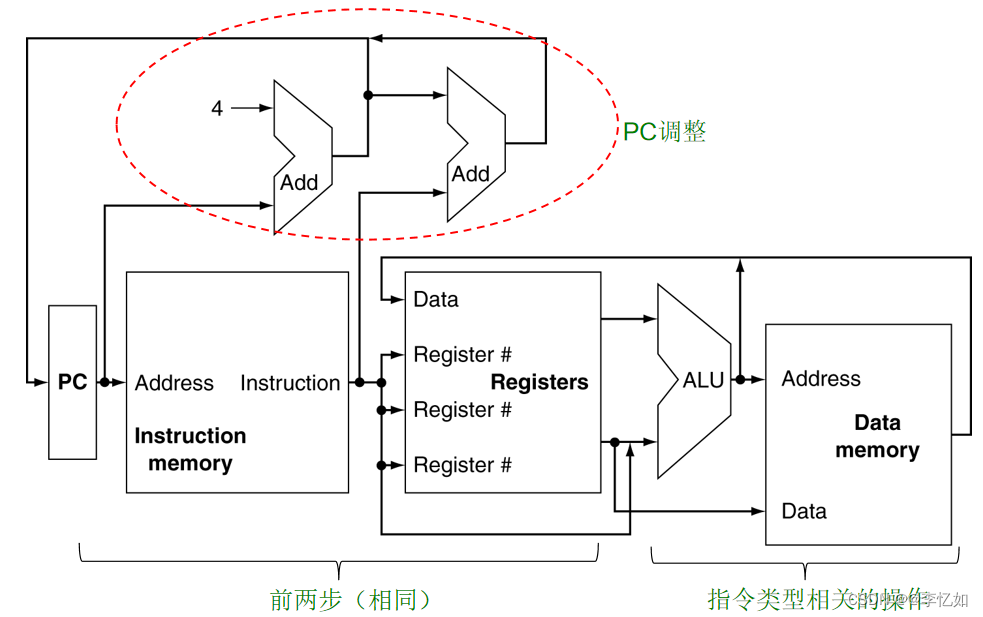

3.CPU 抽象视图

算术逻辑指令、存储访问指令、分支指令的CPU抽象视图分别如下:

Tips:某个操作的数有多个来源时,需要加入复选器调整视图(如bne、lw、sw)

Tips:某个操作的数有多个来源时,需要加入复选器调整视图(如bne、lw、sw)

4.MIPS子集的基本实现

加入后一个MIPS子集的基本实现如下,包含控制信号与复选器。

二、逻辑设计基础

1.组合单元

2.时钟方法

三、数据通路的建立

数据通路:CPU中处理数据和地址的单元部件 Registers ALUs Mux’s Memories …

数据通路部件(datapath element):一个用来操作或保存处理器中数据的单元

程序计数器PC:存放下一条指令地址的寄存器

1.R型指令

2.存取指令

Tips:符号扩展不能漏(为增加数据项长度,将原数据项最高位复制到新数据项多出来的高位)。

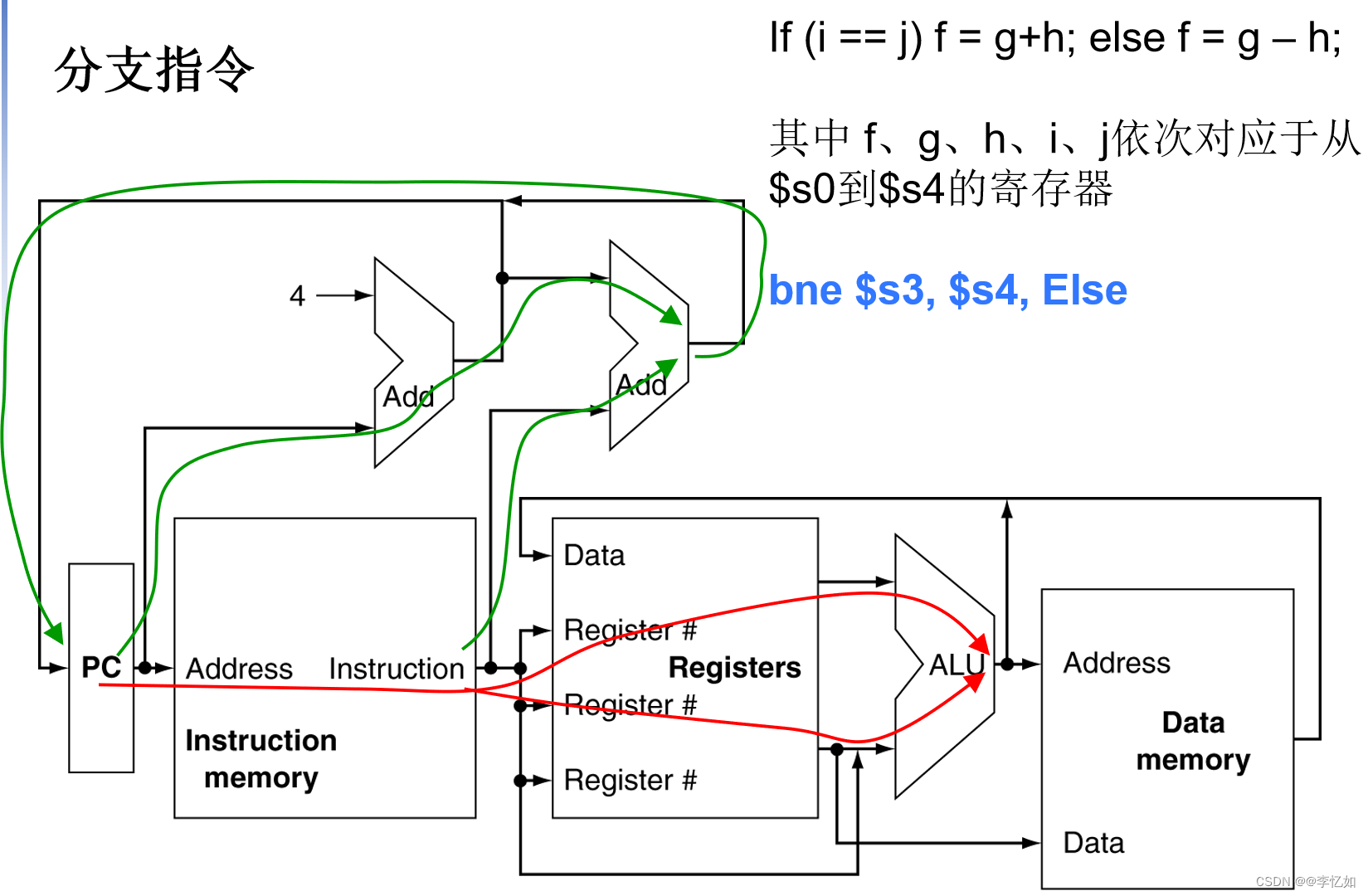

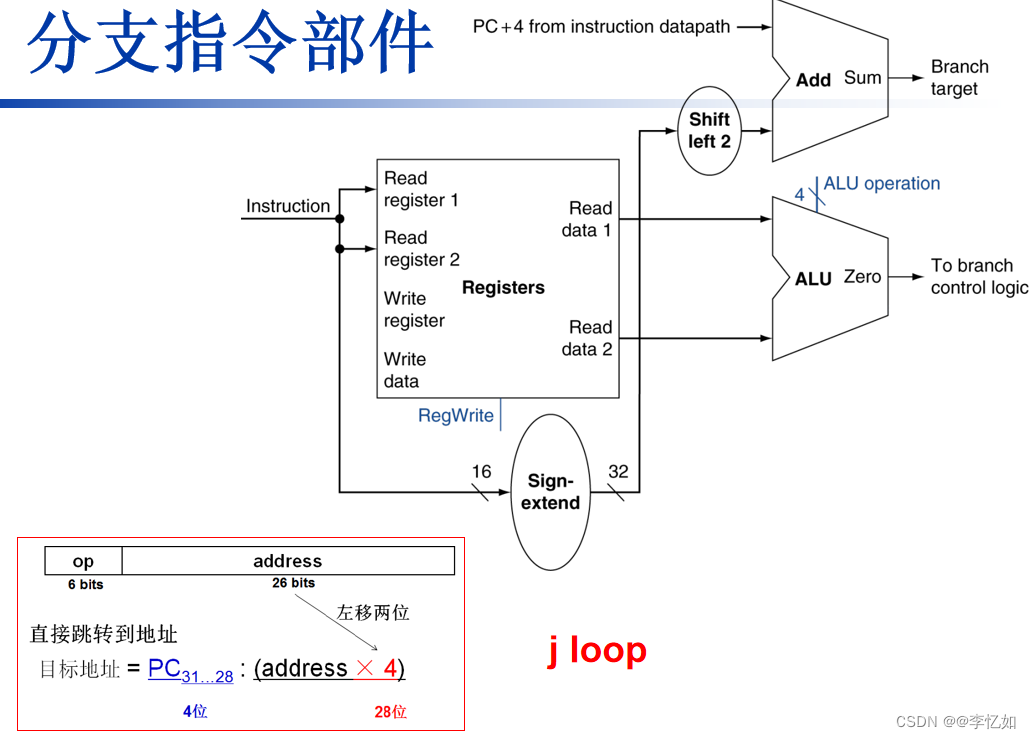

3.分支指令

Tips:beq需要左移两位,MIPS中连续字的地址相差4,且字的起始地址为4的倍数(一个地址为8位,即一个字节,一个字有4个字节)。所以,需要将offset_value左移2位,使其表示为字的地址,确保其能正确跳转到正确地址。

4.简单的数据通路(R型/存取)

初步的数据通路在1个时钟周期内完成指令

每个数据通路部件在一个时钟周期内只能处理一条指令 因此需要独立的数据和指令存储器

当不同指令的数据来源不同时,需要使用多选器

5.完整的数据通路(单周期)

Tips:数据通路必须有独立的指令存储器和数据存储器,因为处理器在一个周期内只能操作每个部件一次,而在一个周期内不可能对一个单端口存储器进行两次存取。

四、简单的实现机制

核心:以MIPS核心指令子集为目标,为数据通路设计控制单元

核心指令: lw, sw, beq, add, sub, and, or, slt, j

1.ALU控制信号

设计单元表示真值表如下:

2.主控单元设计

Tips:增加了指令判断的复选器与ALU控制单元,并标识出了所有控制信号。

控制信号及其含义如下:

加入控制单元后的简单数据通路如下:

各类指令的控制信号如下:

五、流水线概述

单周期处理器缺点:无法应对不同指令路径(处理时间)长短的差异,最慢的路径决定时钟周期,不符合“加快经常性实事件”设计原则。

0.MIPS指令流水

IF: 从内存中取指令

ID: 指令解码& 读寄存器

EX: 执行运算或计算地址

MEM: 访问内存操作

WB: 将结果写回寄存器

Tips:流水线每一步的流水线周期(Tc)一致,取决于最慢处理步骤。

1.流水线的性能

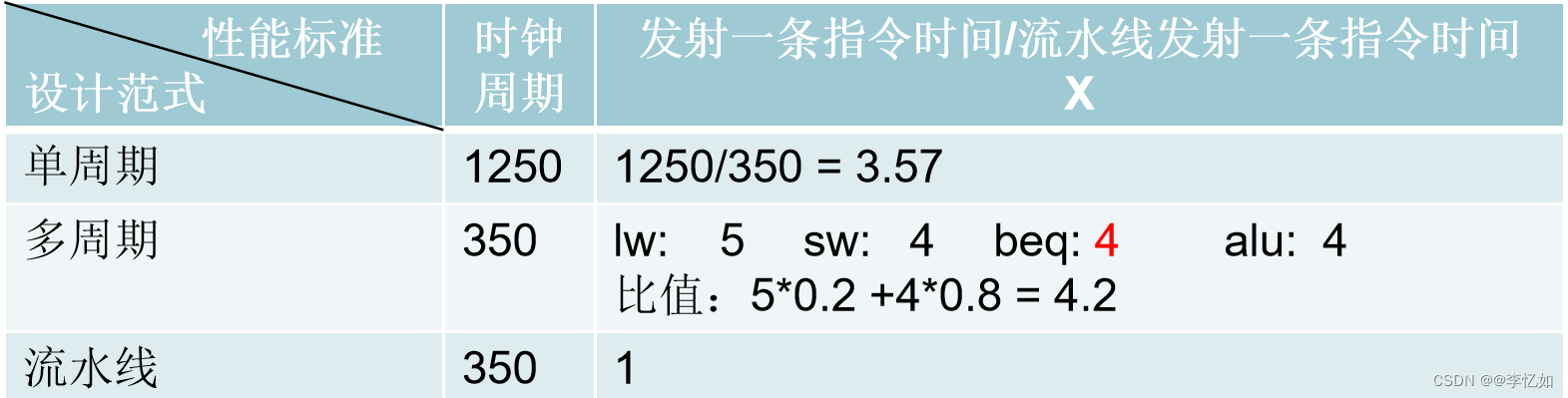

对上述例题(lw)进行分析,性能对比如下:

2.流水线的加速比及分析

流水线vs单周期如下:

流水线vs多周期指令如下:

流水线分析:n个段(以5为例)构成了一个指令流水线,一条指令经过每个段

CPI(平均执行周期数)减少到1,平均每个时钟周期发射或完成一条指令

在任意时钟周期,在每个流水段正执行一条指令的一部分

3.流水线冒险

冒险现象:下一周期不能按时执行下一条指令

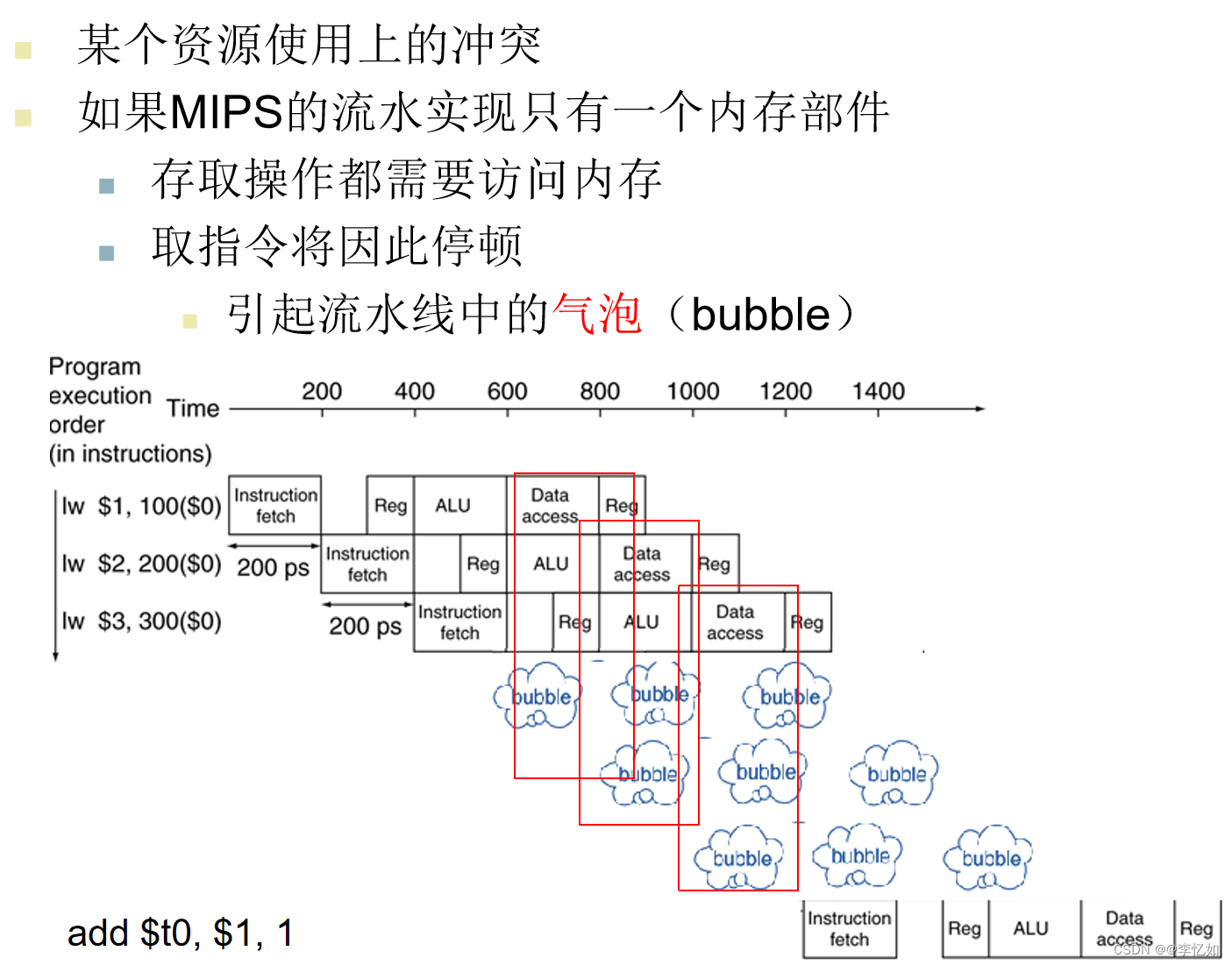

①结构冒险(结构相关):所需的部件忙,暂不可用

②数据冒险(数据相关):需要前面某条指令的计算结果,用于本次计算输入

③控制冒险(控制相关):需要根据前面某条指令的结果来确定分支的选择执行

3.1 结构冒险

定义:缺乏硬件支持导致指令不能在预定的时钟周期内执行的情况

以data access与instruction fecth的冒险为例:

Tips:因此,流水实现的MIPS中指令和数据内存必须是分离独立的 两个独立的L1 cache

3.2 数据冒险

定义:一条指令依赖于前面某条执行的计算结果,缺少指令执行所需数据而导致指令无法在预期的时钟周期内执行。

解决方法如下:

(1)前推

(2)前推+停顿

3.3 数据冒险样例

Tips:时钟周期即横轴数,本题为13个。

Tips:时钟周期即横轴数,本题为13个。

调整后指令如下(减少时钟周期):

3.4 控制冒险

定义:取到的指令不是所需要的(地址变化不是预期)而导致指令不能在预定的时钟周期内执行。

出现原因:决策依赖于一条指令的结果,而其他指令正在执行中(例:下一条指令IF阶段时,分支指令仍在 ID阶段)。

解决控制冒险的方法如下:

(1)阻塞

在分支指令后立即阻塞流水线,避免地址未被计算,样例如下:

分析:在较长流水线中,往往不能在第二级完成分支决策,停顿会带来更大的速度下降。

(2)预测

根据“通过预测提高性能”的设计原则对分支地址进行预测预测,预测错误才需要阻塞。

Ⅰ、恒预测不跳转

一种简单的预测方法就是总预测分支未发生(不跳转),样例如图:

Ⅱ、静态分支预测

一种更成熟的分支预测是基于典型的行为,预测一些分支发生而预测另一些分支不发生,样例如下:

Tips:这种分支预测依赖始终不变的行为,没有考虑特定分支指令的特点。

Ⅲ、动态硬件预测

定义:预测取决于每一步分支的行为,并且在整个程序的生命周期内可能改变分支的预测结果。

实现:保存每次分支的历史记录,利用历史记录来预测。

Tips:较长的流水线会恶化预测的性能(各种方法),并提高错误预测的概率。

3.5 流水线冒险样例

六、MIPS流水化的数据通路

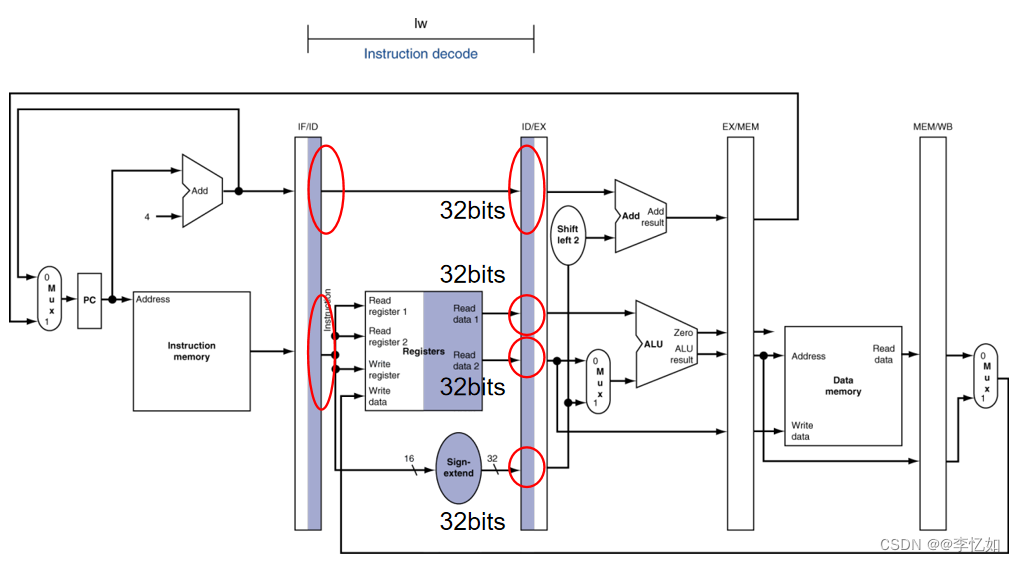

在单时钟周期中,流水线最多五条指令,因此要把之前的数据通路分为五部分,如图:

图中从左到右的指令流中有两个例外:

(1)写回阶段是写回数据通路中间的寄存器(可能导致数据冒险)

(2)选择PC的下一个值的时候,在自增PC与MEM的分支地址间进行选择(可能导致控制冒险)

1.流水线寄存器

通过增加保存中间数据(记录前一时钟周期产生的结果)的寄存器,使得指令过程中可以共享部分数据通路,故需要流水线寄存器,确保一条数据通路实现流水线,加入流水线寄存器如图所示:

Tips:流水线寄存器宽度要足够大(64、128、97、64)

补充:每条指令都会更新PC,PC可以看作是一个流水线寄存器:给IF级提供数据,发生异常时必须保存它的内容。

2.流水线工作方式

以lw与sw为例介绍流水线的工作方式与数据通路实现,红圈为数据传输与存储,供之后的指令使用,如图所示:

2.1 lw/sw指令的流水操作——IF

2.2 lw/sw指令的流水操作——ID

Tips:由于处理器并不知道当前是哪一条指令在被译码,因此它把符号扩展后的常量及两个寄存器的值都读入ID/EX寄存器中,简化控制。

2.3 lw指令的流水操作——EX

2.4 lw指令的流水操作——MEM

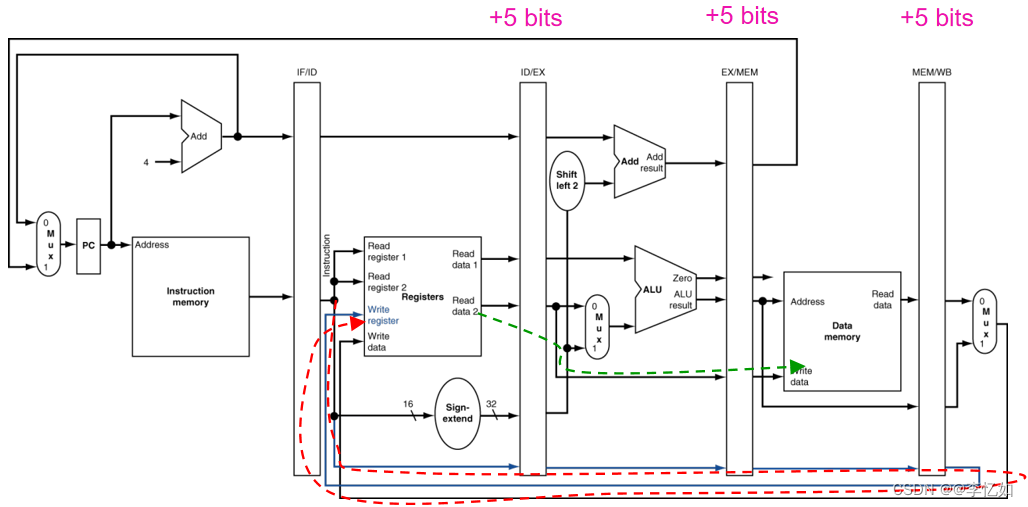

2.5 lw指令的流水操作—— WB

其中,写回寄存器的值是IF/ID流水线寄存器(之前lw的目标寄存器没保存)提供的,但现在的指令是lw后的指令,故写回寄存器的值有问题,需要修正,如图所示:

2.6 sw指令的流水操作——EX

Tips:只有在Sw中才将第二个寄存器的数据写入EX/MEM寄存器。

2.7 sw指令的流水操作—— MEM

2.8 sw指令的流水操作—— WB

3.流水线图形化

3.1 多时钟周期流水线图

多时钟周期流水线图简单但不包括所有细节,构成了资源(部件)的使用情况图。样例如图所示:

Tips:上图描述的是每个步骤使用的物理资源

3.2 传统图示

3.3 单时钟周期流水线图

单时钟周期流水线图表示的是一个时钟周期内整个数据通路的状态,样例如图:

3.4 流水线性能与时钟周期回顾

3.5 流水线例题

Ⅰ、几个学生在讨论五级流水线的效率问题。有一个学生指出并非所有流水级中的指令都是活动的。在忽略冒险的情况下,他们做出了以下几个断言,其中哪一个是正确的?

1)允许跳转、分支、ALU指令使用比5级(装载指令需要的级数)更少的级数将在所有情况下增加流水线的性能。

错误,由2)解释。

2)允许一些指令使用更少的级数并不能提高性能,因为吞吐率(单位时间流出的指令数)是由时钟周期决定的。每条指令所需的流水线级数仅影响它的延迟时间,而不影响吞吐率。

正确

3)不可能减少ALU指令所需的时钟周期数,因为他们需要写回结果。不过分支和跳转指令是可以减少时钟周期数的,因此存在改善性能的机会。

错误

4)相对于尝试减少指令所需的时钟周期数,我们可以延长流水线的级数,虽然每条指令花费更多的时钟周期数,但时钟周期的长度变短了,这样才能提高性能(吞吐率 = 单位时间 / 时钟周期的长度)。

正确

Ⅱ、流水线对时钟周期的影响

1.流水线处理器与非流水线处理器的时钟周期分别是多少?

流水线处理器时钟周期取决于最慢的流水线级:350ps

非流水线时钟周期为一条指令(单周期):1250ps

2.lw指令在流水线处理器和非流水线处理器中的总延迟分别是多少?

流水线总延迟:max (250, 350, 150, 300, 200) * 5 = 350ps * 5 = 1750ps

非流水线:250 + 350 + 150 + 300 + 200 = 1250ps

3.如果可以将原流水线数据通路的一级划分为两级,每级的延迟是原级的一半,那么你会选哪一级进行划分?划分后的时钟周期是多少?

选择最长的一级划分,即ID

划分后时钟周期为:300ps

4.假设没有阻塞和冒险,数据存储器的利用率是多少(占总周期数的百分比)?

lw与sw使用数据存储器,故利用率为20+15=35%

5.假设没有阻塞和冒险,寄存器堆的写寄存器端口的利用率是多少?

alu与lw使用写寄存器端口,故利用率为45+20=65%

6.假设一种多周期的处理器设计,其中每条指令需要多个时钟周期完成。但上一条指令完成前不取下一条指令。在这种设计中,指令仅经过其所需的阶段(例如,存储指令仅需4个时钟周期,因为其不需要WB阶段)。比较单周期设计、多周期设计和流水线设计三者的时钟周期和总执行时间。

Tips:beq因为branch在mem中,所以有控制信号,无WB,所以在多周期中为4。

4.流水线控制信号

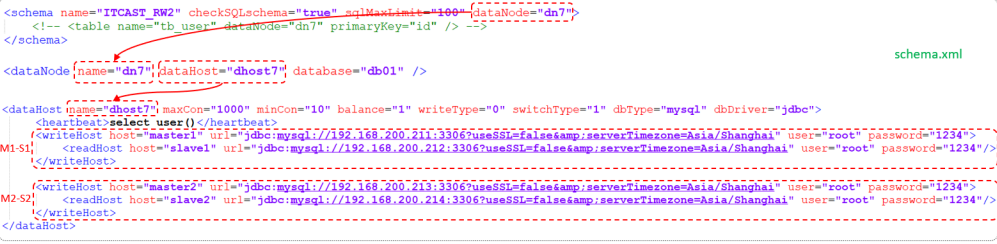

流水线控制信号(简化)如图:

Tips:输入ALU control的六位字段为指令立即数的低六位(符号扩展时无变化)。

EX过程中控制信号有:RegDst、ALUOp、ALUSrc,根据这些信息选择结果寄存器(R、I型指令)、ALU操作、并为ALU读取data2或符号扩展后的立即数。

4.1 控制信号说明

ALUOp信号如下:

其他信号如下:

Tips:控制信号与非流水方式相同的意义,各种指令如下:

4.2 控制信号与数据通路

流水线控制信号根据指令产生:与单周期实现一样,如图:

Tips:ALUOp分为ALUOp1与ALUOp0,为两个控制信号。

流水线数据通路如图:

总结

以上便是绍深入计算机组成与设计第四章处理器的相关知识。在第四章中,主要以计算机系统处理器与流水线的数据通路介绍与实现为主。