硬件保证一致性使得系统功能部件能够在不需要软件编程参与的情况下共享内存。如果任意两个组件对相同地址单元进行写访问,且系统内所有组件看到的这两个写访问顺序是相同,那么这个地址具有一致性属性。

一致性模型

参见下图,每个请求部件RN-F内部都包含了一个局部缓存cache和一致性协议逻辑snoopee。请求部件RN-I没有cache。CHI协议允许一个或多个RN-F的局部cache具有相同地址的数据副本(这个数据长度一般是cache line长度,一个cache line的长度64字节,且地址是按照64字节对齐,数据一致性是以cache line长度为粒度来维护的)。

CHI一致性协议强制要求,一旦对某个地址发生了写访问,那么最多只有一个RN-F的cache保存该地址的数据副本。CHI一致性协议要保证所有RN能正确访问任意地址上的数据。当一个RN对一个地址完成写操作,其他RN-F可以将该最新数据保存在自己的cache中,这样一来,该地址的最新数据就可能存在于多个RN-F的cache中。

当一个地址数据被一个RN-F失效且替换出局部cache后,且其他所有RN-F的局部cache没有数据副本时,片上网络的cache就会更新(要么新分配一个cache保存该地址数据,要么更新命中cache的数据);当所有RN-F的局部cache以及片上网络的cache都没有副本时,系统主存才会被更新。

注意:上面这段并不是强制要求,也允许(并不建议)数据在cache具有副本条件下,更新系统主存。

CHI一致性协议赋予请求结点RN-F自己决定,在整个系统中,一个地址只能存在一个cache副本,还是多个cache副本。(这里是指所有RN-F中的局部cache)。

对于第一种情况,RN-F在修改命中cache的数据时,不需要通知其他RN-F;

对于第二种情况,RN-F在修改命中cache的数据时,必须通知其他RN-F。

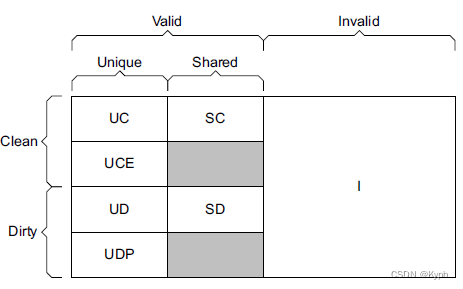

cache状态模型

我们一直讨论的是RN-F的局部cache,而将片上网络cache和系统主存同一看作系统主存。

该地址上的数据在请求RN-F上的状态,以及在其他RN-F上的状态,就决定了在请求结点访问(访问即CHI事务类型)完成后,该地址上的数据在请求RN-F上的状态,以及在其他RN-F上的状态。

V表示cache会命中;

I表示cache未命中;

U表示只有本RN-F的cache会命中,其他RN-F的cache都不会命中;

S表示本RN-F的cache会命中,其他RN-F的cache也可能会命中;

C表示本RN-F的cache副本不一定是最新的;

V表示本RN-F的cache副本一定是最新的。

F表示本RN-F的cache命中,且所有字节都有效;

P表示本RN-F的cache命中,且部分字节都有效;

E表示本RN-F的cache命中,但全部字节都无效;

简单例子

假设一次读写一个cache line的数据(有待进一步确认)

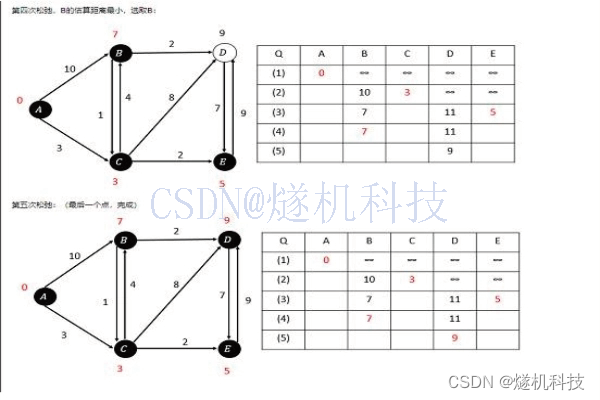

| RN-F0 | RN-F1 | RN-F2 | 主存数据 | |

| 起始 | I | I | I | X |

| RN-F0 写A | UD(A) | I | I | X |

| RN-F1/2读 | SD(A) | SC(A) | SC(A) | X |

| RN-F2写B | I | I | UD(B) | X |

| RN-F0/1读 | SC(B) | SC(B) | SD(B) | X |

| RN-F0失效或换出 | I | SC(B) | SD(B) | X |

| RN-F2失效或换出 | I | I | I | B |

| RN-F0读 | UC(B) | I | I | B |