注意: 时序约束辅助工具或者相关的TCL命令,都必须在 open synthesis design / open implemention design 后才能有效运行。

1、时序约束辅助工具

2、查看相关时序信息

3、一般的时序约束顺序

1、 时序约束辅助工具

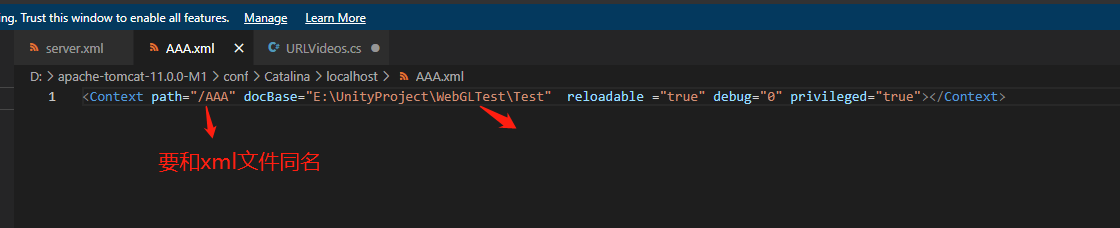

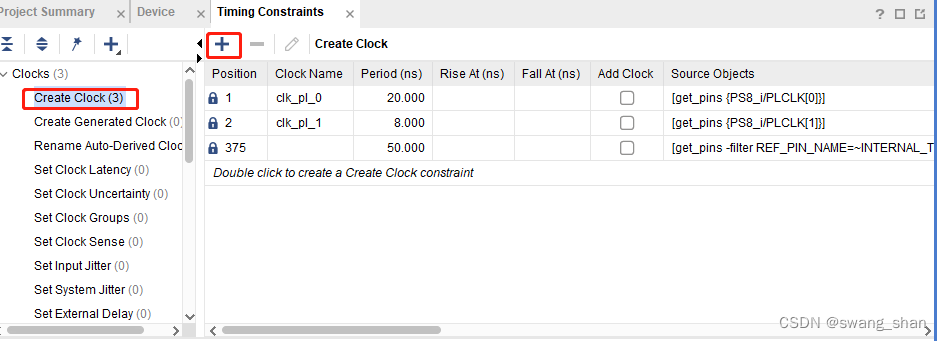

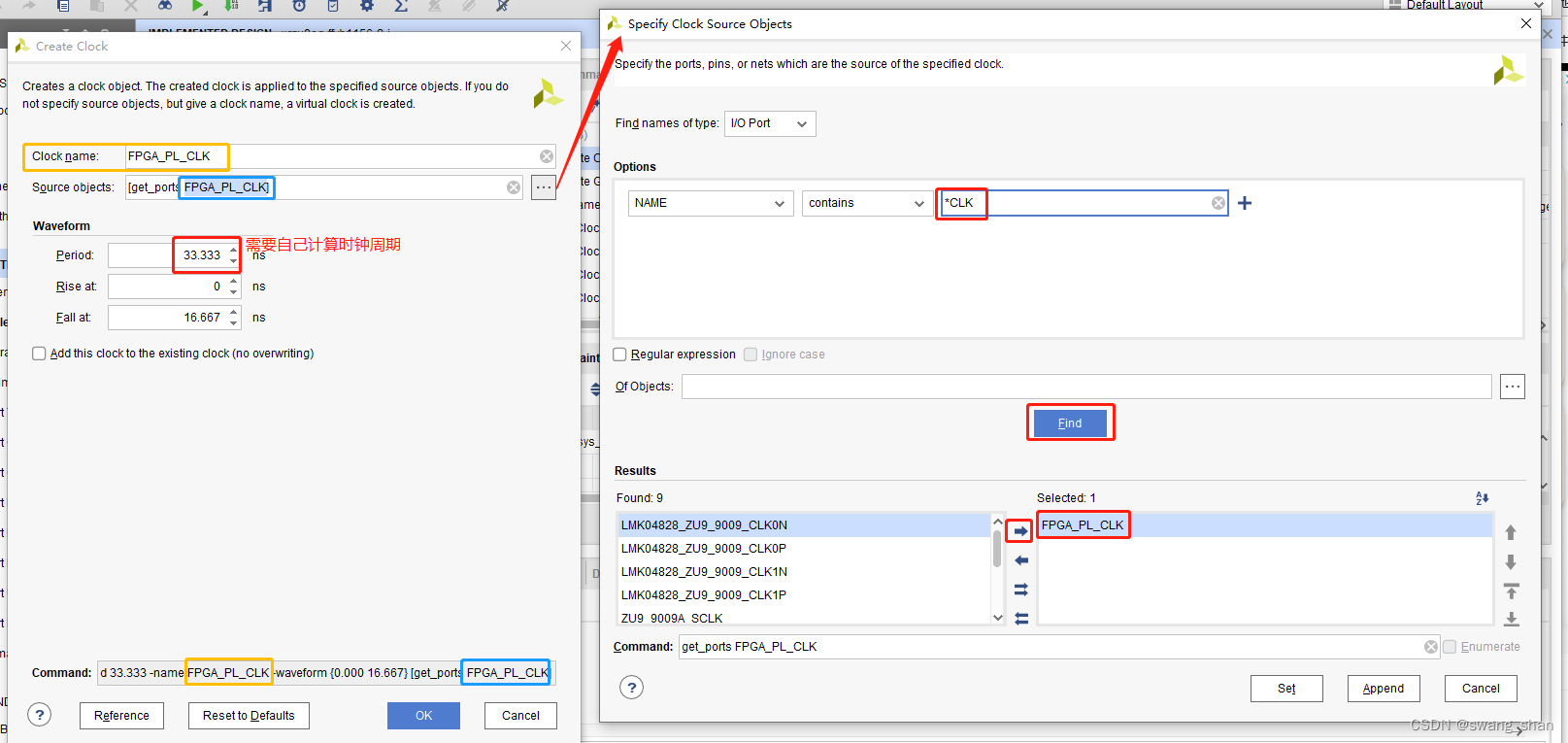

(1)时序约束编辑器: 可以按照左边的Clocks分组添加时钟约束,需要自己搜索要添加的时钟。

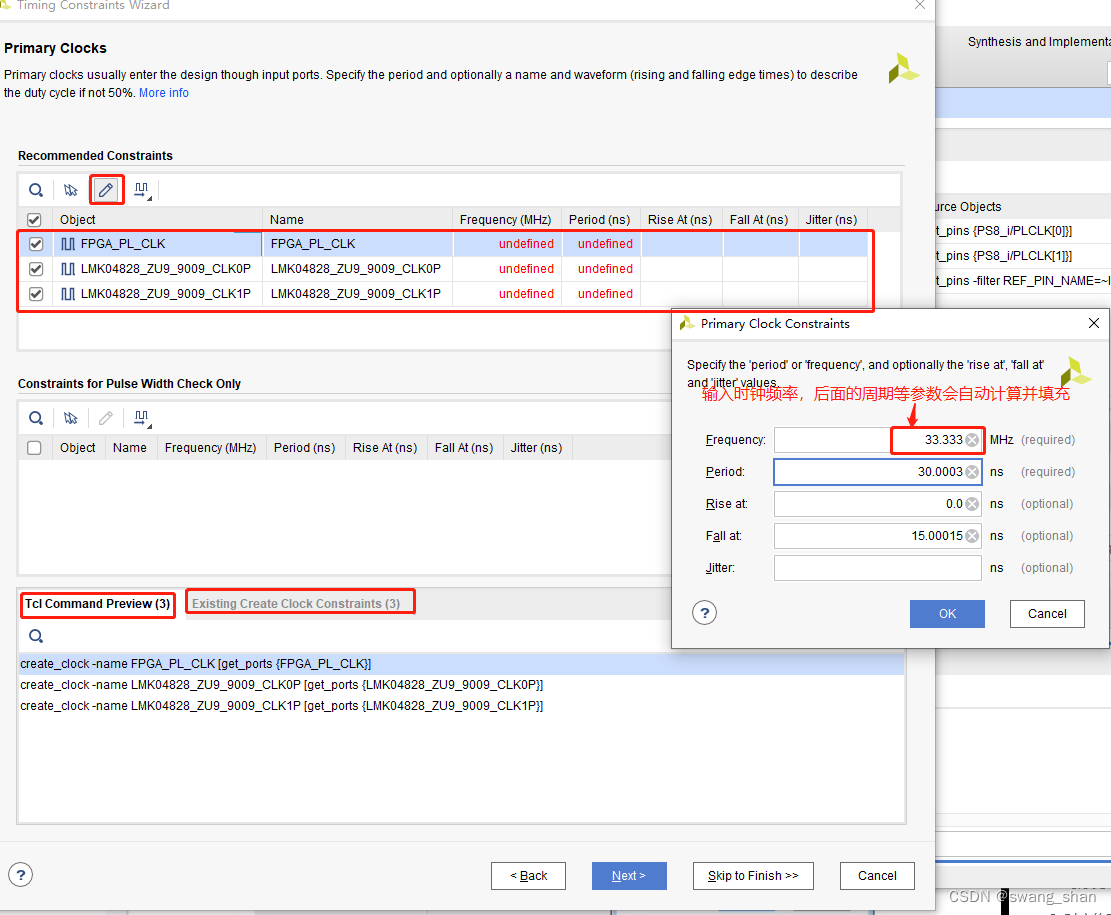

(2)时序约束向导: 按照 primary clocks/generated clocks等时钟顺序一页一页显示添加约束,会显示当前哪些时钟需要添加约束以及已经约束的时钟。

具体用法见:时序约束辅助工具

2、查看相关时序信息

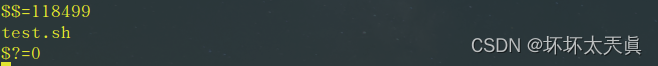

查看所有时钟: report_clock_networks(TCL),会打印已约束和未约束的所有时钟。

查看已约束时钟的详细信息: report_clocks(TCL)打印包含时钟周期在内的的所有时钟信息。

查看是否有 unsafe 时钟: report_clock_interaction(TCL) 或 Implentation- Report Clock Interaction(推荐)。

查看时序约束状态: report_timing_summary (TCL)或者 Implentation- report timing summary (推荐)或者直接 open implemented design ,查看 Timing 窗口,主要查看WNS、TNS、WHS、THS、WPWS、TPWS这6个参数,参数具体含义及标红报错修改方法见后续文章。

3、一般的时序约束顺序

#时序约束

primary clocks (主时钟约束)

virtual clocks (虚拟时钟约束)

generated clocks (衍生时钟约束)

input and output delay constraints (I/O延迟约束)

#时序例外约束

false paths(虚假路径约束)

max delay / min delay(最大/最小延时约束)