首先写这篇文章是因为我有接触到这款芯片,但是在做接口约束时,有许多地方并不是很清楚,因此在这里对官方文档(ug1075)进行了通读,只翻译了我觉得我需要用到和需要了解的地方,具体是什么还需要大家去自己阅读官方文档。

Zynq UltraScale+设备的封装和引脚规格与前几代的区别,包括Zynq-7000 Soc。其中包括:

- 千兆串行收发器(GT)电源引脚组按每列GT 嵌块的列分割

- 标准的HP I/O Bank各有52个SelectIO 引脚,可选择性地配置成24个差分对

- 标准的HD I/O Bank各有24个SelectIO 引脚,可选择性地配置成12个差分对

- 每个Bank都有一个专用的VREF引脚,这些引脚不能用作用户I/O

- 每个Bank的四个差分时钟引脚对由单一类型的全局时钟(GC或HDGC)输入组成

- 每个HP I/O Bank有四个内存字节组,每个组分为上内存字节组和下内存字节组

- 移除了多个PL配置引脚

下面这张表展示了部分Zynq UltraScale+设备的封装尺寸和BGA(球栅阵列结构)间距,这里BGA可以类比CPU背部的引脚,其中包括了文章标题的芯片型号:

图

A

图A

图A 下面这张表则是列出了Zynq UltraScale+设备的千兆收发器信道数量,在所有的设备里,PS-GTR、GTH、GTY通道都是一组MGTRXP、MGTRXN、MGTTXP和MGTTXN引脚:

图

A

图A

图A 下面这张表则是列出了Zynq UltraScale+设备的千兆收发器信道数量,在所有的设备里,PS-GTR、GTH、GTY通道都是一组MGTRXP、MGTRXN、MGTTXP和MGTTXN引脚:

图 B 图B 图B 下面这张表列出了每个设备/封装的可用PS I/O、支持3.3V的HD和支持1.8V的HP I/O的数量以及HD或HP差分I/O的数量:

图 C 图C 图C 上面的I/O口不包括用于配置的GT串行收发器引脚或PUDC_B和POR_OVERRIDE引脚。

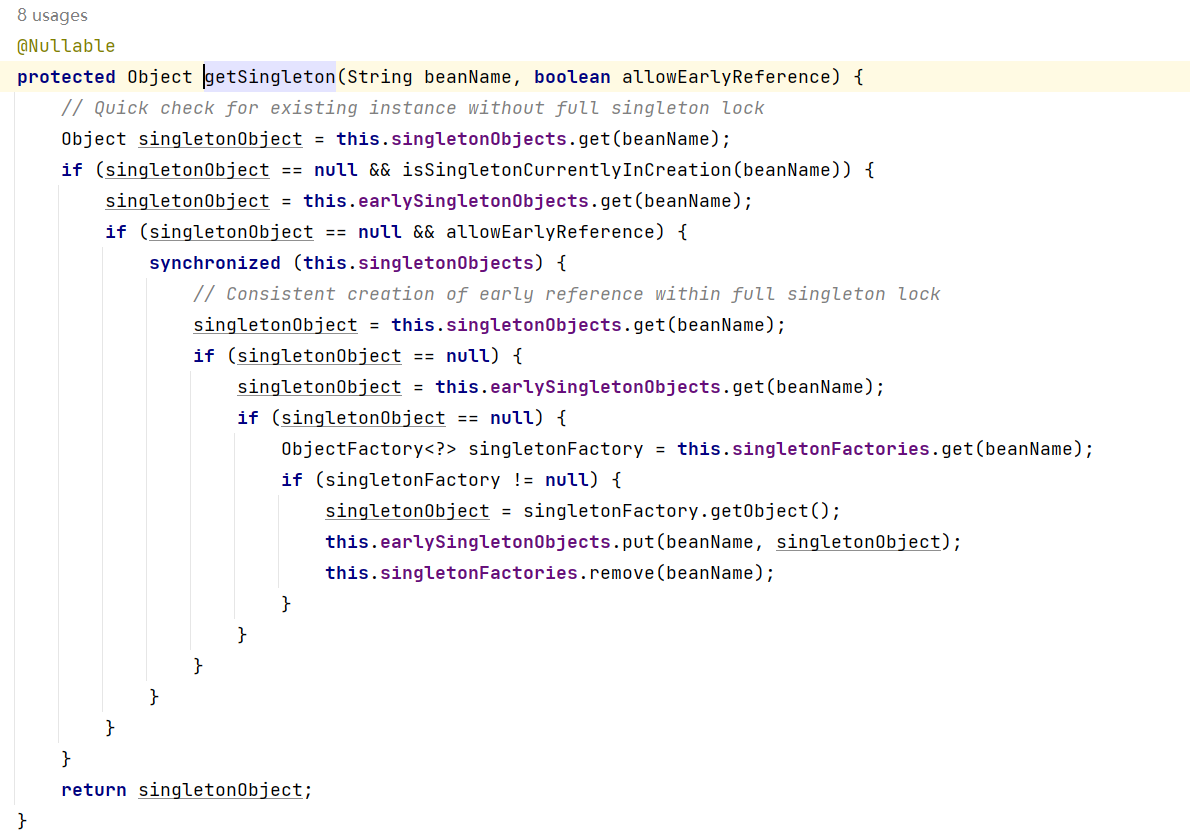

下面这张图则是展示了PS端DDR相关信号接口的定义,从它可以观察有关DDR的读写接口有哪些,有助于理解在PL端控制DDR的话需要考虑到的信号。

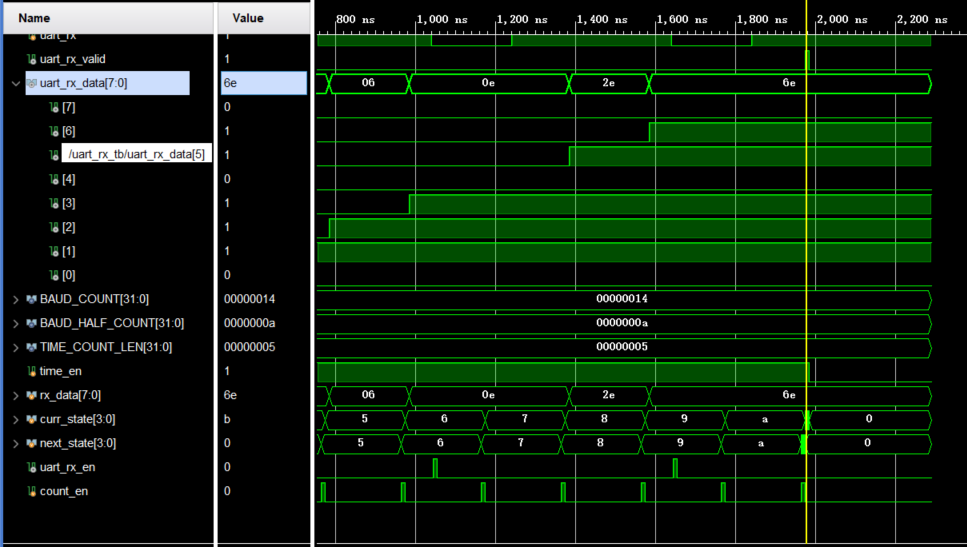

图 D 图D 图D 下面这张图展示了多个千兆收发器引脚(GTHE4、GTYE4、PS-GTR):

图 E 图E 图E 图中标注(4)的位置的L、R、N、S表示GT收发器的四电源组。

下面这张表显示了每个封装可用的封装兼容的设备,但是封装兼容也并不意味着所有引脚都将以相同方式用于封装中的不同设备:

当连接到同样的封装引脚时,许多封装兼容的Zynq UltraScale+设备具有不同的I/O Bank和千兆收发器,由于这些差异的存在,当特定封装间的设备迁移时,Bank(HD\HP),收发器(PS-GTR\GTH\GTY)都必须被考虑。

在封装兼容的一组设备中,每个设备的同一列(由字母A到Z表示)中的存储体和四元组编号到相同的封装引脚,例如在FFVC1760封装中,XCZU11的组88连接到与XCZU17和XCZU19的组90相同的引脚。

图 F 图F 图F 在下面这张图中列出的每一组封装兼容封装,都有一行详细地说明了每个Quad的电源组,这些组根据收发器电源引脚的区域进行标记。

图 H 图H 图H 在模块级Bank编号概述中,需要了解的有如下几个方面:

1、对于每个设备而言,并不是所有的Bank都在每个封装中进行了约束;

2、一个GT Quad等同于四个收发器,与上一点类似,并非所有的Quad都在每个封装中进行了约束;

3、每个Quad中显示的XY坐标对应于该Quad引脚名称中的收发器通道编号,每个Quad中显示一个字目指示符,每个字母对应于上图 F F F中的列,每个Quad的电源组显示在括号[]中。

$ 至于有哪些模块,看图就行了,下面是一张例图:

找到XCZU19EG_FFVC1760的模块编号图如图所示:

至于具体的管脚,是如何分配的,这个可以和硬件组对接,查看原理图得知,其实官方也可以查看,因为都是定义好的,在这里我贴上XCZU19EG_FFVC1760芯片的引脚链接:https://www.xilinx.com/support/packagefiles/zuppackages/xczu19egffvc1760pkg.txt

下面这张图也是可以看到的: