各行各业高速信号软件和硬件的快速发展,带来了更高的频率和带宽。因此,对连接器组件的整体性能要求也更加严格。同时,器件和封装形式、互连以及系统内其他设备的小型化也带来了额外的设计挑战。所有这些都对信号传输完整性产生重大影响。

高速连接器信号完整性基本理论

随着大多数设备和装置的整体结构变得越来越小,并且工作频率越来越高,信号完整性问题也随之出现,需要特别关注。特性阻抗、插入损耗、回波损耗和串扰(其中阻抗和串扰对连接器的信号完整性影响最大)都必须在测试层面进行监控,以确保设备获得最佳性能。

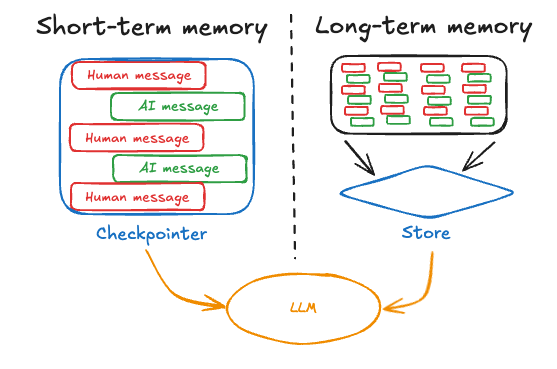

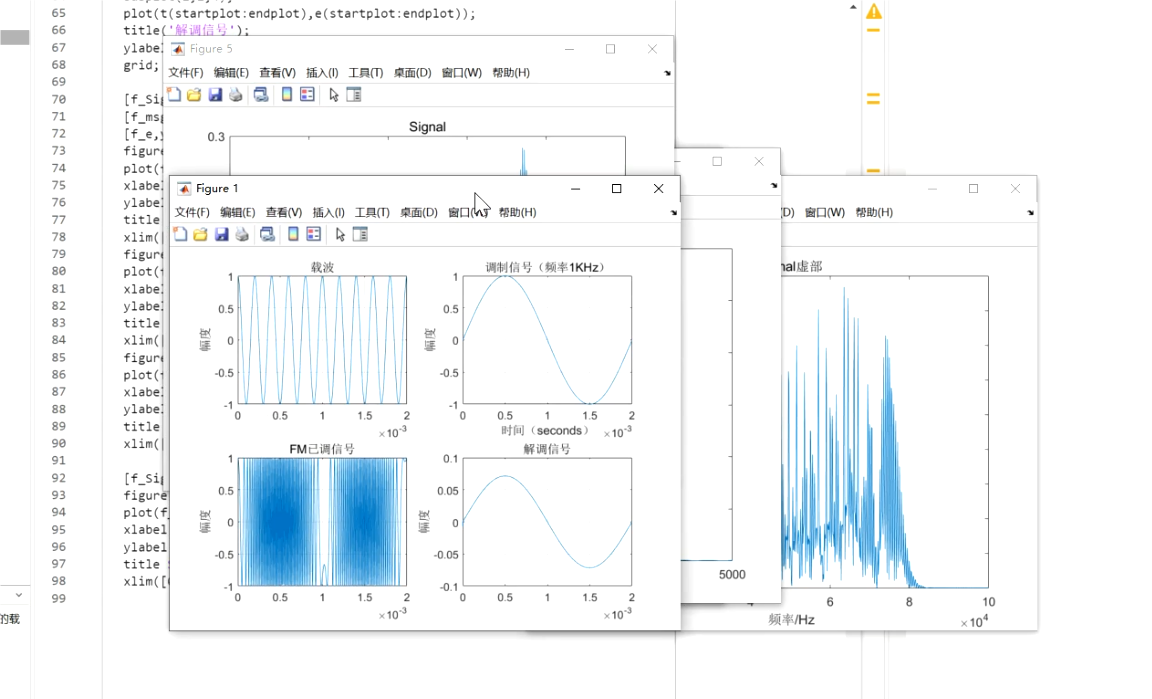

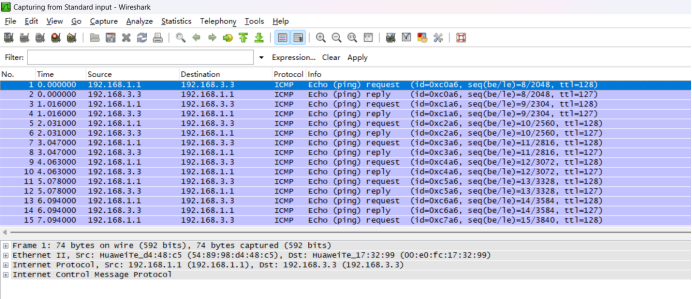

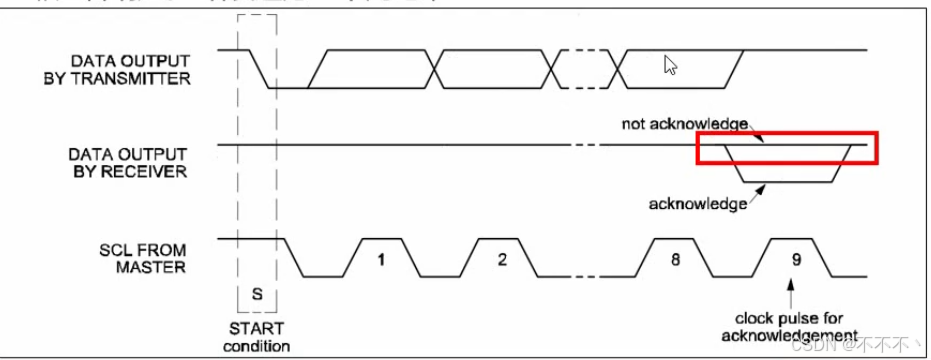

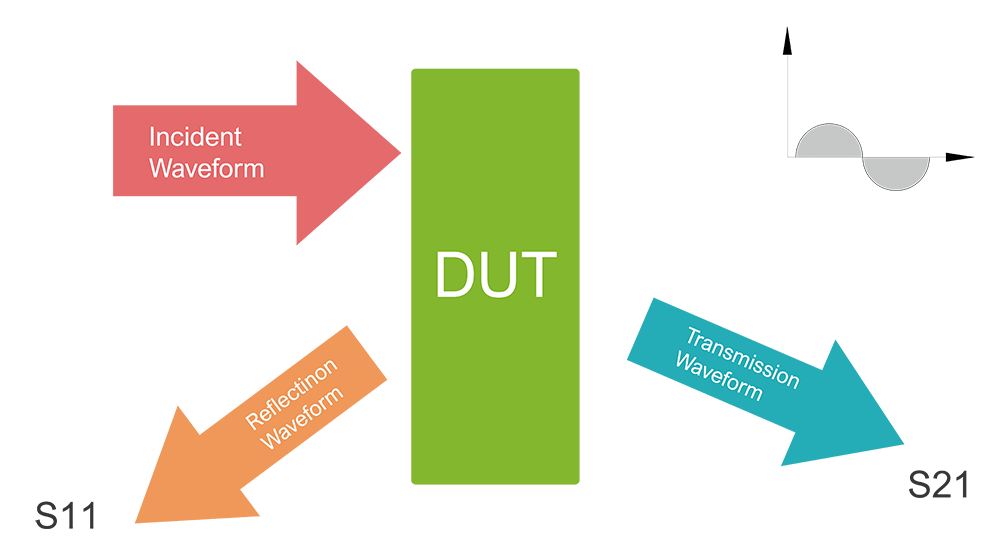

散射参数(S 参数)通常用于信号完整性测试,作为描述互连线宽带高频行为的标准格式。S 参数是一种描述互连线或组件的标准波形在 DUT(被测设备)测试过程中如何散射的格式。

图1:标准波形输入DUT散射。图中,传输波形S21表示插入损耗,反射波形S11表示回波损耗。

影响高速连接器信号完整性的关键因素

一般来说,影响高速连接器信号完整性的主要因素是设计空间、传输速率和信号损耗。不同的PCB布局设计与这些因素密切相关,对整体信号完整性有着至关重要的影响。在不同的PCB布局设计下,连接器所呈现的高频特性会受到影响。

目前,标准的高速连接器已经有完整的结构和规范可供遵循,工程师只需在此结构下调整设计,即可满足特定规范所要求的高频条件。通常情况下,客户只能提供设计空间和所需的传输速率,很多情况下,甚至信号损耗的要求都不确定,这就需要不同的PCB布局和设计上的进一步调整,这时就需要定制化产品。高速连接器的定制化开发可以确保高水平的信号完整性。工程师通常依靠FEA(有限元分析)仿真来辅助高速连接器的设计。

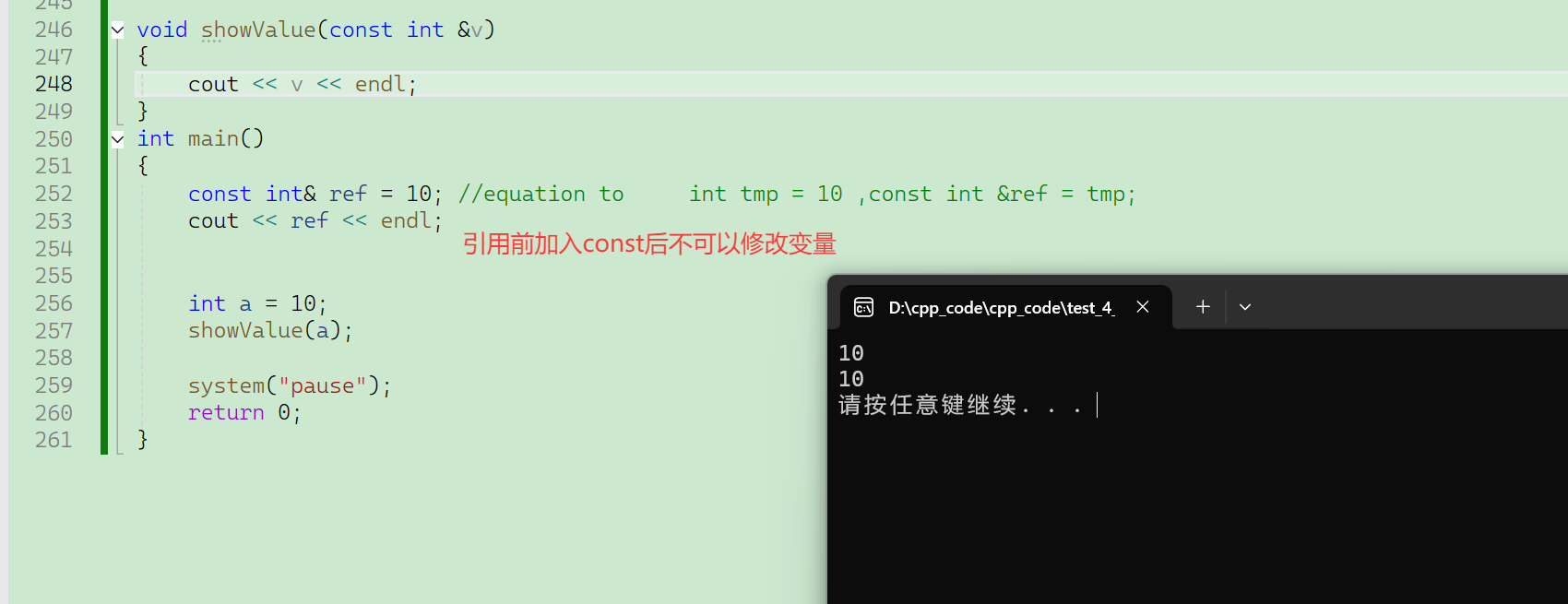

图2:Greenconn 的 1.27mm 高速 BTB/WTB 连接器采用双接触弹簧端子设计,信号传输速度高达 4GBits。

FEA 仿真如何助力高速连接器设计

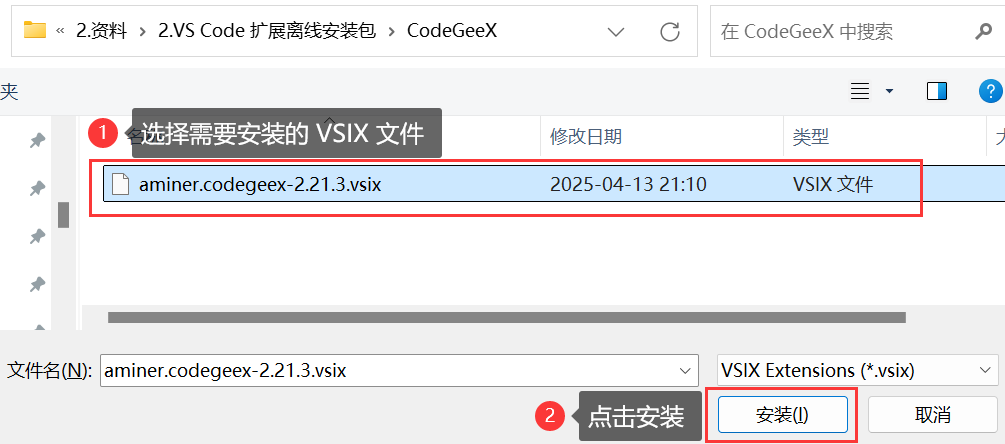

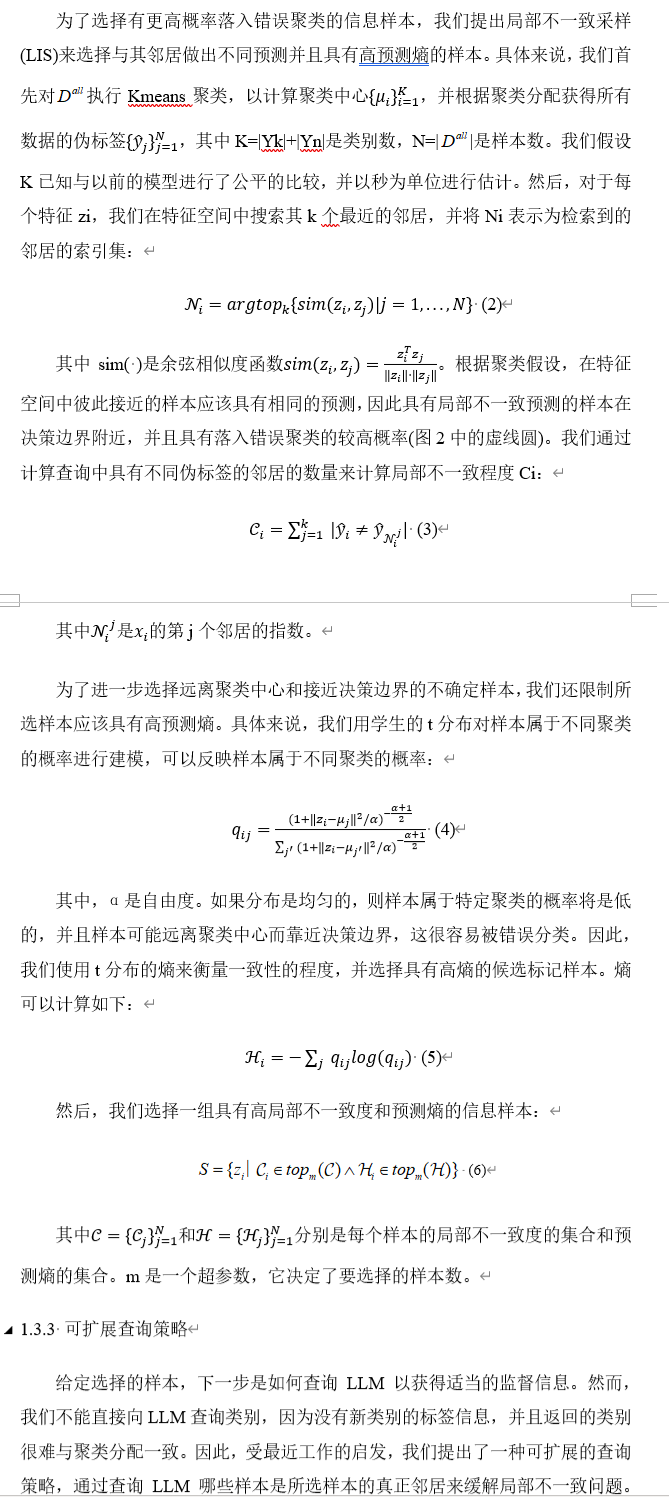

在高速连接器的定制开发中,格林康通过应力及高频FEA仿真,频繁调整机构设计以满足客户需求,并最终对比工艺后产品的高频特性,以确认仿真的有效性。通过多次比较,积累经验,不断提升仿真的精度。流程分为以下步骤:

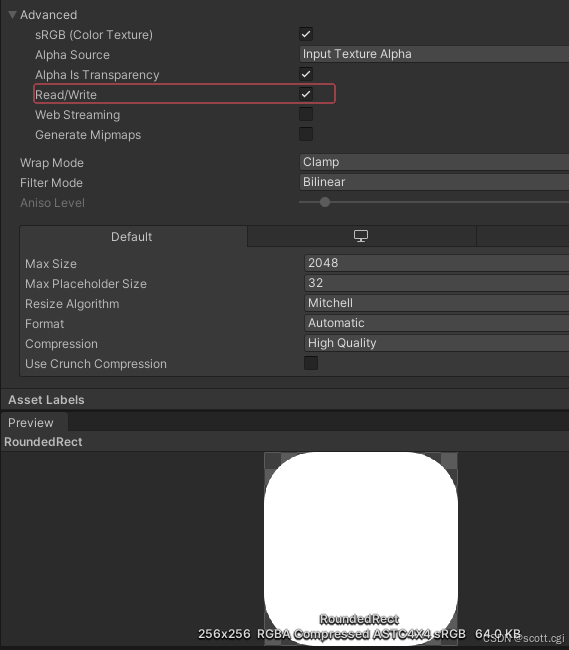

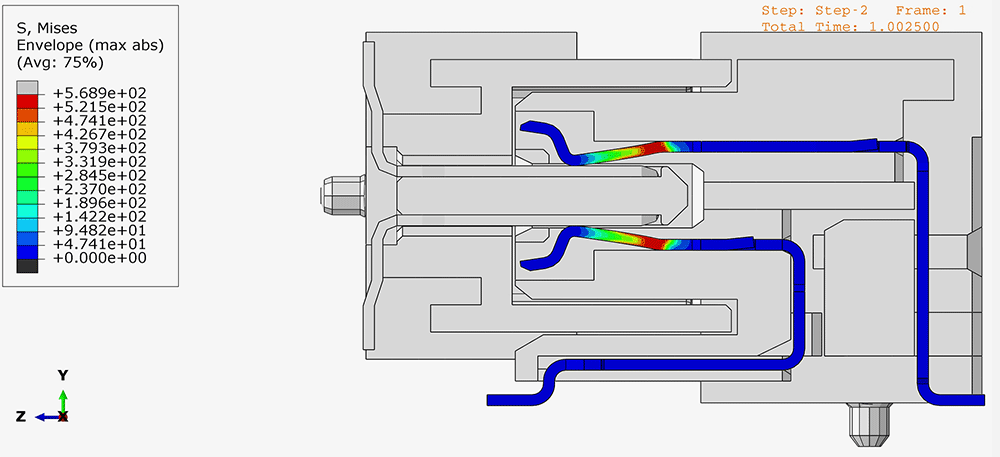

- 经过FEA插拔仿真,可以获得连接器的插拔力数据,从而判断机构设计是否符合要求。此外,通过FEA的仿真结果,可以推导出连接器插入后端子的变形状态。经过多次验证仿真,只要材料参数和FEA仿真条件设置正确,端子的插入力和变形状态都能准确地提供与实际值非常接近的结果。

-

图3:Greenconn通过多个高速连接器FEA获得接近实际的插入力数据和端子应变状态

图3:Greenconn通过多个高速连接器FEA获得接近实际的插入力数据和端子应变状态

- 添加FEA仿真发现的端子变形状态,重新绘制PCB的3D模型。将绘制的模型导入高频FEA软件,设置模型参数,进行高频仿真。

- 经过不断反复的设计和仿真调整,才能得到符合客户需求的S参数,这四个高频条件分别是特性阻抗、插入损耗、回波损耗、以及近端和远端串扰(NEXT和FEXT)。

随着传输频率的提高,信号完整性问题随之而来,对连接器的设计挑战也愈发严峻。理论上,对于高频传输,特性阻抗匹配越好,信号完整性问题就越少。然而,受空间机制的限制,为了匹配高频传输,连接器接触端子的形状会更加不规则。特性阻抗的匹配难度较大,尤其是PCB布局的设计对信号完整性的影响更大。因此,在定制化高速连接器的开发中,通过FEA仿真可以获得更精准的参考,确保信号完整性,满足设备所需的高速传输需求,并有效避免资源浪费,从而节省成本。