目录

一、前言

二、Serdes技术

2.1 芯片间信号传输

2.2 Serdes技术

三、 Xilinx GT

3.1 7系列器件GT

3.2 Ultrascale GT

3.3 Ultrascale+ GT

四、参考资料

一、前言

对于芯片间高速信号传输技术,不得不提serdes以及在Xilinx在此基础上的高速收发器GT系列,下面将简要的介绍Serdes技术以及Xilinx的GT。

二、Serdes技术

SerDes为英文Serializer(串行器)/DeSerializer(解串器)的简称。它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。

2.1 芯片间信号传输

芯片间数据传输时,要保证数据准确被接收端接收,需要考虑时钟信号在准确的时刻采集数据信号,因为需要考虑时钟信号与数据信号的同步。根据时钟信号与数据信号的同步方式分为系统同步,源同步,自同步

系统同步:发送端和接收端的时钟来自同一个外部时钟,简单原理图如下

对应的详细时间模型如下图,下图中灰色背景的都是实际需要考虑的,可见需要考虑不少相关单元的延时。

但系统同步存在以下缺陷

1)时钟到达两个芯片的时间无法真正同步,存在时钟偏斜Clock skew

2) 各个数据的传输时延存在差异

3)时钟和数据的传输时延也存在差异

源同步:接收端的时钟和数据都来自发送端

源同步对应的时间模型如下图,相比于系统同步,只需考虑输出延时和板间延时。源同步设计中,发送芯片会把数据信号和时钟信号做相同的处理来保证相同的时延。在实际运用中,DDR即使用源同步的方式,可达到800MHz,但如果需要更高的速率,则有两种方法,提高时钟频率或者增大数据位宽。

自同步:源同步设计会带来时钟域的增加,如上图中的clk2,此时,就出现了自同步这种方式,时钟信号和数据信号在同一路传输,serdes即为此种方式。

对应的时间模型如下图,自同步中包含了3个主要模块:串并转换,并串转换以及时钟数据恢复单元

并串转换有两种实现方式:移位寄存器,旋转选择器(revolving selectors)

串并转换的方式与并串转换相反

时钟数据恢复

时钟数据恢复是通过PLL去同步一个和生成输入串行数据流的时钟频率相匹配的时钟

2.2 Serdes技术

serdes技术功能可简化成下图,serdes发送端将并行数据转换成串行数据进行传输,接收端的serdes将串行数据再转换成并行数据给内部芯片处理

serde根据架构区分主要有4类:并行时钟serdes,8b/10bserdes,内嵌式时钟bits serdes,bit交叉serdes。

并行时钟serdes结构如下图

8b/10bserdes结构

内嵌式时钟bits serdes结构

bit交叉serdes结构

四种架构的优劣对比如下表

三、 Xilinx GT

GT(Gigabit Transceiver)是吉比特收发器,更熟知的叫法是高速收发器,用于实现高速,低延时的串行信号传输,本质上是Serdes技术。

Xilinx的不同系列器件有对应支持的GT,功能上的最大差异点是支持的速率不同。

3.1 7系列器件GT

下图显示了不同器件含有的GT类型(GTP/GTX/GTH/GTZ)与对应的数量

3.2 Ultrascale GT

下图显示了Ultrascale系列不同器件含有的GT类型(GTP/GTX/GTH/GTZ)与对应的数量

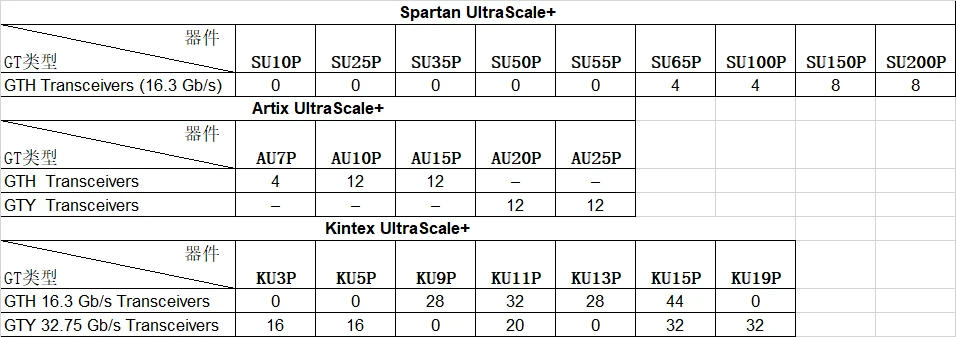

3.3 Ultrascale+ GT

四、参考资料

1、《SerDes_Architectures_and_Applications.pdf》

2、https://www.amd.com/zh-cn/search/site-search.html#q=iserdes