1.电路图搭建

图1

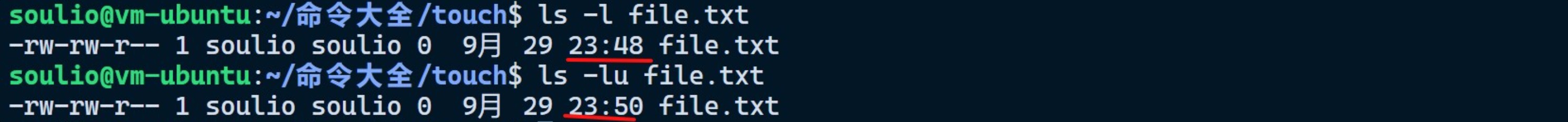

上面那层不能直接一横直接连过来,图2只能这样连。但是,图2的M1和M0的电压已经超过了VDD的1.8V。是不行的,需要调整,主要增大M1和M0的宽长比以减小电压。

图2 candance电流镜OTA电路实现

下面这篇文章讲了电流镜VDSsat一般在150mv,但是我现在的M0的VDsat如图3所示670mv。M3的VDsat是图4所示277mv。

电流镜,运放,比较器等管子的尺寸选取,静态分析,Vdsat和mismatch的关系_运放输入管的vds大小-CSDN博客

图3 M0的VDsat

图4 M3的VDsat

经过调整M1和M0的宽长比为32倍,M2和M3的宽长比为8倍,M5和M6的宽长比为8倍变成了图5。(这是手工设置的,为什么这么给还没找到说明的理由)调整的时候要都保证所有的管子都是在region——>2(饱和区)。

图5 电流镜OTA电路实现改进

图5中所有的电流源都是理想的,不行,需要改成电流镜复制的电流。

图6 按照一般规律改动的电路

但此时查看各个管子工作状态的时候发现M12这个PMOS的工作状态是在region——>1(线性区) ,所以要降低宽长比。

图7 在图6中M12的工作状态

首先进行控制变量法调控M14:M13:M12的比例发现——M12的长宽高比例越大,VGS-VTH的值就越小,就越容易饱和。

注意:“candance中PMOS最大的长度是100u”。

最终将M14的长宽高比例调为15000n:500n,,M11、M13的长宽高比例调为45000n:500n,M12的长宽高比例调为90000n:500n,最终实现所有的管子都在饱和区工作。

图8 最终结构与配置比

图9 M12的饱和区工作状态

![[Redis][典型运用][分布式锁]详细讲解](https://i-blog.csdnimg.cn/direct/34782f1d7f3943e0a37c17f393c24d4f.png)