文章目录

- 前言

- 一、ISERDESE2

- 1.1、ISERDESE2端口信号

- 1.1、ISERDESE2参数

- 二、BITSLIP-位滑动

- 2.1、BITSLIP作用

- 2.2、BITSLIP使用

- 2.3、BITSLIP示例

前言

上文对OSERDESE进行了详细介绍并且进行了仿真分析,本文开始对ISERDES进行介绍,

一、ISERDESE2

不难理解,与OSERDESE相反,ISERDESE2实现串并转换的模块。ISERDESE2框图如下:

1.1、ISERDESE2端口信号

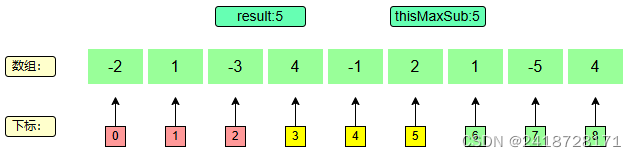

- Q1-Q8:并行输出数据,其中Q8是最先输入的串行数据位,如下图所示。一个ISERDESE2块最多输出8位并行数据,在DDR双沿采样模式下,两个ISERDESE2块级联可以输出10位和14位并行数据。

- O:该端口直接连接到串行输入的几个端口,并没有经过ISERDESE2核心逻辑,可以把D或DDLY的数据直接输出。

- SHIFTIN1、SHIFTIN2、SHIFTOUT1、SHIFTOUT2 :与OSERDESE2中该信号的原理一致,都是在两个OSERDESE2级联的时候,把从OSERDESE2的SHIFTOUT与主OSERDESE2的SHIFTIN连接。

- OFB:ISERDESE2的输入可以来自FPGA的管脚,即D端输入信号。也可以来自IDELAYE2的输出,即DDLY端口作为输入。还可以来自OSERDESE2的输出,即OFB作为输入,与OSERDESE2连接方式如下所示,两个器件的OFB信号相连即可。ISERDESE2与OSERDESE2连接时需要添加“OFB_USED = TRUE ”属性,并且ISERDESE2和OSERDESE2的DATA_RATE、DATA_WIDTH参数必须设置一致。

- CLK:高速时钟输入CLK,与串行数据流对齐。

- CLKB:辅助时钟输入CLKB,在MEMORY_QDR模式下,CLKB应连接到唯一的相移时钟,其余模式下,CLKB连接到CLK取反信号。

- CLKDIV:分频时钟CLKDIV,用于驱动串并转换器、Bitslip子模块和CE模块的输出,与输出的并行数据对齐。在SDR模式下,如果输出的X位并行数据,那么CLKDIV的频率是CLK频率的1/X,如果是DDR模式,则CLKDIV的频率是CLK频率的2/X。

注: 手册要求CLK和CLKDIV的相位必须对齐,一般推荐两种连接方式,一种如下所示,时钟输入管脚通过BUFIO之后直接作为串行输入数据的时钟信号,BUFIO优点就是路径短,延时小,缺点就是只能驱动当前时钟区域的IDDR和ISERDESE2的时钟管脚。而并行时钟需要通过BUFR进行分频,分频系数根据并行数据位宽和工作模式确定。另一种就是通过同一个MMCM产生CLK和CLKDIV两路时钟信号,这种方式更常用。原因是BUFIO和BUFR需要用户提供高频串行时钟,如果需要几百M的串行时钟,显然用户的外部晶振一般是无法提供的。

- CE1、CE2:时钟使能CE1和CE2,与参数NUM_CE的值有关。当NUM_CE为1时,使用CE1作为时钟使能信号。当NUM_CE为2时,当CLK_DIV为低电平时,CE2作为时钟使能信号,当CLK_DIV为高电平时,CE1作为时钟使能信号,对应真值表如下图所示。

- BITSLIP:高电平时执行与CLKDIV同步的移位操作。

- RST:复位信号,高电平有效,推荐退出复位时间与CLKDIV同步。

- OCLK:过采样模式时钟仅当INTERFACE_TYPE设置不为NETWORKING,才会使用OCLK时钟。

- CLKDIVP:MIG控制器专属

- DYNCLKDIVSEL、DYNCLKSEL:动态选择CLKDIV、CLK、CLKB

1.1、ISERDESE2参数

-

DATA_RATE:设置ISERDESE2工作模式,可选择单沿工作模式(SDR)和双沿工作模式(DDR),默认DDR模式。

-

DATA_WIDTH:设置输出并行数据位宽,取决于DATA_RATE和INTERFACE_TYPE的设置。如下图所示,SDR模式下可以设置为2、3、4、5、6、7、8。DDR模式下单个ISERDESE2块只能设置为4、6、8,两个ISERDESE2块级联可以设置为10、14。

-

INTERFACE_TYPE:决定ISERDESE2是配置为内存模式还是网络模式。可选的值有MEMORY、MEMORY_DDR3、MEMORY_QDR、OVERSAMPLE、NETWORKING,默认模式是MEMORY,常用NETWORKING模式。

-

DYN_CLKDIV_INV_EN:动态调整CLKDIV

-

DYN_CLK_INV_EN:动态调整CLK

-

INIT_Q1-Q4:设置第n个采样寄存器的初始值

-

SRVAL_Q1-Q4:设置复位第n个采样寄存器后的值。

-

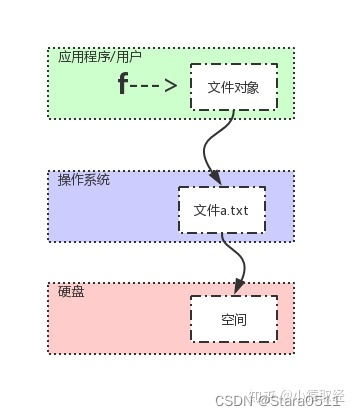

IOBDELAY:D和DDLY都是ISERDESE2的专用输入,D直接连接到IOB(直接与管脚相连),DDLY直接连接到IDELAYE2(在ISERDESE2和管脚之间有IDELAYE2加入延迟)。允许用户把延迟或非延迟的外部管脚输入信号作为ISERDESE2输入,通过参数IOBDELAY确定D和DDLY哪个作为ISERDESE2的输入,下图是IOBDELAY参数与输入信号的关系,经常设置位NONE,将外部管脚信号作为ISERDESE2串行数据输入。

-

NUM_CE:定义使用的时钟使能(CE1和CE2)数量,可设为1和2(默认值为2)。

-

OFB_USED:使能从OSERDESE2的OFB引脚到ISERDESE2 OFB引脚的路径,禁用外部管脚输入D和IDELAYE2的输入DLY。

-

SERDES_MODE:SERDES_MODE确定哪个是主ISERDESE2,哪个是从ISERDESE2。

二、BITSLIP-位滑动

2.1、BITSLIP作用

在串并转化的过程当中,这个信号就是进行校准的关键信号,如果没有这个信号,那么ISERDESE2的输出数据其实没有意义,很大可能是错误的,和之前在GT当中所描述的类似,在串并转换的过程中,我们需要知道从串行数据的哪里开始进行串并转换才能够恢复出来正确的并行数据。

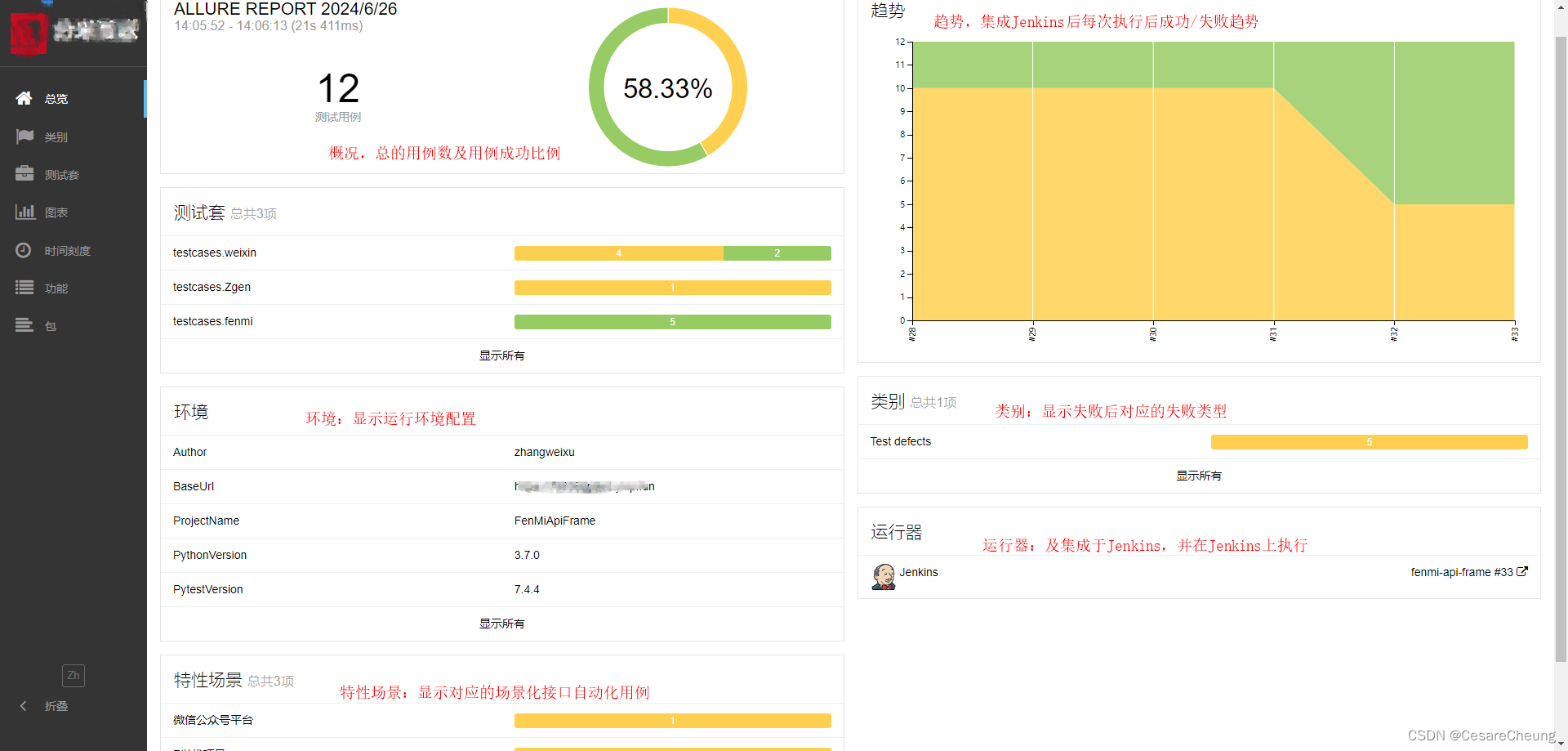

通过拉高ISERDESE2模块的Bitslip信号,输入的串行数据流在并行端重新排序,Bitslip与CLKDIV同步。下图说明了SDR和DDR模式下位滑移操作对数据采样的影响,ISERDESE2的数据宽度是八。在SDR模式下,每次Bitslip拉高都会导致输出数据左移一位。在DDR模式下,每次Bitslip拉高都会导致输出数据在右移1位和左移3位之间交替变化。

2.2、BITSLIP使用

在我们使用的时候,无需关心到底是怎么移动的,只需要观察串并转换结束后的数据是否为正确数据,不准确则拉高一次BITSLIP即可。只有当ISERDESE2处于网络模式(NETWORKING)下,位滑块(BITSLIP)才可用。Bitslip每次只能拉高一个CLKDIV周期,不能在两个CLKDIV周期内连续拉高Bitslip信号。

在SDR和DDR模式下,从ISERDESE2检测到Bitslip的高电平开始,到ISERDESE2把Bitslip移动后的数据输出到Q1–Q8引脚为止,延迟时间为两个CLKDIV周期。在分析接收到的数据模式并可能发出下一个Bitslip命令之前,用户逻辑应在SDR模式下等待至少两个CLKDIV周期,在DDR模式下等待至少三个CLKDIV周期。综上Bitslip拉高后,需要等待至少三个时钟周期,才能检测并行输出结果是否与预期一致,进而确定是否通过拉高Bitslip信号继续调整输出。与当初介绍64B66B的自定义PHY有点类似。

2.3、BITSLIP示例

以下图为例进行说明:

下图是4位并行数据的DDR模式下Bitslip的时序图,数据(D)重复的4位串行数据ABCD。ABCD可能以四种方式出现在ISERDESE2的Q1–Q4并行输出端:ABCD、BCDA、CDAB和DABC,只有ABCD才是正确的输出。拉高Bitslip信号选择所需的对齐方式(ABCD),下图显示了Bitslip的时序以及ISERDESE2并行输出Q1–Q4的校准时序。

- 时钟事件1:第一个并行信号CDAB已被采样到ISERDESE2的输入侧寄存器中。Bitslip引脚未断言;CDAB通过ISERDESE2传播而不进行任何重新排列。

- 时钟事件2:Bitslip引脚被断言,这导致Bitslip控制器内部将所有位向右移动一位。位滑在一个(只有一个)CLKDIV周期内保持高位。

- 时钟事件3:在断言Bitslip之后的三个CLKDIV周期,Bitslip操作完成,新的移位数据作为BCDA在输出上可用。

- 在时钟事件3之后:由于ISERDESE2配置为1:4,bitslip可以有效地断言最多两次。在第二次移位之后,(所需的)输出ABCD在Q4-Q1上可用。第三次移位(右一个位置)后,输出DABC在Q4-Q1上可用。在第四次移位(左三个位置)之后,原始输出CDAB在Q4-Q1上可用,并且Bitslip已经完成了通过所有四个输入组合的循环。

![[leetcode]insert-into-a-binary-search-tree](https://img-blog.csdnimg.cn/direct/e42854e6519b4c2caf3422ff48c63a28.png)