这段代码是RK3568芯片的设备树(Device Tree)片段,用于描述GPIO控制器的配置。

pinctrl: pinctrl {

compatible = "rockchip,rk3568-pinctrl"; // 兼容性字符串,指定此设备树节点适用于RK3568的引脚控制器

rockchip,grf = <&grf>; // 引用通用寄存器(GRF)

rockchip,pmu = <&pmugrf>; // 引用GPIO控制寄存器

#address-cells = <2>; // 指定地址长度的位数为32x2,也就是64位地址

#size-cells = <2>; // 指定每个地址的长度是32x2,也就是64位长度

ranges; // 指定地址映射范围

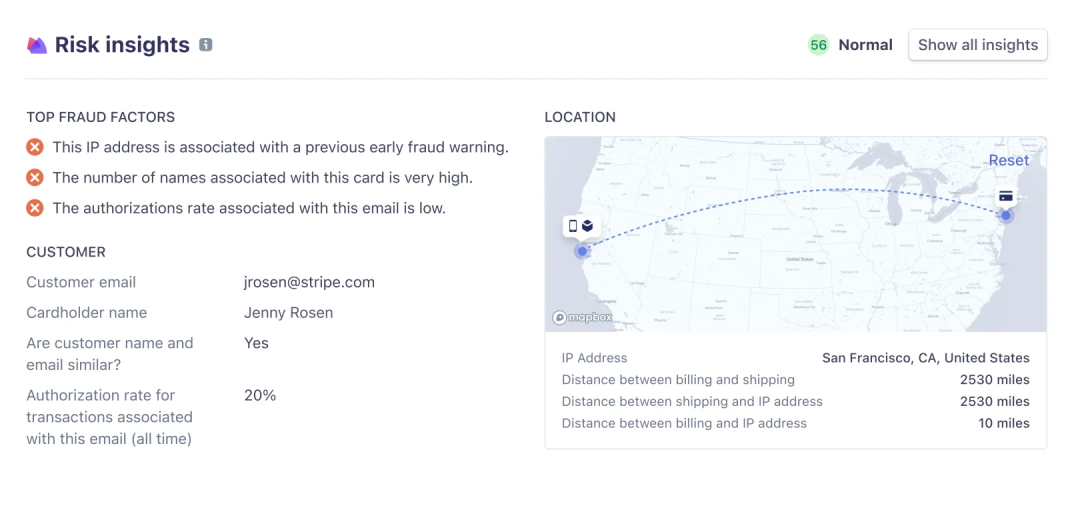

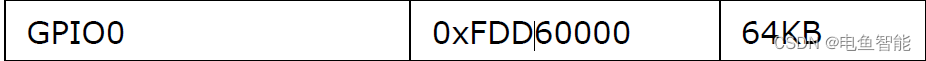

gpio0: gpio@fdd60000 { // GPIO控制器0的描述,0xfdd60000是GPIO0的起始地址,这是从RK3568TRM里面截图出来的信息,一一对应了。

compatible = "rockchip,gpio-bank"; // 兼容性字符串,指定这是Rockchip GPIO控制器,为了通配GPIO

reg = <0x0 0xfdd60000 0x0 0x100>; // 寄存器地址和大小

interrupts = <GIC_SPI 33 IRQ_TYPE_LEVEL_HIGH>; // 中断配置

clocks = <&pmucru PCLK_GPIO0>, <&pmucru DBCLK_GPIO0>; // 时钟源配置

gpio-controller; // 标识这是一个GPIO控制器

#gpio-cells = <2>; // 每个GPIO单元的属性位数(标识和偏移)

gpio-ranges = <&pinctrl 0 0 32>; // GPIO范围配置

interrupt-controller; // 标识这是一个中断控制器

#interrupt-cells = <2>; // 每个中断单元的属性位数

};

gpio1: gpio@fe740000 {

compatible = "rockchip,gpio-bank";

reg = <0x0 0xfe740000 0x0 0x100>;

interrupts = <GIC_SPI 34 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&cru PCLK_GPIO1>, <&cru DBCLK_GPIO1>;

gpio-controller;

#gpio-cells = <2>;

gpio-ranges = <&pinctrl 0 32 32>;

interrupt-controller;

#interrupt-cells = <2>;

};

gpio2: gpio@fe750000 {

compatible = "rockchip,gpio-bank";

reg = <0x0 0xfe750000 0x0 0x100>;

interrupts = <GIC_SPI 35 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&cru PCLK_GPIO2>, <&cru DBCLK_GPIO2>;

gpio-controller;

#gpio-cells = <2>;

gpio-ranges = <&pinctrl 0 64 32>;

interrupt-controller;

#interrupt-cells = <2>;

};

gpio3: gpio@fe760000 {

compatible = "rockchip,gpio-bank";

reg = <0x0 0xfe760000 0x0 0x100>;

interrupts = <GIC_SPI 36 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&cru PCLK_GPIO3>, <&cru DBCLK_GPIO3>;

gpio-controller;

#gpio-cells = <2>;

gpio-ranges = <&pinctrl 0 96 32>;

interrupt-controller;

#interrupt-cells = <2>;

};