来源:Influence of Structure Parameters on the RON,sp of Quasi-Vertical Power DMOS Compatible with 0.18μm BCD Process(ISPSD 24年)

摘要

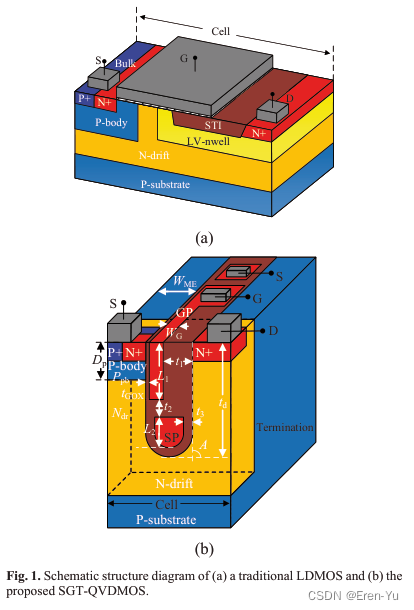

“Lateral double-diffused MOSFET (LDMOS)是应用于功率电子领域最常见的器件之一,得益于其可以实现高集成度的优势。然而,LDMOS的导通特性受到限制,是由于其存在抵抗大电压的横向漂移区域(lateral drift region)。为了进一步降低特定导通电阻(RON,sp),提出了一种新型的集成功率DMOS器件,即准垂直屏蔽栅沟槽结构(SGT-QVDMOS),它与双极型-CMOS-DMOS(BCD)工艺兼容。本文详细研究了关键结构参数对RON,sp的影响。通过优化器件结构,实现了超越硅材料极限的超低RON,sp性能。”

关键词:

- Quasi-vertical: 准垂直

- LDMOS: 横向双扩散MOSFET

- BCD process: 双极型-CMOS-DMOS工艺

- RON,sp: 特定导通电阻

文章的研究内容

论文主要研究了一种新型的功率器件——SGT-QVDMOS(Shielded Gate Trench Quasi-Vertical Double-diffused MOSFET),这种器件与传统的LDMOS(Lateral Double-diffused MOSFET)相比,在保持高集成度的同时,旨在降低特定导通电阻(RoN,sp)并提高功率器件的性能。

-

研究背景:传统的LDMOS由于其横向漂移区的存在,限制了其导电特性。为了提高功率转换系统的功率密度和效率,需要降低LDMOS的RoN,sp。

-

SGT-QVDMOS结构:提出了一种与0.18μm BCD(Bipolar-CMOS-DMOS)工艺兼容的SGT-QVDMOS结构。这种结构通过引入一个不对称的栅槽和分裂的栅极(SP),将横向长漂移结构折叠成准垂直结构,从而实现更小的单元间距。

-

性能优化:通过调整关键结构参数,如尺寸和掺杂浓度,来优化SGT-QVDMOS的RoN,sp和阻断电压(BV)。研究了这些参数对RoN,sp和BV的影响,包括栅槽的角度、栅极的厚度、SP的高度、漂移区的掺杂浓度等。

-

模拟与实验验证:使用TCAD模拟来研究结构参数对RoN,sp和BV的影响,并制造了基于0.18μm BCD工艺的SGT-QVDMOS样品,通过实验验证了模拟结果。

-

性能比较:将SGT-QVDMOS与传统的LDMOS以及已发表的LDMOS器件进行了性能比较,展示了SGT-QVDMOS在降低RoN,sp方面的潜力。

-

结论:SGT-QVDMOS通过其新颖的结构设计,在理论上实现了比硅极限低51%的RoN,sp。通过优化关键结构参数,可以在保持高BV的同时,实现低RoN,sp。

-

参考文献:文档列出了一系列与功率半导体器件相关的参考文献,包括智能功率集成、高电压集成电路技术、功率半导体器件基础等。

文章的研究方法

论文提供了SGT-QVDMOS的详细研究,包括其设计、模拟、制造和性能测试,以及与传统LDMOS的比较,展示了其在功率电子领域的应用潜力。

根据提供的文档内容,研究方法主要包括以下几个步骤:

-

理论设计:首先,研究者提出了一种新型的SGT-QVDMOS结构,这种结构与传统的LDMOS不同,通过引入准垂直的漂移区和屏蔽栅槽(SGT)来改进器件的性能。

-

参数定义:定义了SGT-QVDMOS的关键结构参数,包括单元间距、栅槽宽度、栅极宽度、氧化层厚度、体区域深度和掺杂浓度等,这些参数对器件的性能有直接影响。

-

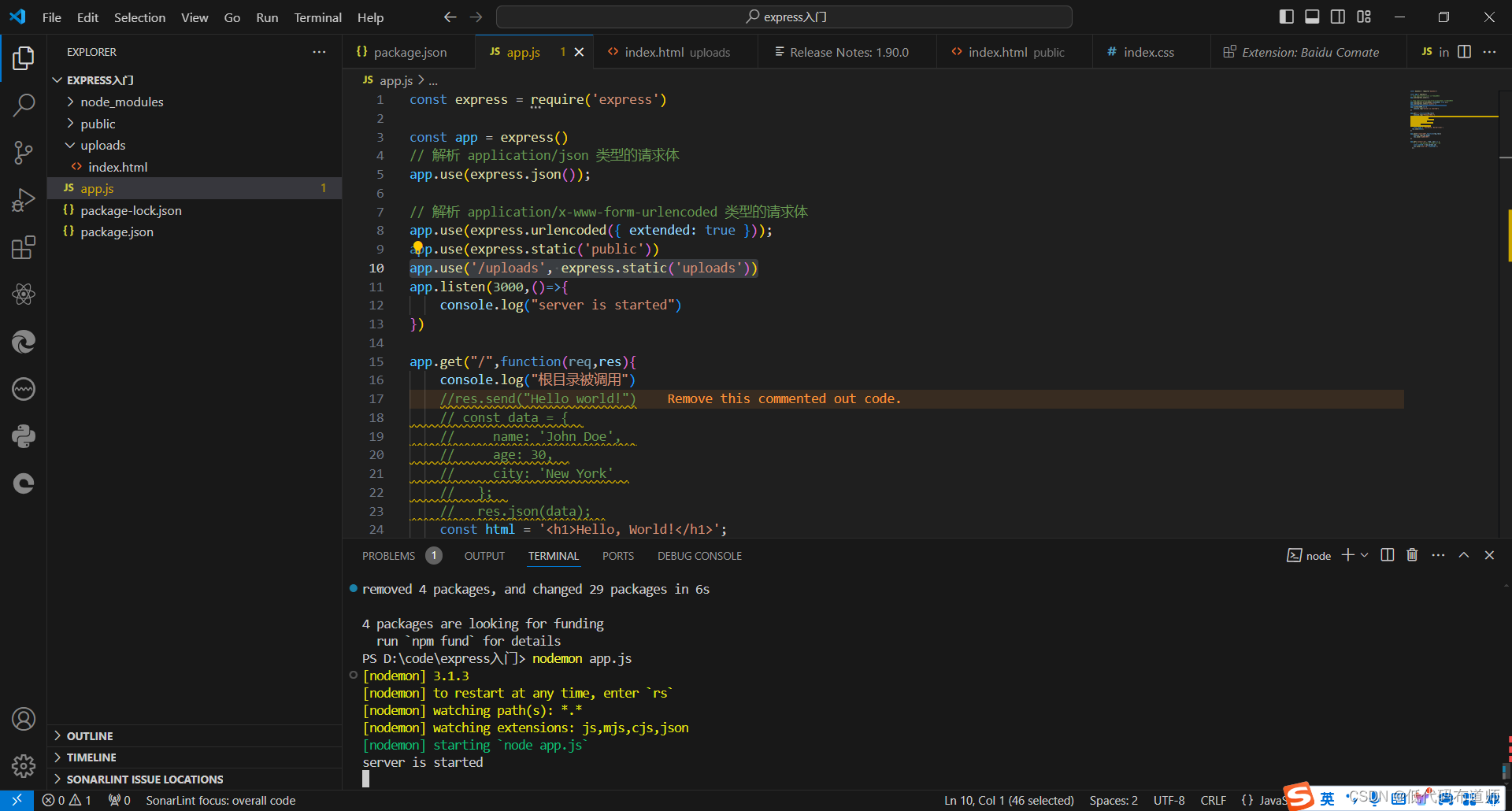

TCAD模拟:使用Technology Computer Aided Design(TCAD)软件进行模拟,研究了关键结构参数对SGT-QVDMOS的导通电阻(RoN,sp)和阻断电压(BV)的影响。模拟结果用于预测和优化器件的性能。

-

制造样品:基于0.18μm BCD工艺,制造了SGT-QVDMOS样品,以验证模拟结果和理论设计的可行性。

-

实验测试:对制造的SGT-QVDMOS样品进行了电性能测试,包括正向输出特性和阻断特性的测量,以验证模拟结果的准确性。

-

数据分析:对模拟和实验数据进行了详细分析,以评估SGT-QVDMOS的性能,并与传统LDMOS和已发表的LDMOS器件进行了性能比较。

-

优化调整:根据模拟和实验结果,对SGT-QVDMOS的结构参数进行了优化调整,以实现更低的RoN,sp和更高的BV。

-

结果验证:通过比较模拟和实验数据,验证了SGT-QVDMOS的性能,并确认了其在降低RoN,sp方面的潜力。

-

撰写论文:最后,研究者将研究结果整理成论文,包括研究背景、方法、结果和结论,并提供了参考文献以供进一步研究。

整个研究方法是一个系统性的过程,从理论设计到模拟、样品制造、实验测试,再到数据分析和优化,最终得出结论。这种方法确保了研究结果的可靠性和实用性。

文章的创新点

根据提供的文档内容,SGT-QVDMOS(Shielded Gate Trench Quasi-Vertical Double-diffused MOSFET)的研究具有以下创新点:

-

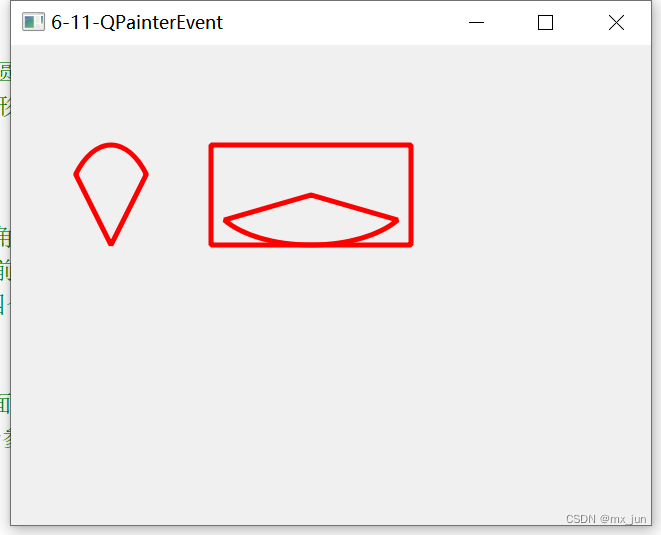

新型结构设计:提出了一种新的SGT-QVDMOS结构,这种结构通过引入准垂直的漂移区和屏蔽栅槽(SGT),与传统的LDMOS相比,能够在保持高阻断电压(BV)的同时降低特定导通电阻(RoN,sp)。

-

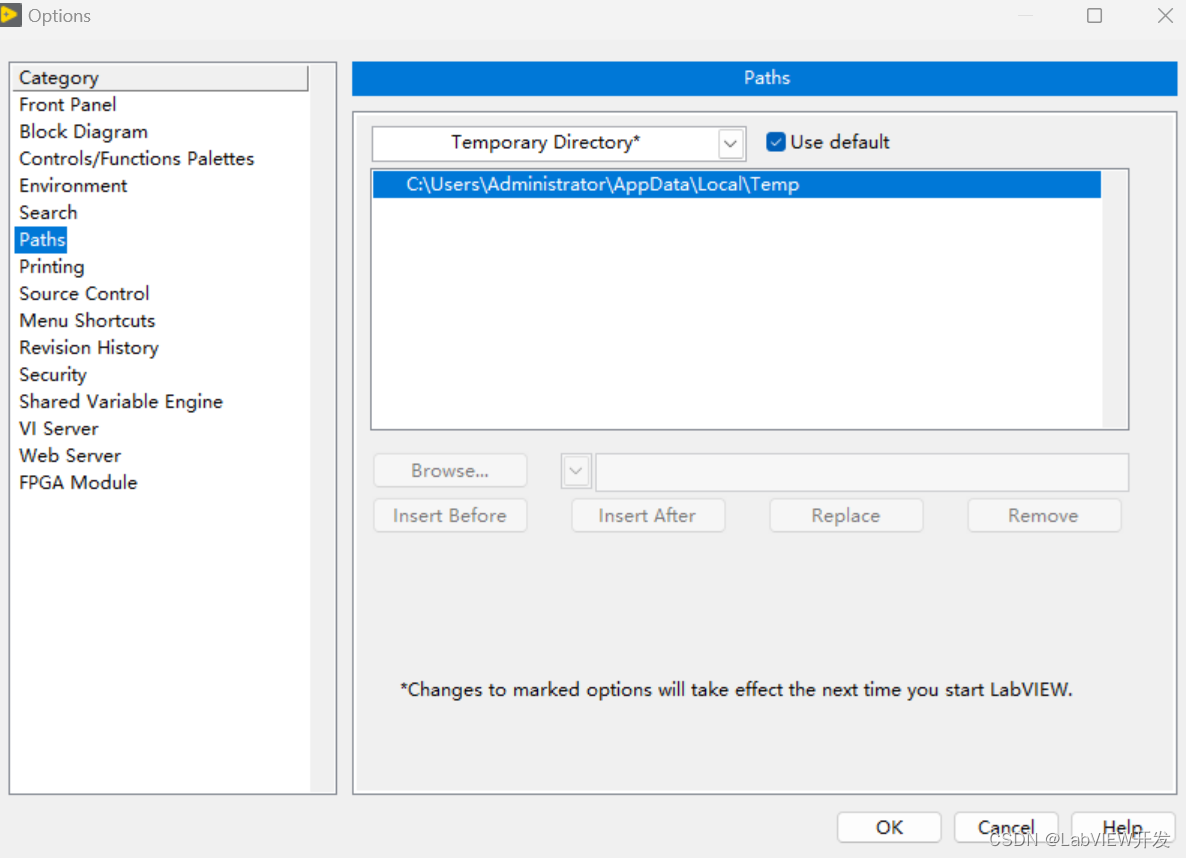

兼容现有工艺:SGT-QVDMOS与现有的0.18μm BCD(Bipolar-CMOS-DMOS)工艺兼容,这意味着它可以在现有的制造流程中实现,无需对生产线进行大规模改造。

-

关键参数优化:研究了影响SGT-QVDMOS性能的关键结构参数,如栅槽角度、栅极厚度、SP(Split Polysilicon)高度、漂移区掺杂浓度等,并通过优化这些参数实现了性能的显著提升。

-

低RoN,sp实现:通过结构和参数的优化,SGT-QVDMOS在理论上实现了比硅极限低51%的RoN,sp,这是一个显著的性能提升,有助于提高功率转换效率。

-

高阻断电压保持:在降低RoN,sp的同时,SGT-QVDMOS还能够保持较高的阻断电压,这对于功率器件在高压应用中的可靠性至关重要。

-

RESURF效应应用:利用SP引入的电荷平衡效应和RESURF(Reduced Surface Field)技术,减少了漂移区的电阻,进一步提高了器件的性能。

-

实验验证:通过制造样品并进行实验测试,验证了模拟结果的准确性,确保了理论设计到实际应用的可行性。

-

性能比较:将SGT-QVDMOS与传统LDMOS以及其他已发表的LDMOS器件进行了性能比较,展示了SGT-QVDMOS在降低RoN,sp方面的显著优势。

-

高集成度:SGT-QVDMOS的设计允许在保持高集成度的同时实现高性能,这对于智能功率集成电路的发展具有重要意义。

这些创新点展示了SGT-QVDMOS在功率电子领域的应用潜力,特别是在需要高效率和高功率密度的场合。通过这些创新,SGT-QVDMOS有望成为未来功率电子设计中的一个有吸引力的选项。

文章的结论

根据提供的文件内容,以下是SGT-QVDMOS研究文章的主要结论:

-

新型结构优势:SGT-QVDMOS通过引入准垂直的漂移区和屏蔽栅槽(SGT)结构,成功地将传统的横向漂移结构转换为更紧凑的准垂直结构,从而在保持高阻断电压(BV)的同时,显著降低了特定导通电阻(RoN,sp)。

-

性能提升:通过优化关键结构参数,SGT-QVDMOS在理论上实现了比硅极限低51%的RoN,sp,这一结果通过TCAD模拟和实验测试得到了验证。

-

工艺兼容性:SGT-QVDMOS的设计兼容0.18μm BCD工艺,这表明它可以在现有的半导体制造流程中实现,有助于快速推广应用。

-

电性能验证:制造的SGT-QVDMOS样品在实验中显示出了优异的正向导通和阻断特性,与模拟结果一致,证明了设计的可靠性。

-

性能比较:与已发表的LDMOS器件相比,SGT-QVDMOS在降低RoN,sp方面取得了显著的进步,同时保持了较高的BV,这在功率电子领域是一个重要的突破。

-

关键参数影响:研究详细分析了关键结构参数对SGT-QVDMOS性能的影响,包括栅槽角度、栅极厚度、SP高度、漂移区掺杂浓度等,为进一步的优化提供了指导。

-

创新贡献:SGT-QVDMOS的设计和实现为功率MOSFET技术提供了新的发展方向,特别是在提高功率密度和效率方面。

-

未来应用前景:SGT-QVDMOS的研究成果预示着其在汽车、消费电子、工业和其他领域的智能功率集成电路中的潜在应用,有助于推动相关技术的发展。

这些结论突出了SGT-QVDMOS在功率电子器件领域的创新性和潜在应用价值,同时也展示了通过结构和工艺优化实现性能提升的可能性。