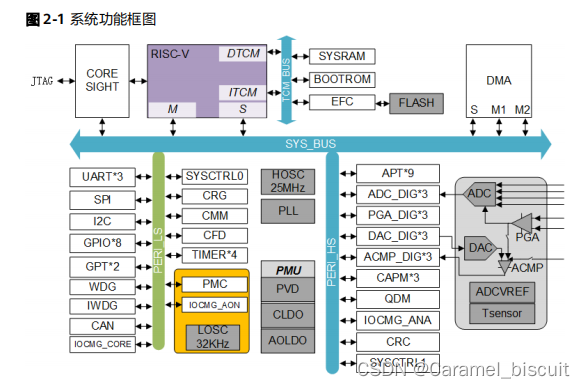

306xH系列产品基于高性能RISC-V CPU核,工作频率最高到200MHz,集成了FPU浮点处理单元,支持浮点乘法,支持浮点乘法,除法和开方等复杂数学运算指令,支持16KB的SRAM和最高160KB的flash存储单元。

该MCU集成最多9组高级PWM定时器,最多可支持两路独立电机PWM控制和两路PFC控制应用。内置最多3个12bit ADC(2MSPS,最多23通道),3个8bitDAC,1个编码器,3个比较器和3个PGA放大器。最多支持1个SPI,3个UART,1个I2C等通讯接口,2个看门狗模块,3个基本timer,1个系统timer,支持多达52个通用GPIO管脚。

系统

MCU集成高性能RISC-V CPU内核,可针对片上闪存或SYSRAM运行的浮点或定点程序提供高达200MHz的信号处理能力。内部集成高性能模拟模块,并与处理单元和APT模块紧密耦合,支持更好的实时信号链连接,还提供了多个管脚复用选项,可实现灵活的单板布局。芯片能够应用于众多场景,如消费类、工业类或IOT类。

嵌入式闪存(eFLASH)

提供高达160KB的嵌入式闪存,可以用于程序与数据的存储。

提供保护机制控制不同的操作源对4个分区读/编程/擦除权限,提供2个保护状态控制。

- protection_level 1:无特殊保护。

- protection_level 0:调试接口部分区域无法操作。

- 支持XIP。

- 支持指令执行加速。

- 支持错误码纠错能力:纠一检二。

电源控制(PMC)

PMC(Power Manage Controller)通过对芯片内部电源的管理,实现芯片的上/下电时序、开/关机功能和低功耗模式切换。

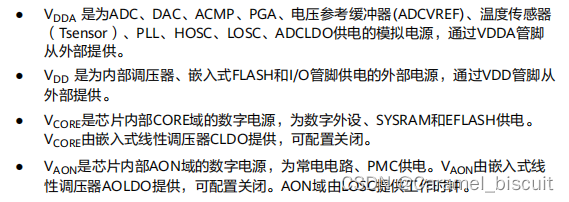

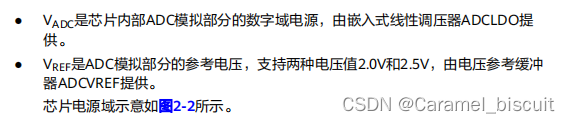

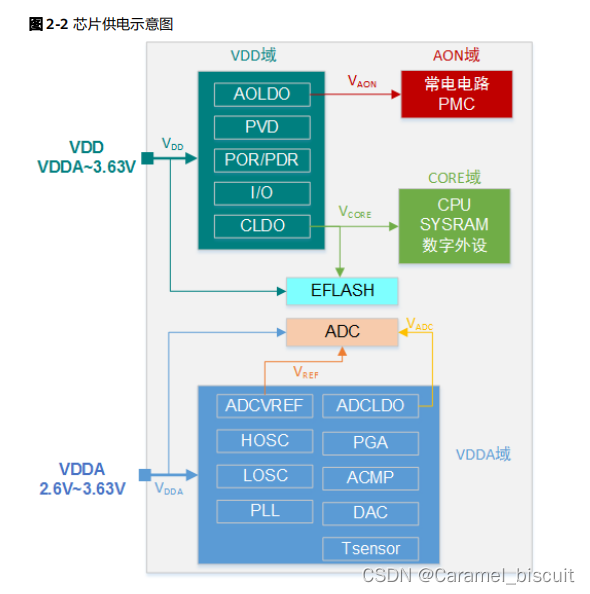

供电方案

芯片支持的工作电压范围为2.6V~3.6V。针对特定外设,芯片提供了几种不同的电源:

电源监控

上电复位(POR)/掉电复位(PDR)

芯片具有一个集成的上电复位(POR)/掉电复位(PDR),在所有功耗模式下都有效。上电期间,POR将使芯片保持复位状态,直到VDD电源电压达到POR阈值。此时,将释放芯片复位信号并使能AOLOD,并唤醒CLDO,系统可以启动。在掉电期间,VDD电源电压降至PDR阈值时,芯片再次被置于复位状态。

可编程电压检测器(PVD)

可以使用PVD监视VDD电源电压,当VDD降至PVD下降沿阈值以下或者当VDD上升到PVD上升沿阈值以上时,可以产生PVD输出中断。该功能的用处之一是可以在中断服务程序中执行紧急关闭系统的任务。

低功耗模式

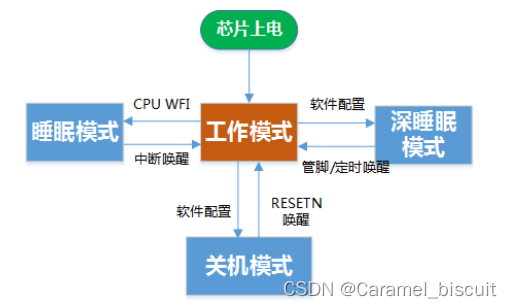

默认情况下,系统复位或上电复位后,芯片进入工作模式。系统提供了多个低功耗模式,可在CPU不需要运行时节省功耗。由用户根据应用选择具体的低功耗模式,以在低功耗、短启动时间和可用唤醒源之间寻求最佳平衡。芯片有三种低功耗模式:

- 睡眠模式:CPU时钟关闭,但所有外设都可以运行,并在发生中断时唤醒CPU。

- 深睡眠模式:CLDO关闭,VCORE域断电。此时,VCORE域中的时钟都会停止,PLL、HOSC和XTAL振荡器被禁止。仅AONLDO保持开启,LOSC正常运行,为VAON域提供工作时钟。

- 关机模式:CLDO和AOLDO都关闭,域和VAON域断电。芯片所有时钟都会停止。

此外还可以通过以下方法降低工作模式下的功耗:

- 降低系统时钟频率。

- 不适用某外设时,关闭其时钟。

时钟复位生成(CRG)

CRG(clock &/芯片有5种类型的复位源:电源复位、管脚复位、电压监控复位、看门狗复位、软件复位。)

源时钟用于衍生芯片各模块所需的时钟。芯片共有三个源时钟资源:HOSC、LOSC、XTAL。

- HOSC:HOSC是芯片集成的高精度高速振荡器,提供25MHz的时钟clk_hosc。clk_hosc是芯片CORE电源域的默认时钟。

- LOSC:LOSC是芯片集成的低速振荡器,提供32kHz时钟的clk_losc。clk_losc是芯片AON电源域的默认时钟,也为IWDOG模块提供计数时钟。

- XTAL:支持高速外部晶体或外部时钟源,提供2~30MHz时钟clk_xtal。

衍生时钟为芯片内部各模块提供工作时钟,主要有以下时钟资源:

- clk_hs:clk_hs为系统主工作时钟,最大支持200MHz,为CPU、SYSRAM、高速外设以及总线SYS_BUS和PERI_HS提供时钟。

- clk_ls:是clk_hs的二分频时钟,为系统低速外设总线PERI_LS提供时钟,也为低速外设提供时钟。还有部分低速外设可以选择clk_ls的2/4/8分频作为其工作时钟。

- clk_adc:为ADC模拟部分工作时钟,最大支持40MHz。

- clk_dac:为DAC模拟部分工作时钟,最大支持10MHz。

时钟失效检测(CFD)

CFD(Clock Failure Detector)时钟失效检测模块用于检测PLL的参考时钟是否失效。

CFD使用参考时钟(clk_losc)对目标时钟(clk_pll_ref)的2048分频时钟进行计数。

在每个目标时钟周期开始时(也就是上一个周期结束时),清零计数器。每个参考时钟(clk_losc),计数值CFDCNT递增。在每个目标时钟周期结束时,保存此时计数值CFDCNT到CFDNTLOCK中,表示本次检测结束。

如此循环往复,直到CFDNTLOCK>CFDWDHO,超过检测窗口上限。此时CFD上报时钟中断失效clk_fail_int,停止计数,输出clak_fail硬件信号给CRG和APT08的系统事件2.CRG自动执行主时钟保护,也就是将系统主时钟切换到clk_losc,主频32kHz。APT08根据配置的系统事件2保护动作,执行输出保护。

CFD模块有以下特性:

- 支持检测PLL参考时钟是否失效。

- 支持检测到失效后自动保护。

- 支持检测到失效后产生系统事件输出到APT。

时钟监测模块(CMM)

CMM(Clock Monitor Module)时钟监测模块,使用参考时钟来监测目标时钟的频率,功能是检测时钟频率是否偏移。

CMM使用参考时钟对目标时钟计数。在每个目标时钟的周期开始时,清零计数值。每个参考时钟,计数值CMCNT递增。在每个目标时钟的周期结束时,保存此时计数值到CMCNTLOCK中,表示本次检测结束,如此循环往复。

CMM模块有以下特性:

- 支持参考时钟4选1。

- 支持参考时钟最大32分频。

- 支持目标时钟5选1。

- 支持目标时钟最大8192分频。

I/O复用控制(IOCMG)

IOCMG(I/O control & Multiplex Generater)实现对芯片I/O管脚的状态控制和功能复用管理。除特殊说明外,所有I/O管脚默认为GPIO输入功能。

IOCMG能够为I/O管脚提供以下可配置特性:

- 上/下拉

- 斯密特输入开/关

- 输出驱动能力

- 输出信号边沿快/慢

- 数字/模拟模式切换

- 复用功能选择

通过I/O(GPIO)

本系统支持8组GPIO控制器,即GPIO0~GPIO7。每组GPIO控制器提供8个可编程的GPIO。

每个GPIO可以独立配置为输入或输出,输入和输出的电平状态均可以通过寄存器读出。作为输入GPIO时,可作为中断源,中断触发类型可以配置为高电平/低电平/上升沿/下降沿/双沿触发;作为输出GPIO时,每个GPIO都可以独立地清0或置1。

系统配置控制器(SYSCFG)

系统控制器SYSCTRL(System Controller)包含一组配置寄存器,其主要用途如下:

- 为系统关键寄存器提供写保护控制。

- 系统复位事件次数统计。

- 触发系统软件复位和软件中断。

- 系统状态查询。

- APT同步启动与管脚事件数字滤波配置。

- DMA请求线源选择配置。

- Tensor使能配置。

- ADCVREF配置。

直接存储器访问控制器(DMA)

DMA(Direct Memory Access)是一种高速的数据传输操作,不通过CPU,在外设和存储器之间直接进行数据传输。

DMA控制器(DMAC)直接在存储器和外设、外设和外设、存储器和存储器之间进行数据传输,减轻CPU的负担并减少了CPU中断处理开销。

DMA控制器有以下特性:

- 支持8bit、16bit、32bit数据位宽传输。

- 支持4个DMA通道,每个通道可配置用于一种单向传输。

- 提供2个位宽为32bit的Master总线接口用于数据传输。

- 支持软件控制的DMA请求。

- 支持Brust传输,Brust长度可配。

- 支持源地址和目的地址可配置为自动递增或不递增。

- 支持链表模式。

- 支持DMAC流控和外设流控。

循环冗余校验计算单元(CRC)

本系统提供1个CRC模块。CRC是循环冗余校验计算单元的简称,支持4种算法多项式可配,可以被使用以产生CRC码值。

CRC校验通常用来校验数据传输或者存储过程的完整性,是数据通信领域最常用的一种差错校验码。

信号捕获模块(CAPM)

CAPM(Capture Module)捕获模块用于捕获芯片管脚输入信号的边沿,记录边沿对应的时间戳,可用于通用数字信号捕获场景,也可实现电机专用场景,如:霍尔传感器,PWM波通信等应用。

CAPM模块有以下特性:

- 支持3通道捕获(CAPM0,CAPM1,CAPM2)。

- 支持输入滤波(支持过滤毛刺宽度18192个时钟周期),输入预分频(2510偶数分频)。

- 支持输入电平实时检测。

- 支持边沿计数,支持边沿数量比较。

- 支持32比特时间计数,支持计数分频。

- 支持单个CAPM通道捕获最多4个捕获事件,保存最多4个捕获事件时间戳,支持捕获溢出检测。

- 支持循环捕获,单轮次捕获。

- 支持时间计数相位同步,APT硬件同步,软件同步。

正交解码器解码模块(QDM)

QDM(Quadrature Decoder Module)用于对接增量解码器,针对增量解码器输出的A/B/Z三相信号进行解码,记录位置信息,方向信息和时间信息。QDM内部集成了正交解码单元QDU,位置处理单元PPU,时间戳单元TSU,周期触发单元PTU,实现了多种类型的增量编码器解码,支持1X/2X/4X倍频解码,支持位置计数的多种校准模式、初始化模式、锁存模式,可编程的位置区间内计时,可编程的时间区间内计数位置,A/B相信号看门狗等功能。用于绝对位置记录,相对位置记录,旋转速度计算等应用场景。

高级PWM定时器(APT)

APT(Advanced PWM Timer)高级PWM(Pulse Width Modulation)定时器可以产生PWM波形,广泛应用于数字电机控制、开关电源控制等领域。可以使用APT模块产生PWM波去控制开关器件导通和关断,并可以实现0~100%范围可编程占空比,支持产生带死区(死区时长可编程)的互补PWM波。

通用PWM定时器(GPT)

GPT(General PWM Timer)通用PWM(Pulse Width Modulation)定时器可以产生一路PWM波。

基本定时器(TIMER)

Timer模块主要实现定时、计数功能,可以供程序用作定时和计数。其中timer0/timer1/timer2为基本timer,timer3位系统timer。

看门狗(WDT)

本系统提供2个看门狗模块,分为WDG和IWDG。

- WDG基于总线时钟进行计数,计数支持分频。内部32bit减法计数器自由计数,支持超时时间间隔可配置,支持寄存器锁定,支持超时中断和复位信号产生,并在调试模式下自动停止计数。

- IWDG基于内部LOSC时钟进行计数,计数不支持分频,除此之外行为与WDG一致。

看门狗用于在系统异常情况下,一定时间内发出中断/复位信号,防止芯片挂死。

集成电路接口(I2C)

本系统提供1个I2C master接口,用于对I2C总线上连接的从设备的读写访问。

通用异步收发传输器(UART)

UART是一个异步串行的通信接口,主要功能是和外围设备的UART进行对接,从而实现设备间的通信。

本系统提供3个UART控制器,其中UART0/2为2线UART,UART1为4线UART,支持硬件流控。

同步串行外设接口(SPI)

SPI控制器实现数据的串并、并串转换,可以作为Master与外部设备进行同步串行通信,也可作为Slave与外设对接。支持Motorola SPI接口,TI串行同步接口和MicroWire接口三种外设接口协议。

CAN控制器

控制器域网CAN(Controller Area Network)是国际上应用最广泛的现场总线之一,具有高性能、高可靠性、高实时性的特点。芯片中CAN控制器支持持CAN Protocol Version 2.0 part A, B。

模数转换器(ADC)

ADC模块实现模拟信号到数字信号的转换,采用逐次逼近形ADC(successive approximation ADC,SARADC)。ADC支持12bit采样精度,最多有16个采样通道。支持单次采样模式和连续采样模式,支持软件过采样,支持两通道同步采样。

可编程增益放大器(PGA)

PGA(Programmable Gain Amplifier)是A/D转换器的高性能模拟前端,该放大器具有失调校准和输入数据选择功能。

PGA集成多个内部增益选项,用于调整宽范围的输入电压信号,使A/D转换器满量程信号达到均一化,提高测量精度。

数模转换器(DAC)

DAC将软件配置的8bit数字信号,转换成对应的模拟电压量,实现了数字到模拟的转换,转换成模拟信号后便可以进行模拟运算。

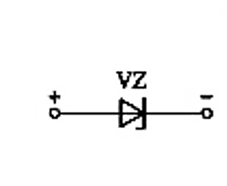

模拟比较器(ACMP)

ACMP为模拟电压比较器,选择两个输入源进行电压比较,ACMP的比较信号有三个来源,即管教输入,DAC输出或PGA输出。