关于 Arm Cortex M 系列内核的中断优先级

Cortex M 的中断和优先级

首先要区分开 中断 和 中断优先级 这是两个不同的东西, 不要搞混了

- 对于 Cortex-M0 和 Cortex-M0+ 内核, 除了系统内建中断外, 支持最多 32 个中断

- 对于 Cortex-M3 内核, 除了 16 个内核中断外, 支持最多 240 个中断

- 有8-bit的优先级, M0是固定的 2-bit, 即4个优先级, M3/M4 至少需要实现3-bit, 即大于等于8个优先级

厂商的实现

- STM32 F1 只使用了其中的 84个中断, 包括 16个内核中断和 68 个可屏蔽中断

- STM32 F1 实现了 4-bit 的优先级, 具有16级可编程的中断优先级.

- STM32F103系列, 只使用了60个可屏蔽中断

优先级的数值和优先级的关系

The most important fact to know is that Cortex-M uses the “reversed” priority numbering scheme for interrupts, where priority zero corresponds to the highest urgency interrupt and higher numerical values of priority correspond to lower urgency. This numbering scheme poses a constant threat of confusion

注意,Cortex-M 对中断优先级编号的方案, 数值是倒序的, 优先级0对应最高优先级, 数值越大对应的优先级越低.

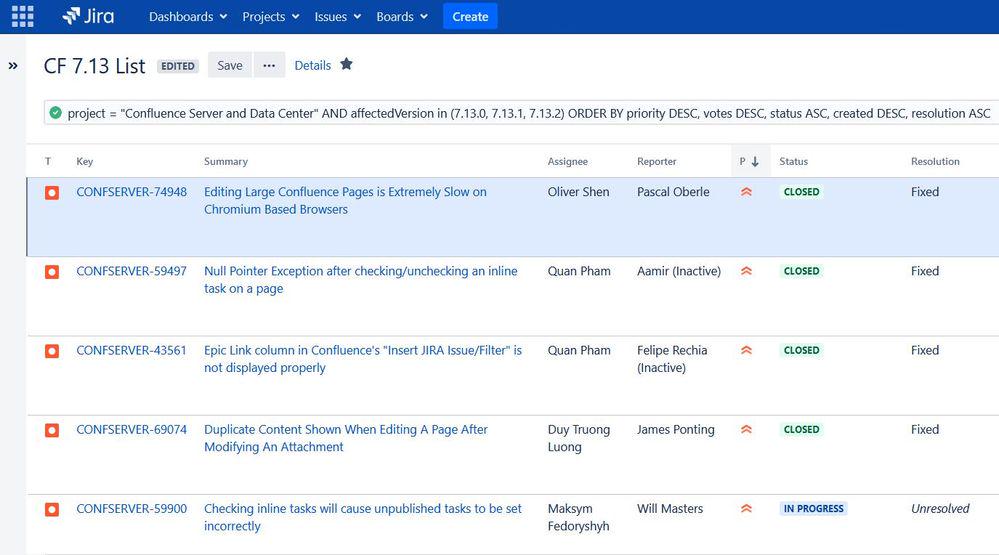

NVIC(Nested Vectored Interrupt Controller) 中的中断优先级配置

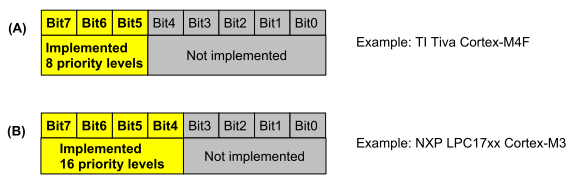

The number of priority levels in the Arm Cortex-M core is configurable, meaning that various silicon vendors can implement different number of priority bits in their chips. However, there is a minimum number of interrupt priority bits that need to be implemented, which is 2 bits in Arm Cortex-M0/M0+ and 3 bits in Arm Cortex-M3/M4.

Cortex-M 内核的中断优先级数量不全是固定的, Cortex-M0/M0+ 是固定的2-bit, Cortex-M3/M4 至少需要3-bit, 各个厂商可以在芯片产品里根据需要实现不同的优先级位数.

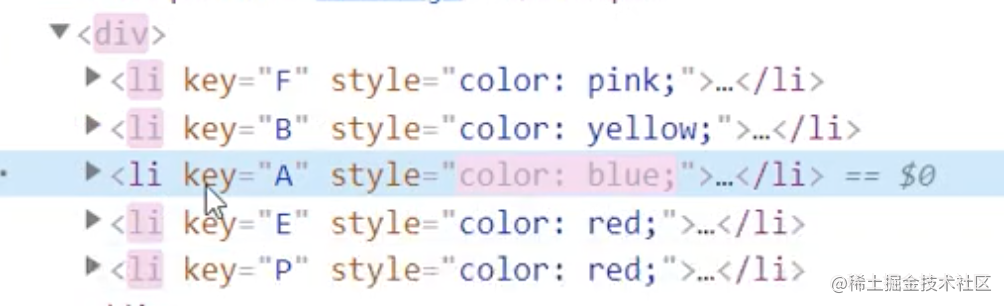

上图是 NVIC 优先级寄存器中的位表示方法. 优先级的有效数值是左对齐的, 如果直接往寄存器写值, 需要对应地左移.

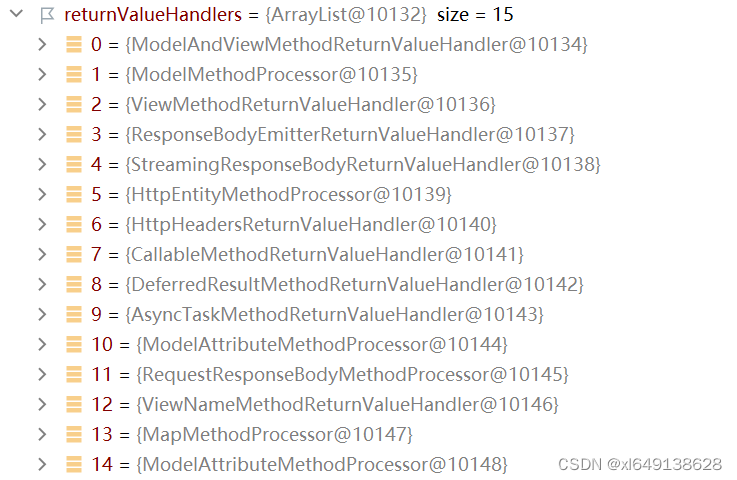

CMSIS 中的中断优先级

CMSIS(Cortex Microcontroller Software Interface Standard) 是面向 Cortex M 的通用底层实现, 在标准的 CMSIS 实现中提供了函数 NVIC_SetPriority(IRQn, priority) 用于设置中断优先级. 这个函数中的 priority 不需要左移, 在函数里已经根据 __NVIC_PRIO_BITS 自动处理了. 例如 调用 NVIC_SetPriority(7, 6) 对于 3-bit 优先级的 Cortex-M, 会将 IRQ#7 的优先级设为 1100,0000, 对于4-bit 优先级的 Cortex-M, 会将 IRQ#7 的优先级设为 0110,0000.

抢占优先级 Preempt Priority 和 子优先级 Supbpriority

优先级被分成两类

- Preemption Priorities, 抢占优先级

- Sub Priorities, 子优先级

这两种优先级的区别

- 更高的抢占优先级中断 可以打断 正在进行的低抢占优先级中断

- 抢占优先级相同的中断, 高子优先级 不可以打断 低子优先级的中断

- 抢占优先级相同的中断, 中断同时发生时, 子优先级高的先执行

- 抢占优先级和子优先级都一样时, 哪个中断先发生哪个就先执行

在大多数应用中, 建议将所有优先级bits分配给preempt priority group, 不使用 Supbpriority. 避免使中断优先级之间的关系复杂化. 一些第三方代码库(例如STM32的驱动库)会将优先级组配置为非标准, 建议在初始化此类驱动库后, 通过调用CMSIS函数 NVIC_SetPriorityGrouping(0U) 显式地将优先级分组重新设置为默认值.

使用库函数void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup)设置优先级组, 参数是以下宏定义

#define NVIC_PriorityGroup_0 ((uint32_t)0x700)

#define NVIC_PriorityGroup_1 ((uint32_t)0x600)

#define NVIC_PriorityGroup_2 ((uint32_t)0x500)

#define NVIC_PriorityGroup_3 ((uint32_t)0x400)

#define NVIC_PriorityGroup_4 ((uint32_t)0x300)

下面的表格是宏定义对应的抢占优先级和子优先级的拆分关系, 以及拆分后的优先级取值范围

| NVIC_PriorityGroup | NVIC_ IRQChannelPreemptionPriority | NVIC_ IRQChannelSubPriority | Description |

|---|---|---|---|

| NVIC_PriorityGroup_0 | 0 | 0-15 | 0 bits for pre-emption priority 4 bits for subpriority |

| NVIC_PriorityGroup_1 | 0-1 | 0-7 | 1 bits for pre-emption priority 3 bits for subpriority |

| NVIC_PriorityGroup_2 | 0-3 | 0-3 | 2 bits for pre-emption priority 2 bits for subpriority |

| NVIC_PriorityGroup_3 | 0-7 | 0-1 | 3 bits for pre-emption priority 1 bits for subpriority |

| NVIC_PriorityGroup_4 | 0-15 | 0 | 4 bits for pre-emption priority 0 bits for subpriority |

中断优先级由抢占优先级和子优先级共同组成, NVIC_InitStruct->NVIC_IRQChannelPreemptionPriority表示抢占优先级, NVIC_InitStruct->NVIC_IRQChannelSubPriority表示子优先级

系统运行后先调用函数void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup)设置中断优先级分组

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);

整个系统执行过程中,只设置一次中断分组.

针对每个中断,void NVIC_Init(NVIC_InitTypeDef* NVIC_InitStruct)设置对应的抢占优先级和响应优先级

NVIC_InitTypeDef NVIC_InitStruct;

NVIC_InitStruct.NVIC_IRQChannel = TIM2_IRQn;

NVIC_InitStruct.NVIC_IRQChannelCmd = ENABLE;

NVIC_InitStruct.NVIC_IRQChannelPreemptionPriority = 1;

NVIC_InitStruct.NVIC_IRQChannelSubPriority = 1;

NVIC_Init(&NVIC_InitStruct);

FreeRTOS优先级设置

对于 STM32F103, FreeRTOSConfig.h 中需要配置 configKERNEL_INTERRUPT_PRIORITY 和 configMAX_SYSCALL_INTERRUPT_PRIORITY, 另外在 FreeRTOS 调度启动前调用函数NVIC_PriorityGroupConfig( NVIC_PriorityGroup_4 )将全部优先级设为抢占优先级.

configKERNEL_INTERRUPT_PRIORITY

- 设置 FreeRTOS 内核本身使用的中断优先级, 因为FreeRTOS内核中断不应当抢占用户使用的中断, 因此一般定义为硬件最低优先级

- 对于STM32F103, 优先级总共4-bit, 在字节的最高位, bit[7:4], 全一表示的最低优先级, 所以在 FreeRTOSConfig.h 中将其设置为 0B1111xxxx 的任一个值就行 [240, 255]

- 对于AIR32F103, 优先级总共3-bit, 字节最高位 bit[7:5], 所以设置为 0B111xxxxx 的任一个值就行 [160, 255]

configMAX_SYSCALL_INTERRUPT_PRIORITY

设置可以在中断服务程序中, 调用中断安全的FreeRTOS API函数的最高中断优先级.

FreeRTOS 中断嵌套方案将可用的中断优先级分成2组: 被 FreeRTOS 临界区覆盖的, 和不会被覆盖的(这些中断是无法被屏蔽的), 优先级高于配置值的中断, 不受FreeRTOS管控, 在 FreeRTOS 中无法通过进入临界区屏蔽这些中断, 因此也不能在这些中断中调用 FreeRTOS API, 否则系统会有崩溃的风险

例如将这个优先级设置为5, 那么如果有一个中断优先级等于4, 在这个中断中调用了FreeRTOS API, 则系统会有崩溃的风险, 如果使能了configASSERT宏, 会触发断言失败.

在STM32中要保证所有的优先级设置为可抢占优先级, 具体实现方式是在 FreeRTOS 启动前, 调用函数NVIC_PriorityGroupConfig( NVIC_PriorityGroup_4)

STM32使用了中断优先级寄存器中的4位, bit[7:4], 如果设置优先级为5, 对应的二进制值为0x101,

- 对应STM32使用的 bit[7:4] 就是

0x0101, 剩余的 bit[3:0] 可以设置成任何值, 但为了兼容,最好将他们设置成1. 因此就是0x0101 1111 = 0x5F = 95 - 对应AIR32/MH32使用的是 bit[7:5] 就是

0x101, 剩余的 bit[4:0] 可以设置成任何值, 设成全1就是0x1011 1111 = 0xBF = 191

/* AIR32F103 only use 3 bits(bit[7:5]) for priority */

/* This is the raw value as per the Cortex-M3 NVIC. Values can be 255

(lowest) to 0 (1?) (highest). */

/* equivalent to 0xFF (0x111x xxxx, x=1), or priority 7. */

#define configKERNEL_INTERRUPT_PRIORITY 255

/* !!!! configMAX_SYSCALL_INTERRUPT_PRIORITY must not be set to zero !!!!

See http://www.FreeRTOS.org/RTOS-Cortex-M3-M4.html. */

/* equivalent to 0xBF (0x101x xxxx, x=1), or priority 5. */

#define configMAX_SYSCALL_INTERRUPT_PRIORITY 191

链接

- FreeRTOS的中断说明 http://www.openrtos.net/RTOS-Cortex-M3-M4.html

- Cutting Through the Confusion with Arm Cortex-M Interrupt Priorities

- A Beginner’s Guide on Interrupt Latency - and Interrupt Latency of the Arm Cortex-M processors