SGMII接口到底能不能直接出光模块?先说结论:我认为可以,但是有限制,此时的光口只支持强制模式,不支持自协商。如果对端是1000base-X接口,对端也需要把自协商关闭才能与SGMII直出的光口建立连接。

为什么SGMII明明是媒体独立接口,也就是MAC和PHY之间的接口,为什么又能直接出光模块,直接和传输媒体打交道呢?

下面分析原因。

我们先来梳理一下串行接口的主要技术的由来。首先,诸如GMII或者RGMII等并行口数据线较多,占用PCB面积和引脚多,同时不同走线之间的skew和串扰会影响数据速率的进一步提升,于是人们想办法将并行信号转换成串行信号发送,这就可以大大减少引脚数量,且需要使用差分信号来增加抗共模干扰的能力,同时为了收发端不同电平的对接,通常使用交流耦合,使用了交流耦合就需要保证信号的直流平衡,于是就有8B/10B、64B/66B、scramble等技术的引入,同时通过编码技术,还可以进行接收端CDR时钟恢复,进一步减少时钟引脚和时钟与数据之间的skew。有了这些技术之后,就具备了从GMII到SGMII的演进能力。

xGMII是IEEE定的标准,SGMII是思科定的标准(1999年10月出的第一版规范),本质上来说,SGMII就是将1000base-X(802.3zclause36 1998年出的规范)的PCS层(8B/10B编码,码组对齐同步和1000base-X物理层pcs编码一样,但自协商功能有差异)和PMA层(串并转换,时钟恢复,早期定义的SGMII规范没有CDR)拿过来用。

先来看一下SGMII的由来和框架。

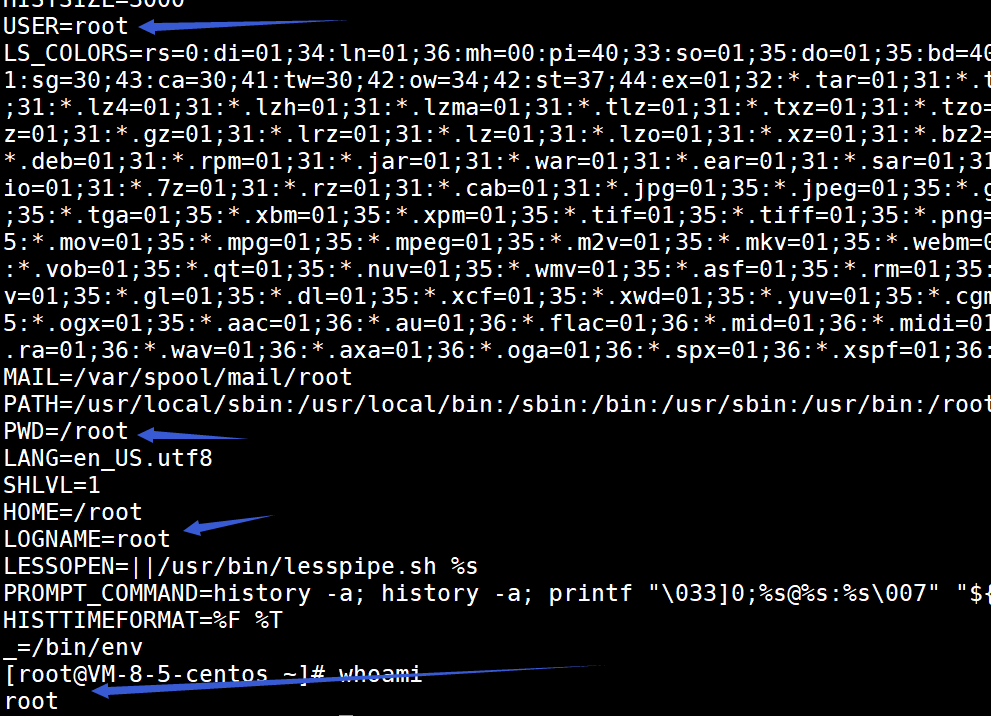

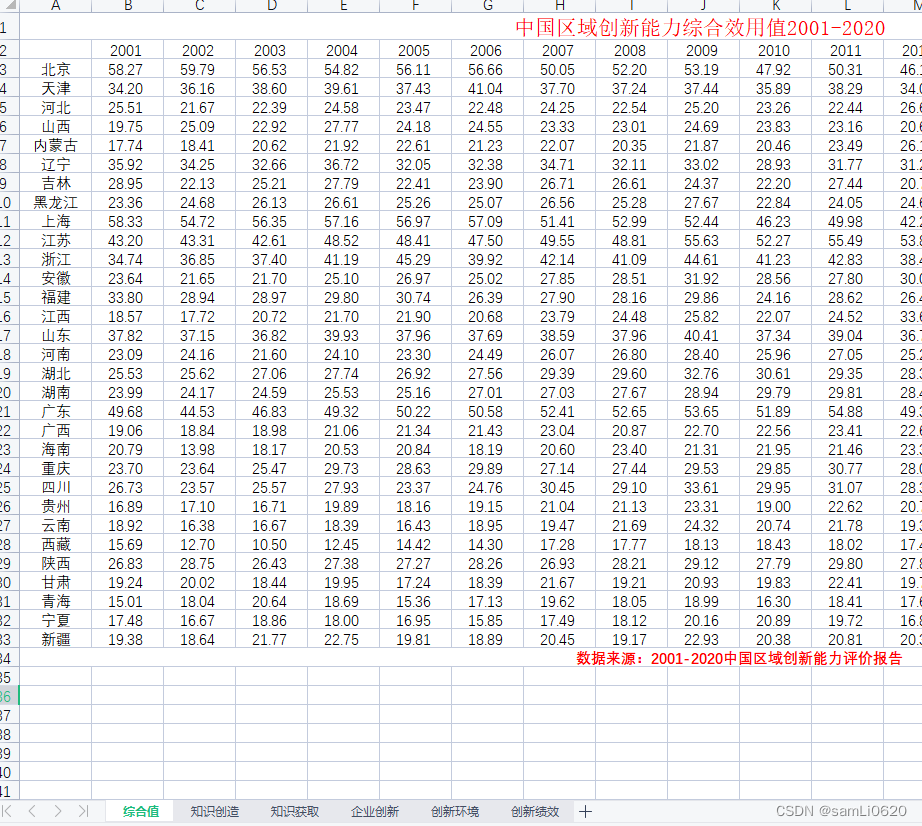

如下是MAC和PHY通过SGMII对接的框架图。可以看到发送和接收数据通道直接拿了802.3z的PCS层,PCS层的两边都是传统的GMII接口信号,8位数据TXD/RXD[7:0]和数据有效信号(TX_EN、RX_DV)、数据错误信号(TX_ER、RX_ER)经过编吗解码、串行解串,在625M的DDR时钟作用下,通过一对差分对传输。初始架构还没有CDR,所以还保留了随路时钟。可以看到,MAC端从RX_DV信号得到载波侦听CRS信号,从TX_EN和RX_DV的逻辑与得到冲突检测COL信号。

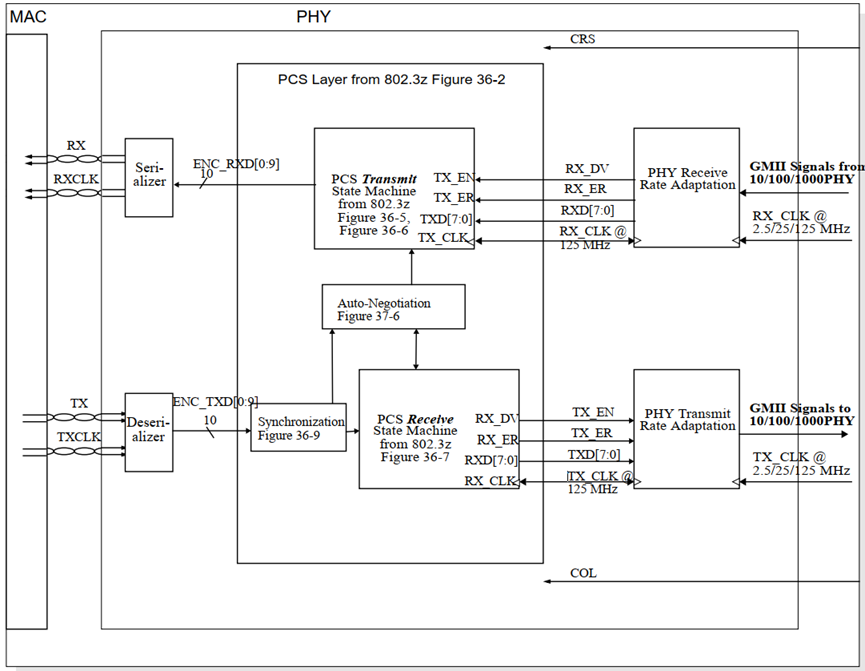

了解了SGMII两端的整体框架,再来细看SGMII与PHY芯片的连接细节:

接收侧,收到PHY芯片下游(如果是1000base-X,则有PCS+PMA+PMD,如果是1000base-T则有PCS+PMA)的GMII信号,速率可能是10、100、1000M,时钟速率2.5、25、125M,经过rate adaptation,将所有GMII接口速率数据都用125M时钟发给SGMII在PHY中的PCS模块,然后经过8B/10B编码将10位并行数据给到串行器转成串行数据,在625M时钟的作用下发给MAC。

发送侧,MAC将串行数据发给SGMII PHY,先经过解串器解出并行数据,然后经过同步模块将数据对齐,剩下的部分和接收侧相反,不再赘述。

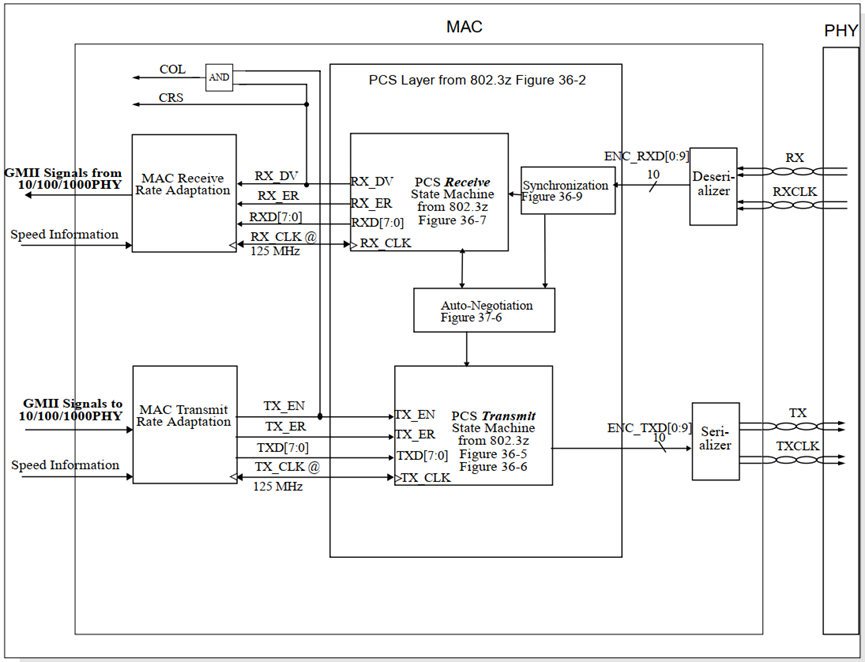

继续看MAC侧的连接细节:

结构基本和PHY侧类似,只是经过这里的PCS再往上就是GMII和RS子层对接,再往上才是真正的MAC,附上一张802.3定义的1000base-X的框架图有助理解,可以看到两个规范里的pcs层内容确实是一样的:

了解的框架之后我们再看为什么SGMII和1000base-X为什么不能自协商对接。

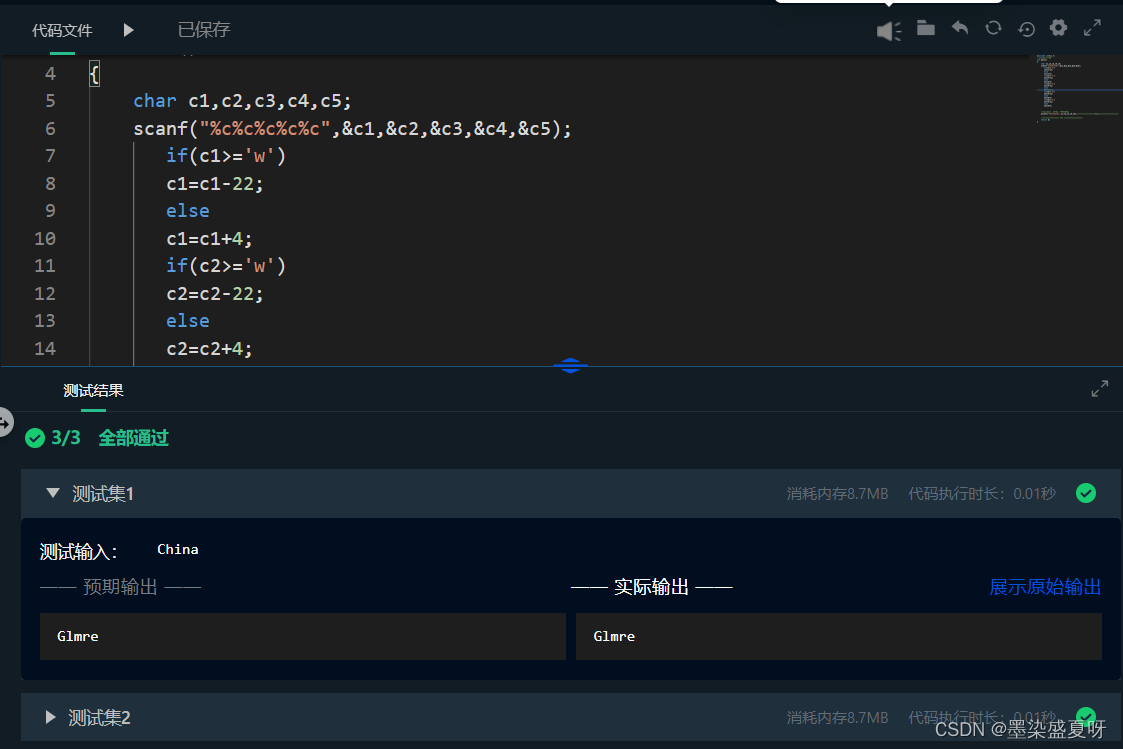

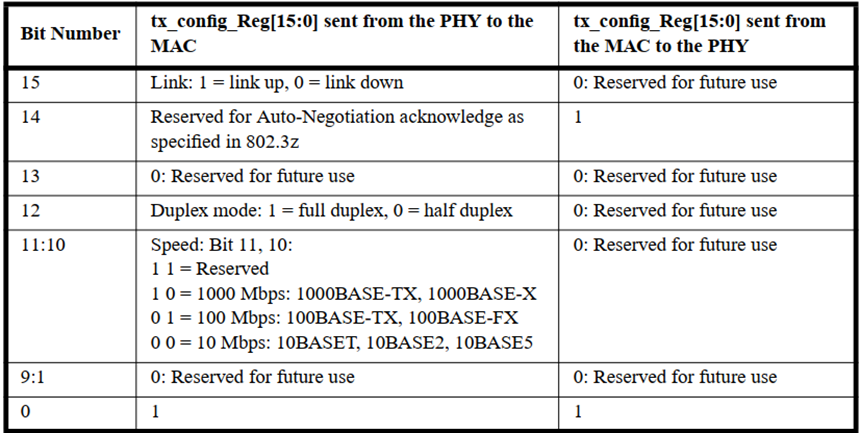

从第一张SGMII框图可以看到SGMII是支持MAC和PHY之间的自协商的,直接沿用802.3zclause 37 1000base-x的协商规范,但是发送的配置信息是不一样的,如下表所示为SGMII PHY和MAC之间传输的协商配置信息,可以看到定义的主要PHY发给MAC的信息,很好理解,IEEE规范里,自协商是PHY芯片完成的功能,PHY芯片要将自己的能力或者和对端PHY的协商结果告诉MAC,而MAC没必要再将自己的能力告诉PHY,只要协商成功给ACK就行,所以MAC发给PHY的配置信息是预留的。

配置信息包括:link状态、ACK、双工能力、速率能力。

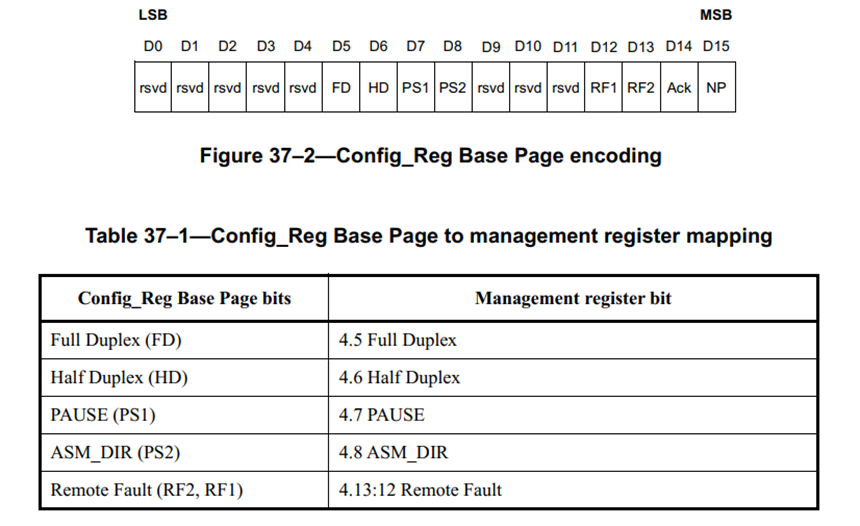

而1000base-x的发送的协商配置信息则有不同,如下图:

所以两个使能了自协商的SGMII和1000base-x接口对接,是无法协商成功建立连接的。要想对接,需要将二者的自协商功能关闭,两边同时发送idle码流,这时理论上可以建立连接。

同时需要注意的是,SGMII的接口速率1.25Gbaud是固定的,并不会因为物理层端口协商成10M、100M而降速,当协商为10M时,MAC芯片内,PCS层之前,会将每个帧复制100次来拉长帧,填满这1.25Gbaud的速率,同样,当协商为100M时,将每帧复制10次。

估计读者又会问了,什么是IDLE码流?这就得从8B/10B编码说起。

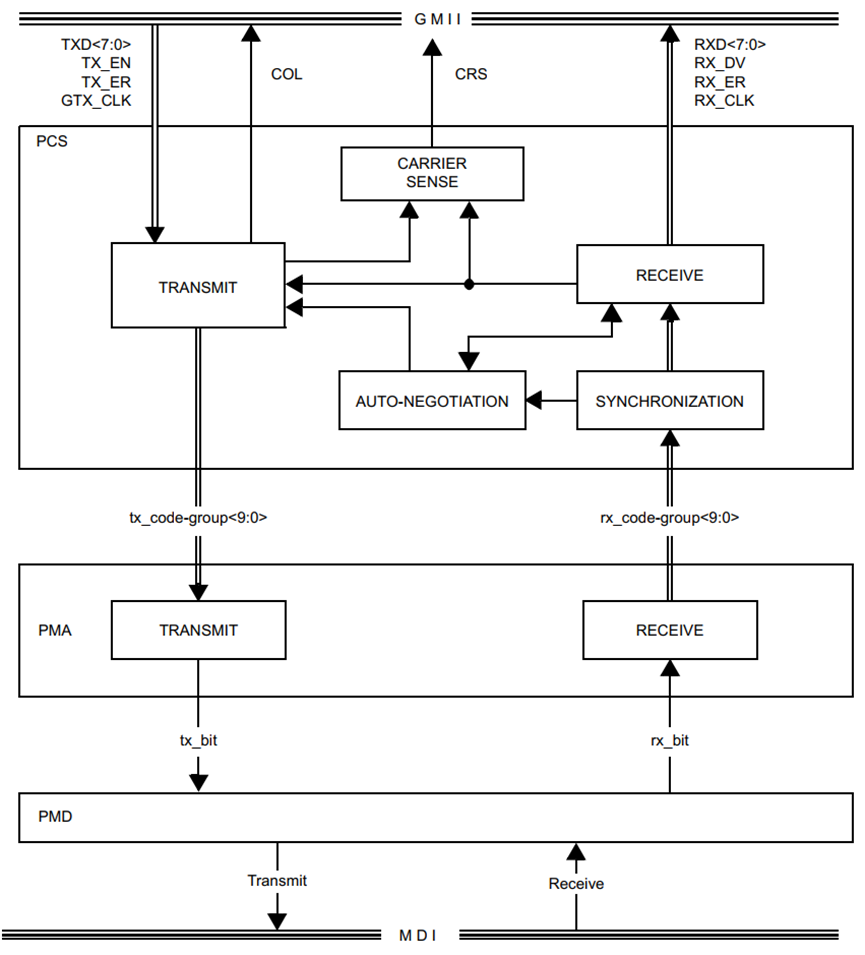

下面我们来回顾一下1000base-X的8B/10B编码,相关详细内容在802.3 clause 36。

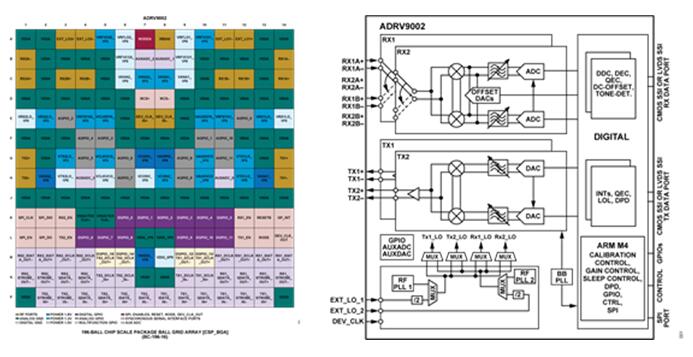

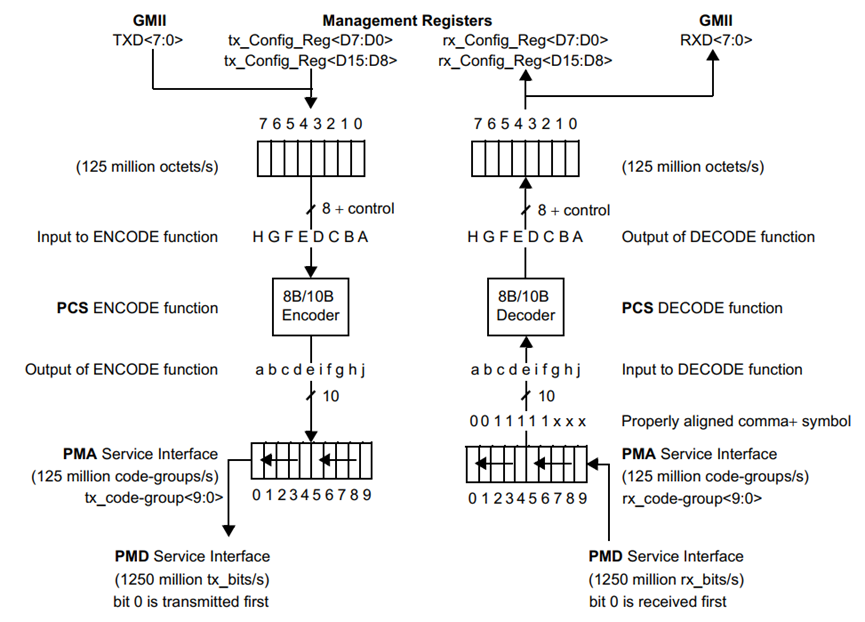

如上图,发送方向将GMII数据TXD[7:0]和配置寄存器tx_config_reg[15:0],通过8B/10B编码,然后经PMA完成并串转换,从PMD发送出去。接收方向,PMA完成串并转换和码组对齐后,发给PCS进行8B/10B解码,解出GMII数据RXD[7:0]和配置寄存器rx_config_reg[15:0]。

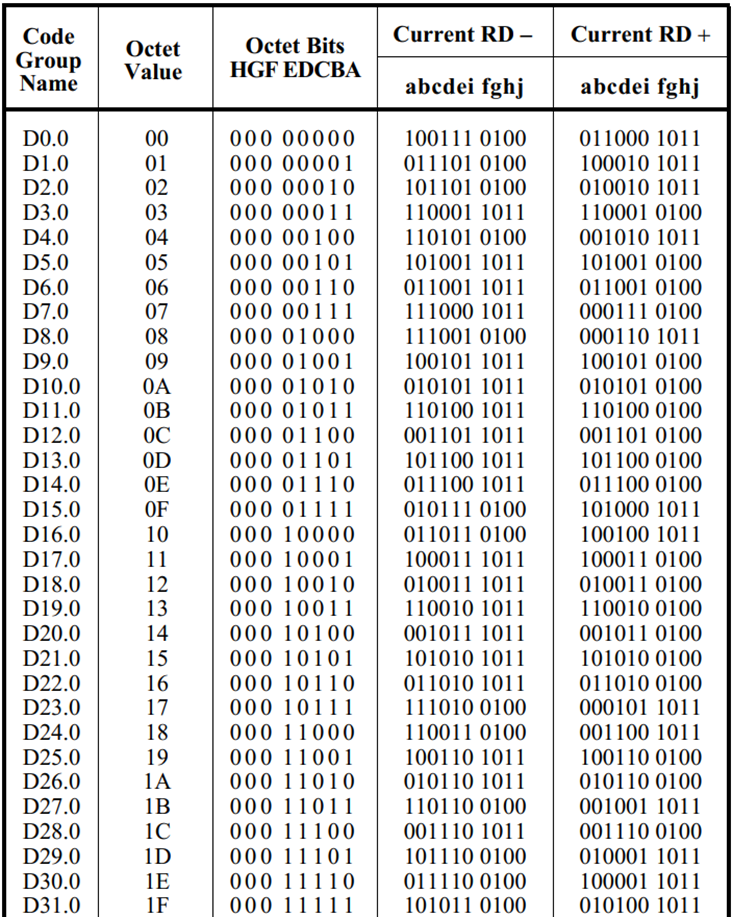

未编码的数据或控制字符为A、B、C、D、E、F、G、H,编码完后为A、B、C、D、E、i、F、G、H、j表示,用/Dx.y/表示256个有效数据代码组,/Kx.y/表示特殊控制代码组,其中其中x是位EDCBA的十进制值,y是位HGF的十进制值。所有代码组的定义见802.3表36–1和表36-2。

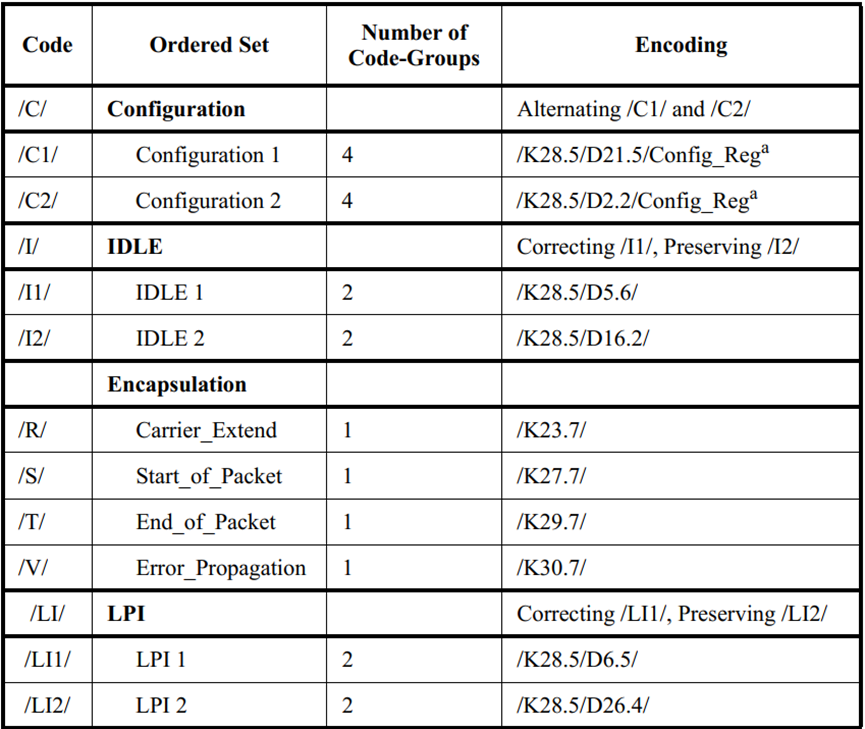

1000base-x的8B/10B编码后定义了如下一些码组序列:

以上的码组序列就有IDLE码,下面对各个码组序列逐一介绍:

C码。当1000base-X使能自协商时,通过发送C码完成建链。规范定义码流的运行时极性初始为-,C1和C2交替发送,其中C1为头两个代码组K28.5+D21.5后的运行时极性与初始运行极性相反,C2为头两个代码组K28.5+D2.2后的运行时极性与初始运行极性相同,如果配置寄存器的值是固定的,要保证发送序列C1/C2后的运行时极性与初始阴性极性相反,也就是要选择含comma+的K28.5。

I码。当GMII的TX_EN和TX_ER均无效时,PCS层将发送I码,用来建立和维持时钟同步。I码由一个或多个连续传输的I1或I2序列组成。其中I1 序列被定义为在传输/I1/结束时的运行时极性与开始的运行极性相反,I2 序列被定义为在传输/I2/结束时的运行时极性与开始的运行极性相同。D码流或C码流之后的第一个I码应将当前正或负运行极性恢复为负值,所有后续/I/均为/I2/,以确保负的结束时运行极性。不同的载波事件由/I/码分隔。

LI码。当GMII指示了使能LPI时,pcs将连续重复发送LI码,相当于LPI低功耗接口模式下的idle码。

可以观察到,C码、I码、LI码都是以/K28.5/代码组为开头,通常链路建立连接过程是通过C码或者I码,/K28.5/的作用是为了使接收机能对输入的码流进行对齐同步,同时/K28.5/可以用来区分序列码order set的边界。

另外,K28.1、K28.5、K28.7这三个特殊码组的前7位是相同的,这前7位被称为comma码,0011111为comma+,1100000为comma-,comma码的作用就是用来码组对齐。

封装部分:

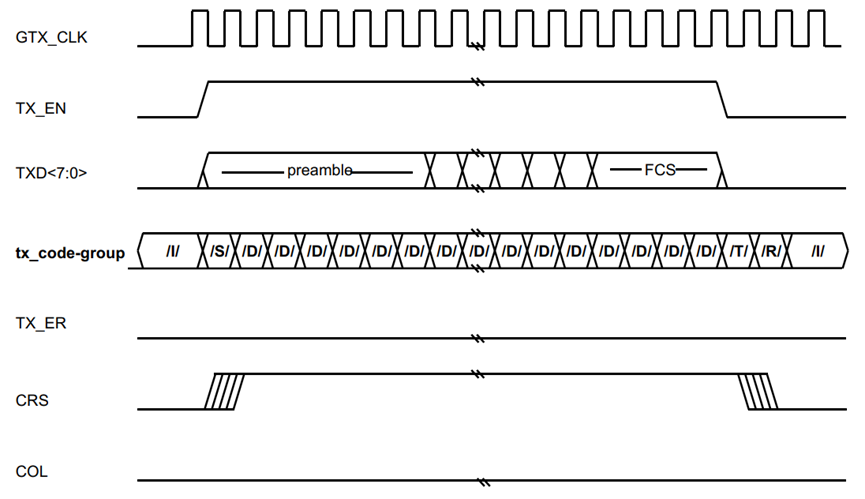

SPD。Start of packet定界符,是数据传输序列码流的起始边界。当GMII的TX_EN使能,且在当前PCS的order set传输完成之后,PCS将用SPD替换MAC前导码的当前八位,在接收端PCS又会用和MAC前导码相关的8位数据替换SPD定界符。对于单个数据包或突发中的第一个数据包,SPD跟随/I/。对于突发的第二个和后续分组,SPD跟随/R/。

EPD。End of packet定界符,顾名思义,就是数据序列的结束边界。PCS将在GMII的TX_EN撤销,并在MAC帧结构最后的FCS校验数据之后发送EPD定界符。EPD的构成遵循如下规则:

a、PCS在MAC数据帧最后一个字节之后发送/T/R/。

b、如果MAC有载波扩展给到PCS,则载波扩展规则生效。

C、如果MAC没有载波扩展给到PCS,则遵循如下规则:

1、如果/R/是在偶数代码组位置发送的,则PCS向代码组流附加一个单独的附加/R/,以确保后续/I/与偶数代码组边界对齐,并且EPD传输完成;

2、PCS传输I码。

R码,载波扩展序列。R码有如下3个用途:

1、载波扩展是MAC用于延长载波事件的持续时间的方法。当用于此目的时,载波扩展由MAC发出并由MAC解释,并由PCS对相应的代码组进行编码和解码。为了扩展载波,GMII必须撤销TX_EN。TX_EN变为无效的同时,TX_ER有效时,触发PCS发出具有两个8bit延迟的/R/,这使PCS有时间在开始传输之前完成其EPD。PCS发射的/R/码组的数量等于其扩展载波的GMII GTX_CLK周期的数量(通俗就是就是PCS层用R码来表示MAC帧中的载波扩展数据)。

2、数据包分离:MAC使用载波扩展来分离数据包突发中的数据包。当用于此目的时,载波扩展从MAC发出并由MAC解释,并由PCS编码到相应的代码组并从中解码;

3、EPD2。End_of_Packet定界符/T/R/I/或/T/R/R/I/中/T/之后的第一个/R/。

4、EPD3。End_of_Packet定界符/T/R/R/I/中/T/之后的第二个/R/。如果需要,这个/R/用于填充数据包突发中的唯一或最后一个数据包,以便后续/I/在偶数代码组边界上对齐。

V码。Error_Propagation是向对端发送的发送错误指示,即PCS将从GMII收到的TX_ER信息,通过V码发送出去。

如下图为GMII到PCS封装成比特码流的示意:

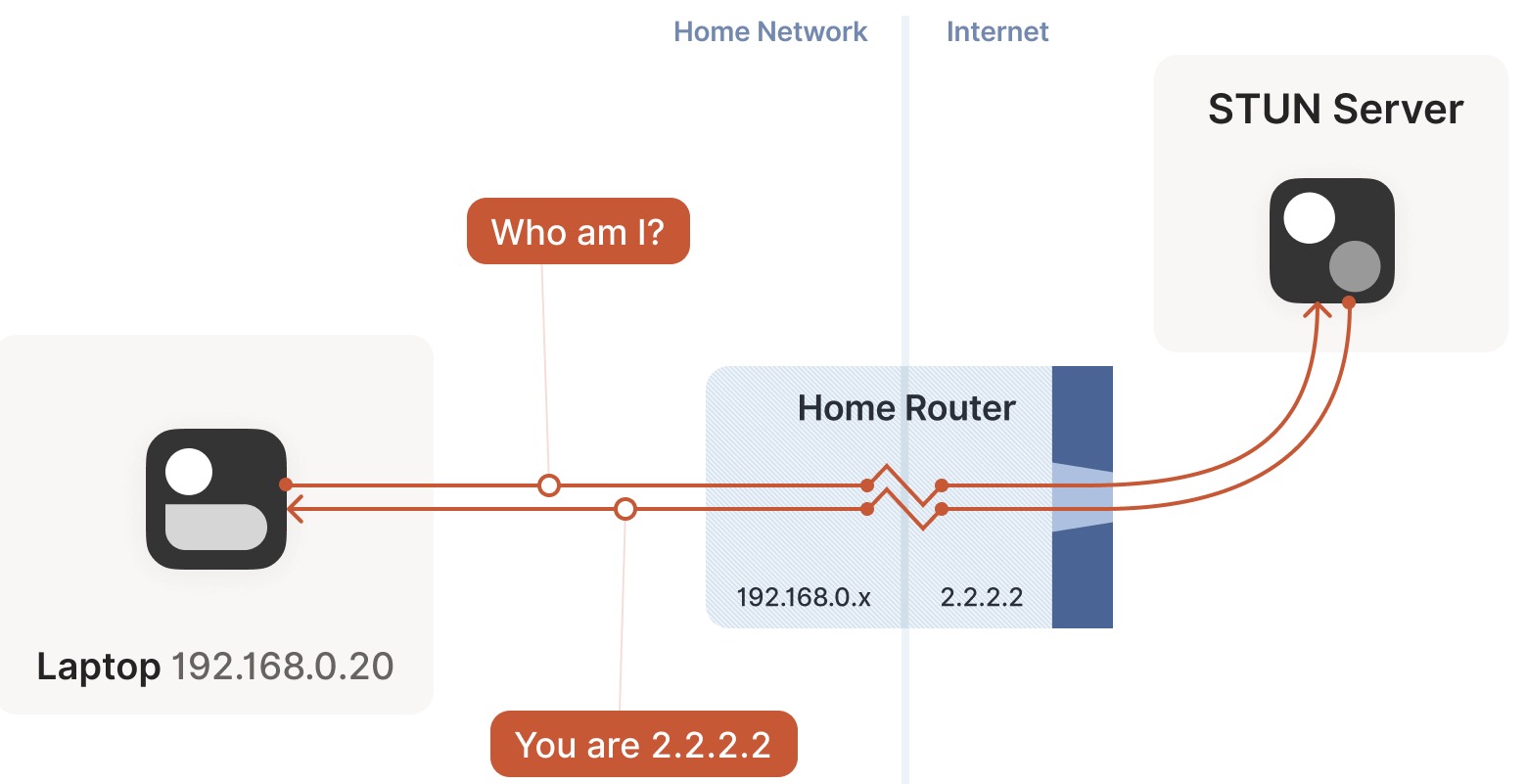

看到这里大家应该能明白了,当SGMII与1000base-X对接时,两边都关闭自协商,用强制千兆全双工,两边在相同的PCS作用下发送I码,此时可以通过I码实现同步,建立连接。如果两边都使能自协商,两边的C码流内容不一样,无法建立连接。