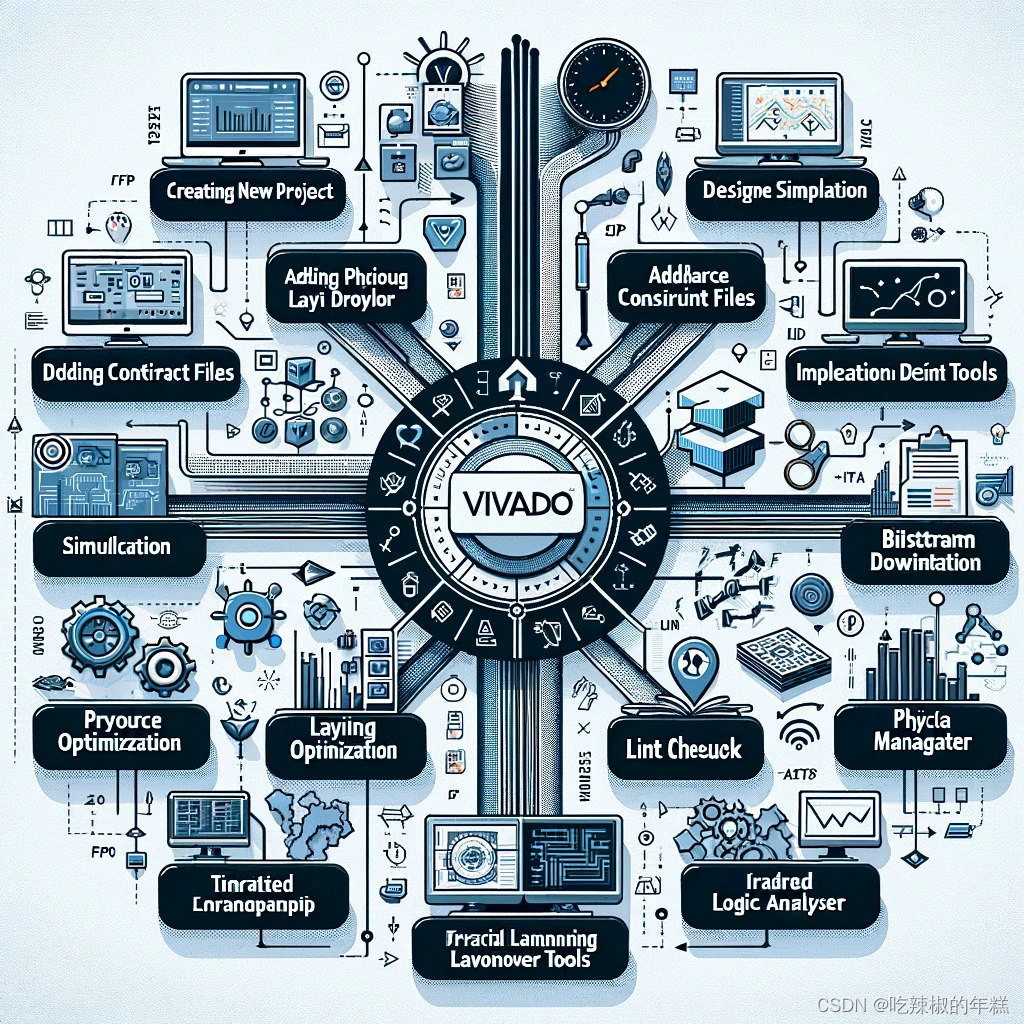

Vivado 是 Xilinx 公司推出的一款用于 FPGA 设计的集成开发环境 (IDE),提供了从设计输入到实现、验证、调试和下载的完整流程。本文将详细介绍 Vivado 的使用方法,包括项目创建、设计输入、约束文件、综合与实现、仿真、调试、下载配置等步骤。

一、创建新项目

1.1 启动 Vivado

打开 Vivado 应用程序,进入欢迎界面。

1.2 创建新项目

- 在欢迎界面选择“Create New Project”。

- 输入项目名称和路径。

- 选择“RTL Project”,并勾选“Do not specify sources at this time”。

- 选择目标器件(如 XC7Z020-1CLG484)。

- 点击“Finish”完成项目创建。

二、设计输入

2.1 添加设计源文件

- 在 Flow Navigator 面板中,选择“Add Sources”。

- 选择“Add or Create Design Sources”并点击“Next”。

- 点击“Create File”以创建新的 Verilog 或 VHDL 文件。

- 输入文件名并选择文件类型(Verilog/VHDL)。

- 点击“Finish”完成文件创建。

2.2 编辑设计源文件

- 在 Sources 面板中,双击新创建的源文件以打开编辑器。

- 编写设计代码。例如,以下是一个简单的 Verilog 模块:

module led_blink (

input wire clk,

input wire rst,

output reg led

);

reg [23:0] counter;

always @(posedge clk or posedge rst) begin

if (rst) begin

counter <= 24'd0;

led <= 1'b0;

end else begin

counter <= counter + 1;

if (counter == 24'd9999999) begin

counter <= 24'd0;

led <= ~led;

end

end

end

endmodule

三、添加约束文件

3.1 添加约束文件

- 在 Flow Navigator 面板中,选择“Add Constraints”。

- 选择“Create File”并命名文件(如“constraints.xdc”)。

- 点击“Finish”完成文件创建。

- 在 Sources 面板中,双击新创建的约束文件以打开编辑器。

- 添加引脚约束。例如:

set_property PACKAGE_PIN W5 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property PACKAGE_PIN U16 [get_ports rst]

set_property IOSTANDARD LVCMOS33 [get_ports rst]

set_property PACKAGE_PIN V17 [get_ports led]

set_property IOSTANDARD LVCMOS33 [get_ports led]

3.2 约束文件细节

引脚约束:指定 FPGA 器件的引脚连接。

时序约束:定义时钟周期、输入和输出延迟、时钟偏移等时序要求。例如:

create_clock -period 10.000 -name clk [get_ports clk]

set_input_delay -max 5.000 -clock clk [get_ports rst]

set_output_delay -max 5.000 -clock clk [get_ports led]

布线约束:定义特定信号的布线要求,避免电源噪声和串扰。例如:

set_property PULLUP true [get_ports rst]

set_property DRIVE 12 [get_ports led]

3.3 约束文件的优化

- 确保时序约束的准确性,避免过于宽松或严格。

- 针对关键路径设置合理的时序约束,保证时序收敛。

- 使用分层约束文件,便于管理和维护。

四、综合与实现

4.1 运行综合(Synthesis)

- 在 Flow Navigator 面板中,选择“Run Synthesis”。

- Vivado 将开始综合设计。完成后,查看综合报告以确认无错误。

4.2 查看综合报告

- 在 Flow Navigator 面板中,选择“Open Synthesized Design”。

- 打开“Reports”选项卡,查看综合报告中的时序、资源利用情况等信息。

时序报告:检查所有路径是否满足时序要求。

资源利用报告:查看逻辑单元、寄存器、内存块、DSP 等资源的使用情况。

4.3 运行实现(Implementation)

- 在 Flow Navigator 面板中,选择“Run Implementation”。

- Vivado 将开始实现设计。完成后,查看实现报告以确认无错误。

4.4 查看实现报告

- 在 Flow Navigator 面板中,选择“Open Implemented Design”。

- 打开“Reports”选项卡,查看实现报告中的布线、时序等信息。

布线报告:检查布线是否合理,是否存在长路径或高拥堵区域。

时序报告:再次检查时序收敛情况,确保所有路径满足时序要求。

4.5 优化布线

- 调整约束:检查和优化约束文件,确保时序约束和布线约束合理。

- 重复综合和实现:多次运行综合和实现过程,逐步优化设计。

- 使用物理布局工具:在 Vivado 中使用物理布局工具查看和调整关键路径的布线。

4.6 布局和资源优化示例

资源优化示例

假设我们有一个简单的计数器设计:

module counter(

input wire clk,

input wire rst,

output reg [3:0] count

);

always @(posedge clk or posedge rst) begin

if (rst)

count <= 4'b0000;

else

count <= count + 1;

end

endmodule

资源利用报告:

- 在综合完成后,查看综合报告中的“Utilization Report”,检查 LUT、FF、BRAM 和 DSP 的使用情况。

- 如果发现某些资源使用过多,可以尝试以下优化:

- 重写代码以减少不必要的逻辑。

- 使用更高效的数据结构(如将组合逻辑转换为查找表或存储器)。

布局优化示例

- 在综合和实现完成后,查看实现报告中的“Placement Report”和“Routing Report”。

- 检查是否有信号的延迟过长或拥堵区域。

- 使用 Vivado 的“Floorplanning”工具进行手动布局优化:

- 将相关模块放置在相邻区域内,减少布线长度。

- 确保关键信号的路径尽可能短,减少延迟。

- 示例:将计数器和 LED 驱动逻辑放置在相邻的逻辑块中。

五、仿真

5.1 添加仿真源文件

- 在 Flow Navigator 面板中,选择“Add Sources”。

- 选择“Add or Create Simulation Sources”并点击“Next”。

- 点击“Create File”以创建新的仿真文件(如“testbench.v”)。

- 输入文件名并选择文件类型(Verilog/VHDL)。

- 点击“Finish”完成文件创建。

5.2 编写测试平台

- 在 Sources 面板中,双击新创建的仿真文件以打开编辑器。

- 编写测试平台代码。例如:

module counter(

input wire clk,

input wire rst,

output reg [3:0] count

);

always @(posedge clk or posedge rst) begin

if (rst)

count <= 4'b0000;

else

count <= count + 1;

end

endmodule

5.3 运行仿真

- 在 Flow Navigator 面板中,选择“Run Simulation”。

- 选择“Run Behavioral Simulation”。

- 仿真完成后,查看波形窗口以验证设计行为。

5.4 波形查看和分析

- 在仿真过程中,可以使用 Vivado 仿真器查看波形图。

- 在波形窗口中,选择感兴趣的信号,点击“Add to Wave”以添加到波形视图中。

- 使用“Zoom In”和“Zoom Out”工具调整波形视图。

- 在波形视图中,检查信号的时序关系和逻辑行为,验证设计的正确性。

5.5 仿真报告

查看仿真日志,确认所有测试用例通过,并且没有错误和警告。

六、调试

6.1 设置调试探针

- 在设计源文件中插入 ILA (Integrated Logic Analyzer) 核。

- 例如,将以下代码添加到 Verilog 模块中:

ila_0 ila_inst (

.clk(clk),

.probe0(count)

);

6.2 配置调试核

- 在 Flow Navigator 面板中,选择“Open IP Integrator”。

- 在 IP Integrator 中添加 ILA 核,并将其连接到设计中相应的信号。

6.3 运行调试

- 在 Flow Navigator 面板中,选择“Run Implementation”。

- 生成比特流文件并下载到 FPGA。

- 打开硬件管理器,配置 ILA 并运行调试。

七、下载配置

7.1 下载比特流文件

- 连接 FPGA 开发板与计算机。

- 在 Flow Navigator 面板中,选择“Open Hardware Manager”。

- 选择“Open Target”,然后选择“Auto Connect”。

- 选择“Program Device”,并选择生成的比特流文件进行下载。

7.2 验证设计

- 确认 FPGA 已正确配置。

- 验证设计功能是否符合预期。

八、综合和实现的优化技巧

8.1 Lint 检查

Lint 检查用于在代码综合之前查找和修复代码中的潜在错误和不规范写法。

- 在 Flow Navigator 面板中,选择“Open Synthesized Design”。

- 选择“Report”->“Report DRC”进行设计规则检查。

- 选择“Report”->“Report CDC”进行时钟域交叉检查。

- 查看报告中的警告和错误信息,修改代码以修复这些问题。

8.2 时序优化

- 在综合和实现过程中,检查时序报告,确保所有路径满足时序要求。

- 使用多重约束(Multi-Constraint)文件,根据不同的工作条件设置不同的时序约束。

- 调整代码结构,优化关键路径,减少路径延迟。

8.3 资源优化

- 检查资源利用报告,确保设计在目标 FPGA 上的资源利用率合理。

- 使用高效的数据结构和算法,减少资源消耗。

- 使用分层设计,将复杂模块分解为多个子模块,提高设计的可维护性和可扩展性。

8.4 物理布局优化

- 在物理布局阶段,使用 Vivado 提供的布局工具,手动调整关键路径的布局。

- 确保关键信号布线尽量短,减少布线延迟。

- 使用区域约束(Area Constraints),将相关模块放置在相邻的区域内,减少信号延迟。

8.5 布局和资源优化示例

假设我们有一个简单的计数器设计:

module counter(

input wire clk,

input wire rst,

output reg [3:0] count

);

always @(posedge clk or posedge rst) begin

if (rst)

count <= 4'b0000;

else

count <= count + 1;

end

endmodule

资源优化示例:

- 在综合完成后,查看综合报告中的“Utilization Report”,检查 LUT、FF、BRAM 和 DSP 的使用情况。

- 如果发现某些资源使用过多,可以尝试以下优化:

- 重写代码以减少不必要的逻辑。

- 使用更高效的数据结构(如将组合逻辑转换为查找表或存储器)。

布局优化示例:

- 在综合和实现完成后,查看实现报告中的“Placement Report”和“Routing Report”。

- 检查是否有信号的延迟过长或拥堵区域。

- 使用 Vivado 的“Floorplanning”工具进行手动布局优化:

- 将相关模块放置在相邻区域内,减少布线长度。

- 确保关键信号的路径尽可能短,减少延迟。

- 示例:将计数器和 LED 驱动逻辑放置在相邻的逻辑块中。

九、实机条件下的调试

9.1 设置和配置调试核

- 在设计中添加 ILA 核,捕获实际工作条件下的信号。

- 配置 ILA 核,选择要捕获的信号和触发条件。例如:

ila_0 ila_inst (

.clk(clk),

.probe0(count)

);

9.2 运行实机调试

- 生成比特流文件并下载到 FPGA。

- 连接调试设备(如 JTAG 调试器)与 FPGA 开发板。

- 在 Vivado 中打开硬件管理器,选择“Open Hardware Manager”。

- 选择“Open Target”,然后选择“Auto Connect”。

- 在硬件管理器中配置 ILA,设置触发条件并捕获信号数据。

- 分析捕获到的波形数据,检查信号时序和逻辑行为。

9.3 调试步骤示例

- 在硬件管理器中,选择“Add Probes”添加需要监控的信号。

- 设置触发条件,例如设置计数器达到特定值时触发捕获。

- 开始捕获数据,运行 FPGA 设计,触发器触发时自动捕获信号。

- 分析波形图,检查信号是否按照预期工作。

- 根据需要调整设计,重新生成比特流文件,并再次下载和验证。

十、总结

Vivado 是一个功能强大的 FPGA 开发工具,提供了从设计输入到实现、验证、调试和下载的完整流程。本文详细介绍了 Vivado 的使用方法,包括项目创建、设计输入、约束文件、综合与实现、仿真、调试、下载配置、优化技巧等步骤。通过这些内容的学习和实践,可以有效提高 FPGA 设计的性能和可靠性。